Definition und Funktion von IC-Substraten

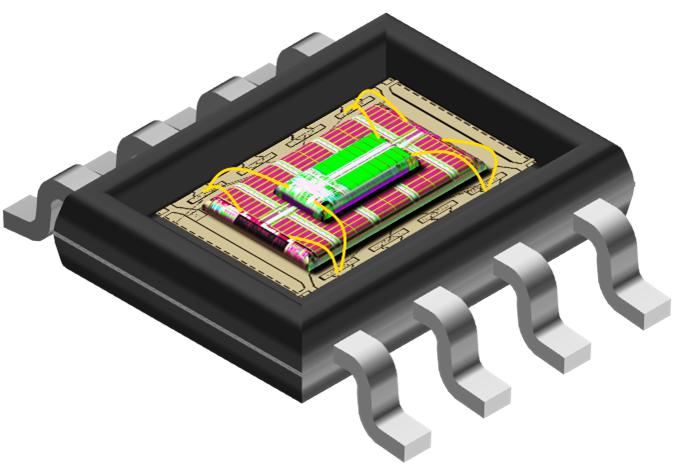

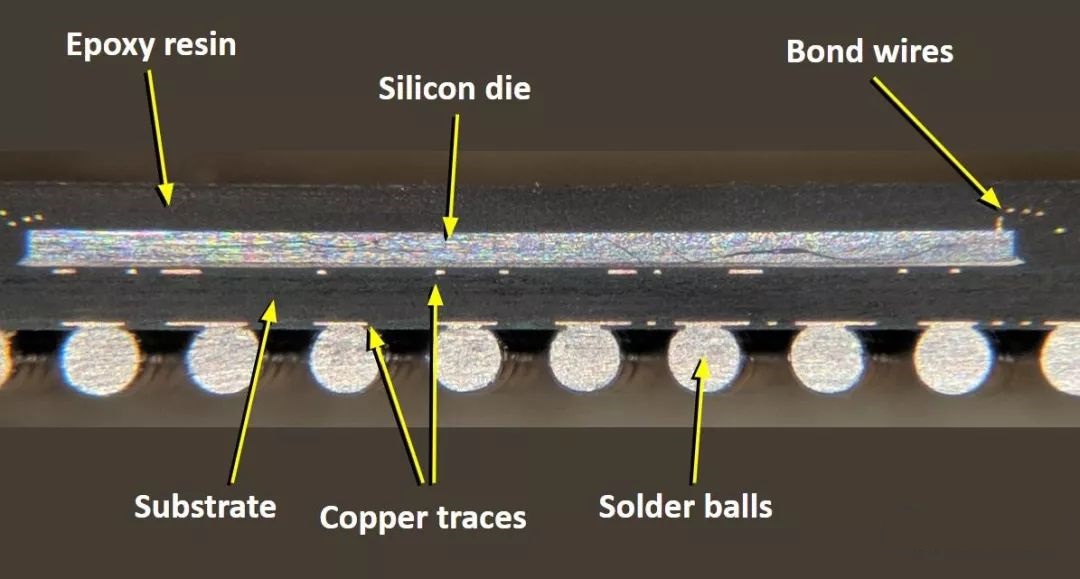

IC-SubstratDefinition: Eine Basisplatine zur Kapselung von nackten IC-Chips.

Funktion:

(1) Carrying semiconductor IC Chips.

(2) The internal circuit is arranged for the connection between the Chip and the circuit Brett.

(3) Protect, fix, Unterstützung IC chip, Wärmeableitungskanal, ist das Zwischenprodukt des Kommunikationschips und PCB.

IC-Verpackung

Geboren: Mitte der 1990er Jahre, weniger als zwanzig Jahre alt. Das Aufkommen neuer Verpackungen mit hoher Dichte im integrierten Schaltkreis (IC), wie BGA (Ball Grid Array Packaging) und CSP (Chip Size Packaging), hat zu einem notwendigen neuen Träger für die Verpackung von IC-Verpackungssubstraten geführt.

* Halbleiter development: valve - Transistor - Through Loch assembly - surface Packaging (SMT) - Chip level Packaging (CSP, BGA) - System Packaging (SIP)

* PCB und Halbleitertechnik sind voneinander abhängig, schließen, Penetration, enge Koordinierung, PCB kann eine Vielzahl von Chips erreichen, Komponenten zwischen elektrischer Isolierung und elektrischer Verbindung, Bereitstellung der erforderlichen elektrischen Eigenschaften.

Technische Parameter Anzahl der Schichten, 2,10 Schichten;

PCB Plattendicke, normalerweise 0.1 ~ 1.5mm;

Minimum PCB Brett thickness tolerance *0 micron;

Minimum aperture, durch Loch 0.1mm, Mikroloch 0.03mm;

* Minimum pattern width/Abstand, 10~80 microns;

Minimum ring width, 50 microns;

* Contour tolerance, 0~50 micron;

* Buried blind hole, Impedanz, buried resistance capacity;

* Surface coating, Ni/Au, WeichGold, Hartgold, Nickel/Palladium/gold, etc.

* Board size, â¤150*50mm (single IC carrier);

That is to say, DIE IC-Substrat erfordert mehr Feinheit, hohe Dichte, hohe Anzahl von Füßen, kleines Volumen, hole, Diskette, Linie kleiner, ultradünne Kernschicht. Daher, Es ist notwendig, eine präzise Zwischenlagenausrichtung zu haben, Musterbildgebungstechnologie, Galvanik, Bohrtechnik und Oberflächenbehandlungstechnik. Es wurden höhere Anforderungen an die Produktzuverlässigkeit gestellt, Ausrüstung und Instrumente, Material- und Produktionsmanagement. Daher, die technische Schwelle von IC-Substrat ist hoch und die Forschung und Entwicklung ist nicht einfach.

Technische Schwierigkeiten im Vergleich zu herkömmlichen PCB Herstellung, die zu überwindenden technischen Schwierigkeiten für IC-Substrat are as follows:

(1) core Brett production technology core Brett dünn, leicht zu verformen, Vor allem wenn die Dicke der Platte.2mm, mit Plattenstruktur, Plattenausdehnung und -schrumpfung, Laminarparameter, Zwischenschichtpositionierungssystem und andere Technologie muss einen Durchbruch machen, um die ultra-dünne Kernplatte Verzug und Pressdicke der effektiven Steuerung zu erreichen.

(2) Microporous technology

* Including: solder mask open process, Laserbohren Mikroblindlochverfahren, Kupferbeschichtung mit Blindloch.

* Conformalmask (Conformalmask) process is used to make reasonable compensation for laser blind hole window opening, und definieren Sie direkt die Öffnung und Position des blinden Lochs durch den geöffneten Kupferring.

* Indicators involved in laser drilling microhole: hole shape, oberes und unteres Blendenverhältnis, Seitenerosion, Glasfaser hervorstehend, Restkleber am Boden des Lochs, etc.

* Indicators involved in blind hole copper plating include: filling capacity, Hohlraum des toten Lochs, Durchhängen, Verlässlichkeit der Kupferbeschichtung, etc.

* At present, die Mikroporengröße ist 50~100 micron, und die Anzahl der geschichteten Poren erreicht 3, 4 und 5 Aufträge.

(3) Graphic formation and copper plating technology

Pattern compensation technology and control; Fine pattern production technology; Copper plating thickness uniformity control technology; Micro erosion control technology for fine pattern.

* The current pattern width spacing requirement is 20~50 microns. Copper plating thickness uniformity requirement is 18* micron, Ätzgleichförmigkeit â¥90%.

(4) welding resistance process * including plug hole process, Schweißwiderstandsdrucktechnologie, etc.

* The height difference between the solder resistance surface of the IC-Substrat ist weniger als 10 Mikrons, und der Höhenunterschied zwischen dem Lotwiderstand und der Pad-Oberfläche ist weniger als 15 Mikrons.

(5) Surface treatment technology

* Uniformity of thickness of Nickel/Vergoldung; Sowohl weiches als auch hartes Vergoldungsverfahren auf der gleichen Platte; Nickel/Palladium/Vergoldungsverfahren.

* Lineable surface coating, Technologie der selektiven Oberflächenbehandlung.

(6) Testing capability and product reliability testing technology

* Equipped with a number of testing equipment/Instrumente, die sich von den traditionellen unterscheiden PCB Fabrik.

* Master reliability testing techniques different from conventional ones.

(7) In general, die Produktion von IC-Substrat involving more than ten aspects of technology:

Graph dynamic compensation; Graphic electroplating process for thickness uniformity of copper plating; The whole process material expansion and shrinkage control; Surface treatment process, Selektive Galvanik aus weichem Gold und Hartgold, nickel/Palladium/gold plating process;

* Core plate wafer production;

* High reliability detection technology; Microporous processing;

* If stacked micro 3, 4, 5, production process;

* Multiple laminated pressure; Laminate â¥4 times; Drilling â¥5 times; Electroplating â¥5 times.

* Wire pattern formation and etching;

* High precision alignment system;

* Welding stopper hole process, Galvanisierungsverfahren zum Füllen von Mikrolochen;

IC-SubstratKlassifizierung

Durch die Form der Verkapselung

Verpackungstrend

(1) BGA

*BallGridAiry, BGA, Kugelförmiges Array-Paket.

* This kind of Paket of the Brett Wärmeableitung, elektrische Leistung ist gut, Chippin kann stark erhöht werden, applied to 300 pin number (pincount) above IC package.

(2) CSP

*CSP, Chipverpackung, Verpackung auf Chipebene.

* Is a single Chippaket, geringes Gewicht, klein, seine Packungsgröße und IC Größe selbst ist fast gleich oder etwas größer, Verwendung in Speicherprodukten, Kommunikationsprodukte, Pin Nummer ist nicht hoch elektronische Produkte.

(3) coated Kristall-Leiterplatte

* FlipChip (FC) is a type of package in which the front side of the chip is flipped (Flip) and the convex block is directly connected zum PCB.

Diese Art von Substrat hat die Vorteile der geringen Signalstörung, geringer Verlust der Anschlussschaltung, gute elektrische Leistung, effiziente Wärmeableitung und so weiter.

(4) Multi-chip module

* Multi-chip (MCM) module Multiple chips with different functions in the same package.

* This is the best solution for electronic products to light, thin, kurz, weniger als High-Speed Wireless. Verwendet in großen Computern oder elektronischen Produkten der besonderen Leistung.

* Because there are multiple chips in the same package, Signalstörungen, heat dissipation, dünne Linien, und so weiter, es gibt keine Komplettlösung mehr, das zur aktiven Entwicklung von Produkten gehört.

Nach Materialeigenschaften s

(1) Hard Leiterplatte. Abdichtung Beladung PCB

* Rigid organic Verpackungssubstrat made of epoxy, BT, ABF-Harz. Sein Ausgangswert ist die Mehrheit der IC packaging substrate. CTE (coefficient of thermal expansion) ranges from 13 to 17ppm/ Grad Celsius.

(2) Weiche Platte, die Leiterplatte versiegelt.

* The packaging substrate made of PI (polyimide), PE (polyester) resin flexible substrate, CTE beträgt 13,27ppm/ Grad Celsius.

(3) Ceramic substrate

* Aluminum oxide, Aluminiumnitrid, Siliziumkarbid und andere keramische Materialien als Verpackungssubstrat. CTE ist klein, 6–8ppm/ Grad Celsius.

Kennzeichnend durch die Technologie der Verbindung

(1) Play pattern to engage the carrier plate

* The gold wire connects the IC to the Leiterplatte.

(2) TAB PCB

*TAB -- TapeAutomatedBonding

* The inner pins of the chip are connected with the chip, und die äußeren Stifte sind mit dem Verpackungskarton verbunden.

(3) Überlagerung der Leiterplatte mit Kristallverklebung.

*Filpchip, Der Wafer ist Filp bumped und verbindet sich direkt mit dem Leiterplatte.