Comme son nom l'indique, une puce inversée est une méthode d'encapsulation qui relie la face avant de la puce (le côté sur lequel le circuit IC est fabriqué) vers le bas à un substrat. Les bornes de signaux électriques sont réalisées en soudure classique et peuvent être interconnectées avec le substrat. Dans ce type d'interconnexion, les bornes d'entrée et de sortie (I / o) peuvent couvrir l'ensemble de la puce, de sorte que la densité des interconnexions de puces inversées est beaucoup plus élevée que celle des jonctions de fils, même au même pas. Dans une interconnexion par liaison filaire, les E / s ne peuvent être disposées que autour de la puce. Ainsi, quelle que soit la taille de l'espacement, la densité d'E / s des interconnexions de puces inversées n'est pas réalisable. La technologie de bloc est la clé de toute la technologie d'interconnexion de puce inversée.

Vue d'ensemble de la technologie des blocs de plaquettes la clé pour la fabrication des blocs de plaquettes est le dépôt d'une couche métallique sous - jacente aux blocs (UBM). Il est à noter que le terme utilisé précédemment par IBM était la couche de métallisation à contrainte sphérique (BLM), dont le rôle était de fournir une couche de liaison pour les interconnexions; Une barrière de diffusion atomique est prévue pour empêcher la diffusion des atomes du matériau de la bosse vers la structure métallique sous - jacente; Le matériau diélectrique sous - jacent et le métal constituent une couche adhésive et servent de barrière empêchant la migration des contaminants vers le métal sous - jacent dans la direction horizontale de la couche diélectrique. La plupart des UBM actuellement utilisés sont réalisés par pulvérisation. Le procédé de pulvérisation est le procédé le plus rentable pour la fabrication d'UBM. Surtout par rapport au processus d'évaporation. Le facteur le plus direct qui affecte la fiabilité structurelle des points de soudure est la qualité de la production d'UBM. En général, les structures UBM doivent être capables de résister à plusieurs reflux (généralement jusqu'à 20) sans dommage. Étant donné que l'UBM est une structure utilisée pour lier les plots de soudure et les couches de métallisation des plots, il doit également passer des tests de contrainte de cisaillement et de traction. Dans les tests de dommages mécaniques, le critère général pour la défaillance des billes de soudure est que la défaillance se produit dans la soudure elle - même. Par conséquent, UBM doit avoir une force suffisante. Il n'y aura pas de baisse de performance due à des facteurs tels que le temps, la température, l'humidité et la tension de polarisation.

Tendance du marché des puces inversées l'encapsulation des puces inversées est devenue la technologie d'interconnexion d'encapsulation dominante. Jusqu'à présent, la puce inversée était en fait considérée comme un boîtier plutôt que comme une technologie d'interconnexion. Par exemple, le Flip Chip Ball Grid Array Encapsulation (fcbga) utilise principalement la technologie de substrat stratifié pour compléter le processus d'assemblage et d'encapsulation, mais est limité aux applications de circuits intégrés hautes performances. Le diagramme ci - dessous montre les domaines d'application des puces inversées:

(1) espacement des points convexes: réduire l'espacement des points convexes peut augmenter la densité d'E / s; Tendance à la variation du bitume (passage progressif de 250 à 125 microns);

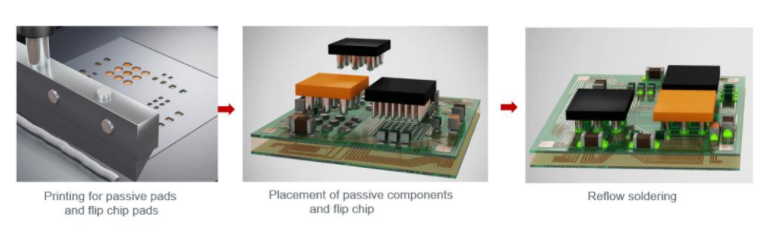

(2) Méthode d'enfoncement du point de soudure: sérigraphie évaporée plaquée;

(3) Composition de la soudure à billes: teneur élevée en plomb faible eutectique sans plomb (Sn - AG) - espacement des colonnes Cu < 125 microns;

(4) Composition de l'emballage: substrat en céramique substrat stratifié d'interconnexion haute densité substrat stratifié préimprégné substrat stratifié à faible coefficient de dilatation thermique? Substrat sans noyau.

(5) Structure d'emballage: couvercle monolithique scellé (SPL) - renfort de couvercle monolithique non scellé + couvercle en forme de feuille nue

Les marchés d'application des fccsp traditionnels sont les suivants:

Marché des applications fccsp:

(1) densité de billes (I / o) par rapport à la taille de la puce: pour les tailles de puces supérieures à 200 I / o ou supérieures à 5,5 mm; Les produits à faible densité utilisent wlcsp pour un meilleur coût.

(2) faible puissance: puissance générale < 2W selon = "" on = "" Chip = "" Board Level = "" Packaging = "" Can = "" be = "" used = "" for = "" Power = "" Bare = "" fccsp = "" > 2W).

(3) Zone: pour les appareils portables, la technologie 40nm / 65nm réduit la taille de la puce, mais plus d'E / s font que les E / s périphériques n'ont pas assez de surface pour être disposés, il est donc nécessaire d'utiliser des fils de substrat pour éventrer cette zone.

(4) prix: pour les puces de petite taille d'E / s élevées, l'insuffisance de la zone périphérique, le coût de la ligne au et le substrat de grande taille pour le secteur de plomb stimuleront le développement de fccsp à prix compétitif.

(5) moulé, facile à tester et à tenir, la forme commune est la même que cabga.

Résumé

La puce inversée a toujours été une technologie d'emballage passionnante. Mais son coût limite les puces inversées à devenir la technologie dominante par rapport aux boîtiers de liaison par fil traditionnels. Cependant, les contraintes de coûts sont progressivement supprimées et l'utilisation de puces de retournement encapsulées en bandes réduit considérablement leur coût. Étant donné que les substrats stratifiés représentent la majeure partie du coût du produit, la réduction du coût des substrats stratifiés est le moyen le plus efficace de réduire le coût d'encapsulation des puces inversées.

En outre, pour la conception fpfc, amkor a effectué de nombreuses recherches pour transformer la conception de puce inversée area array existante en une conception à espacement fin. 80% des études ont montré que les conceptions périphériques finement espacées peuvent réduire le coût du substrat en raison de la réduction des couches métalliques et de la réduction des dimensions extérieures. En réduisant le coût du substrat d'encapsulation de puce inversée (qui est le plus coûteux), l'encapsulation de puce inversée peut être rendue largement disponible sur d'autres marchés.