Principes et applications d'encapsulation de circuits intégrés 3D

La couche diélectrique 2.5D est une configuration dans laquelle les noyaux sont montés côte à côte sur une couche diélectrique de silicium, de verre ou organique en utilisant des Vias de silicium (TSV) traversant la couche diélectrique. (lorsque le verre ou les stratifiés organiques sont utilisés comme substrat pour la couche intermédiaire, ils sont connus comme traversant le verre (TGV) et traversant le substrat (TSV), respectivement.) La communication entre les coeurs est réalisée au moyen de circuits réalisés sur la couche intermédiaire.

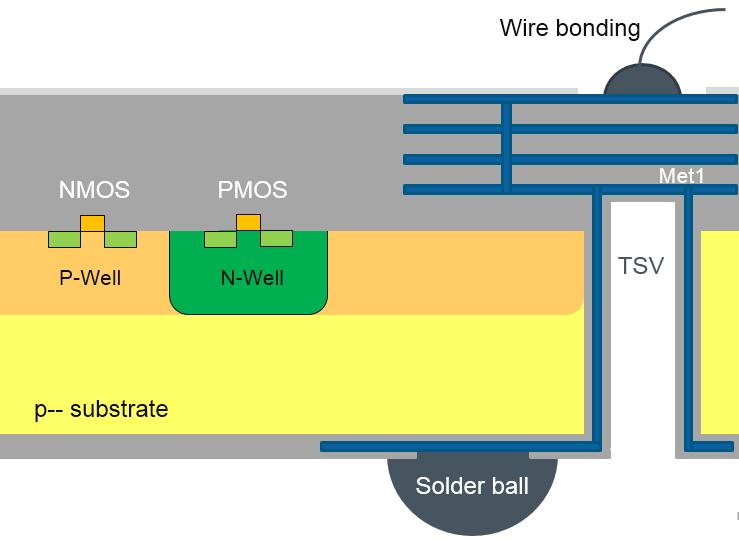

Le capteur d'image CMOS (CIS) dispose d'un TSV comme trou arrière pour former l'interconnexion, ce qui élimine la fusion de clés de connexion, ce qui réduit la taille et augmente la densité. Dans tous les types de boîtiers 3D, les puces dans le boîtier communiquent en utilisant des signaux hors puce comme si elles étaient montées dans un boîtier séparé sur une carte de circuit ordinaire.

L'IC 3D peut être divisé en IC empilés 3D (3D - SiC), ce qui signifie que la puce IC est empilée et interconnectée avec le TSV; Les circuits intégrés 3D réels utilisent le processus FAB pour empiler plusieurs couches de dispositifs sur une seule puce, avec ou sans tsvs très finement espacés pour former des interconnexions.

Les Vias de silicium (TSV) sont des trous réalisés sur une tranche de silicium à l'aide d'un procédé de gravure. Les interconnexions sont réalisées en remplissant le TSV d'un matériau conducteur tel que le cuivre, le tungstène ou le silicium polycristallin (Figure 2). Le principal avantage des interconnexions TSV est qu'elles raccourcissent le trajet des signaux d'une puce à l'autre ou d'une couche de circuits à l'autre. Cela permet de réduire la puissance et d'augmenter la densité d'interconnexion, améliorant ainsi la fonctionnalité et les performances. Le TSV lui - même n'est pas un IC 3D. Au lieu de cela, ils sont la base pour activer les circuits intégrés 3D. Les Vias arrière sont également utilisés dans d'autres dispositifs tels que les capteurs d'image, les systèmes microélectromécaniques (MEMS) et les semi - conducteurs composés.

Quelle est la signification d'un IC 3D monolithique?

Au lieu d'empiler des tranches ou des modules pour créer des circuits intégrés 3D, les circuits intégrés 3D monolithiques commencent par une tranche de base sur laquelle des couches supplémentaires telles que du silicium cristallin, des couches métalliques et des circuits actifs et passifs sont ajoutées à l'aide de dispositifs FAB traditionnels (Figure 2). Réaliser des interconnexions verticales entre les couches plutôt qu'entre les puces à l'aide de Vias de portée nanométrique plutôt que micrométrique; Pareil pour TSV. Plusieurs méthodes différentes sont actuellement en cours de développement, principalement pour les applications de mémoire. Integral 3D est parfois appelé Sequential 3D.

Qu’est - ce que la mémoire 3D?

De nombreuses méthodes ont été développées pour empiler des mémoires perpendiculairement à deux dispositifs de mémoire non volatile (flash NAND) et de mémoire volatile (DRAM). Les méthodes DRAM comprennent la mémoire haute bande passante (hbM), le cube de mémoire hybride de micron et la RAM intégrée (diram) de tezzaron. Tout cela est basé sur un ci 3D utilisant TSV (Figure 3). Samsung, Toshiba et de nombreuses autres sociétés développent des mémoires flash NAND 3D basées sur une approche holistique de la 3D.

Quels sont les avantages de la technologie 2.5D Inserter?

La technologie 2.5D a été développée à l'origine comme une technologie de pont pour les circuits intégrés 3D et a maintenant évolué pour devenir une plate - forme d'encapsulation qui promet de coexister avec les circuits intégrés 3D. Contrairement aux circuits intégrés 3D, seule la couche intermédiaire (et non le noyau lui - même) nécessite un TSV pour connecter le noyau actif au substrat d'encapsulation. Cela permet d'utiliser les conceptions de moules existantes.

Quels sont les principaux moteurs technologiques de l’intégration 3D?

Sur les nœuds de la prochaine génération de puces, le coût accru de cette étape de lithographie et de traitement des plaquettes a incité l'industrie à rechercher des alternatives pour améliorer les performances et les fonctionnalités de nos appareils électroniques et réduire les coûts. De plus, la nécessité d’intégrer à petite échelle diverses technologies (logique, mémoire, RF, capteurs, etc.) pousse l’industrie à adopter l’intégration 3D comme solution.

Quels sont les moteurs du marché de l’intégration 3D?

La force motrice du marché de l'intégration 3D (3D Integration) commence par l'informatique haut de gamme, les serveurs et les centres de données, les équipements militaires et aérospatiaux et les dispositifs médicaux, car ils sont les plus demandés et peuvent supporter le coût des technologies d'intégration 3D actuelles. Les tablettes, les smartphones et les appareils de jeu font également progresser cette technologie.

Quels sont les défis des circuits intégrés 3D?

Bien que beaucoup prétendent qu'il n'y a pas de défis techniques restants et que les problèmes restants peuvent être facilement résolus, certaines étapes du processus nécessitent encore de meilleures solutions, telles que des outils de conception pour la planification, la mise en œuvre et la validation de circuits intégrés 2.5D et 3D, le traitement des plaquettes, la gestion thermique et les tests. Les principaux défis sont les coûts unitaires actuels, les faibles volumes et les risques de mise en œuvre dus à la maturation des écosystèmes. Des efforts sont déployés pour réduire les coûts des processus et simplifier la collaboration dans l'ensemble de l'industrie. Augmenter la production aidera à réduire les coûts. Cependant, de nombreux experts en 3D estiment que la mise en œuvre de circuits intégrés 3D réduira considérablement les coûts du système, et le défi restant est d’éduquer les ingénieurs de niveau système sur les avantages de la conception de circuits intégrés 3D dans leurs systèmes.

Le capteur d'image CMOS (CIS) a été l'un des premiers dispositifs à implémenter un grand nombre de trous traversants. Le CIS avec éclairage arrière (BSI) est actuellement en production et, comme le CIS est empilé sur le dessus de l'IC, il s'agit d'un dispositif IC 3D (Figure 2). Xilinx a lancé le plug - in 2.5D en 2011 pour tous les FPGAs programmables de sa gamme virtex - 7. Au cours des dernières années, tezzaron a livré de petites quantités de diram.

Fin 2014, micron et Samsung commenceront à produire le Hybrid Storage cube (HMCS), une pile de DRAM 3D située au - dessus des périphériques logiques. SK Hynix fournira à la fois le HMC et le hbM (High Bandwidth Memory). Ces dispositifs de stockage 3D intégrés ont été produits en série en 2014 / 15 et ont continué à utiliser des piles logiques et des dispositifs hétérogènes pendant plusieurs années.

IPCB partagera toutes les informations avec vous!