Un système de station de base (BTS) doit répondre aux exigences d'indicateur d'une liaison de signal tout en répondant à divers critères. Cet article décrit certains dispositifs de liaison de signal pour les ADC dynamiques à haute performance et les dispositifs RF dans les récepteurs RF numériques, tels que les ADC à haute performance dynamique, les amplificateurs à gain variable, les mélangeurs et les oscillateurs natifs, et détaille leur utilisation dans les stations de base typiques pour répondre aux exigences des systèmes de stations de base en termes de performances dynamiques élevées, de performances d'interception élevées et de faible bruit.

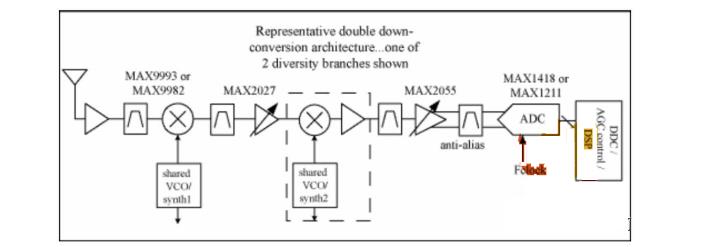

La plupart des récepteurs numériques ont des exigences élevées pour les convertisseurs analogiques - numériques (ADC) et les simulateurs haute performance. Par example, un récepteur numérique de station de base cellulaire nécessite une plage dynamique suffisante pour traiter des signaux parasites importants afin de démoduler un signal utile de bas niveau. Le convertisseur analogique - numérique 15 bits 65 MPS max1418 ou le convertisseur analogique - numérique 12 bits 65 MPS max1211 de Maxim, couplé à un mélangeur intégré 2 GHz max9993 ou 900 MHz max9982, peut fournir d'excellentes caractéristiques dynamiques pour les circuits clés à deux étages du récepteur. De plus, les amplificateurs de gain à réglage numérique à fréquence intermédiaire (IF) max2027 et max2055 de Maxim peuvent fournir une coupure de sortie du troisième ordre (oip3) élevée dans de nombreux systèmes et répondre à la plage de réglage de gain requise par le système.

Puces et circuits max1418 ADC

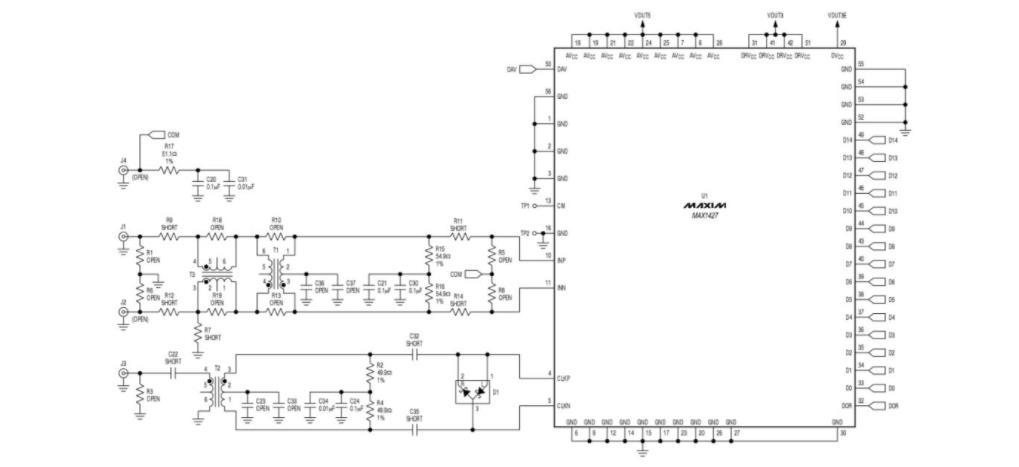

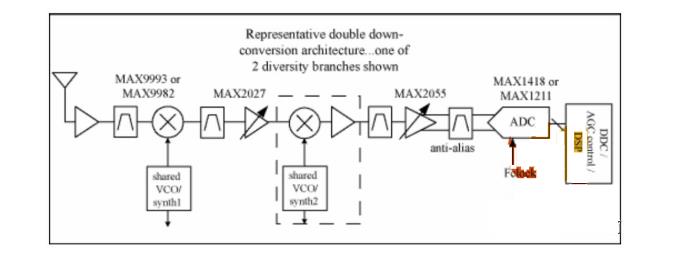

Une station de base cellulaire (BTS: Base Station Transceiver) est composée de plusieurs modules matériels différents, dont un module émetteur - récepteur (TRX) qui assure les fonctions de réception RF (RX) et d'émission RF (TX). Dans les anciens amplificateurs analogiques et Tac BTS, un seul émetteur - récepteur ne pouvait être utilisé que pour traiter une seule porteuse RF RX et TX en duplex intégral. Pour obtenir la couverture d'appel requise, de nombreux émetteurs - récepteurs sont nécessaires pour fournir une porteuse suffisante. Aujourd’hui, dans le monde entier, la technologie analogique a été remplacée par le CDMA et le WCDMA, et le GSM a été adopté en Europe il y a 10 ans. En CDMA, plusieurs utilisateurs appelants utilisent la même fréquence RF, de sorte qu'un émetteur - récepteur peut traiter simultanément les signaux de plusieurs utilisateurs appelants. Jusqu'à présent, il existe différentes options de conception pour CDMA et GSM. Les fabricants de BTS ont également cherché à explorer des moyens de réduire les coûts et la consommation d'énergie. L'optimisation d'une solution monoporteuse ou le développement d'un récepteur multiporteuse sont des solutions efficaces. La figure 1 est un schéma bloc structurel d'un récepteur de sous - échantillonnage couramment utilisé dans un dispositif BTS.

Figure 1. Diagramme bloc de la structure du récepteur de sous - échantillonnage

Sur la figure 1, les mélangeurs max9993 à 2 GHz et max9982 à 900 MHz de Maxim peuvent fournir le gain et la linéarité nécessaires pour de nombreuses conceptions et ont un bruit de couplage très faible, de sorte que ceux avec des pertes élevées ne sont plus nécessaires. Max2027 et max2055 fonctionnent dans les premier et deuxième étages de fréquence du récepteur. L'oip3 de ces deux dispositifs peut atteindre + 40 DBM sur toute la plage de réglage du gain. Dans le circuit de la figure 1, on utilise max1418 (15 bits, 65 MSPS) et max1211 (12 bits, 65 MSPS) comme Convertisseurs de données. En outre, les produits de conversion de données de Maxim ont d'autres appareils avec des taux d'échantillonnage qui peuvent répondre à la plupart des exigences de conception. Si le deuxième convertisseur inférieur de la figure 1 (représenté en pointillés) est omis, le circuit de la figure 1 devient une structure de convertisseur inférieur unique. Maxim ADC à faible bruit: max1418.

La structure du récepteur de sous - échantillonnage représenté sur la figure 1 impose des exigences strictes en matière de bruit et de distorsion de l'ADC. Dans le récepteur, les signaux utiles de bas niveau sont numérisés individuellement ou accompagnés de signaux inutiles de grande amplitude nécessitant plus d'attention. Par conséquent, pour que le récepteur fonctionne correctement, le coefficient de bruit effectif de l'ADC doit être calculé en fonction des conditions extrêmes de ces deux signaux, à savoir le signal utile minimal et le signal inutile maximal. Pour les signaux d'entrée analogiques plus petits, le bruit thermique et le bruit de quantification sont la base de bruit de l'ADC, ce qui détermine le coefficient de bruit de l'ADC.

En effet, le coefficient de bruit effectif de l'ADC dans des conditions de faible signal est déterminé, de même que le coefficient de bruit concaténé du circuit analogique (RF ou if). Le gain de puissance minimal du circuit de l'étage avant de l'ADC doit satisfaire aux exigences du coefficient de bruit du circuit récepteur. Typiquement, la valeur du gain de puissance est la limite supérieure du niveau maximal de blocage ou du niveau maximal d'interférence autorisé par le récepteur avant la surcharge de l'ADC. En BTS, sans l'utilisation de l'AGC, la plage dynamique de l'ADC ne répondra pas aux exigences du coefficient de bruit du circuit (sensibilité du récepteur) et du blocage maximal. Le circuit AGC peut être placé dans un circuit de niveau RF ou If ou dans un circuit à deux étages du circuit AGC.

Les autres produits de la série max1418 sont particulièrement adaptés aux applications en bande de base avec feinput = fclock / 2. Lorsque le convertisseur fonctionne dans cette gamme de fréquences, l'utilisation de ces dispositifs avec d'excellentes caractéristiques de bande de base permettra d'obtenir une plage dynamique optimale. Ces produits comprennent max1419 pour un taux d'horloge de 65 MSPS et max1427 pour un taux d'horloge de 80 MSPS. Leur bande de base sfdr (gamme dynamique sans parasites) peut atteindre 94,5 DBC.

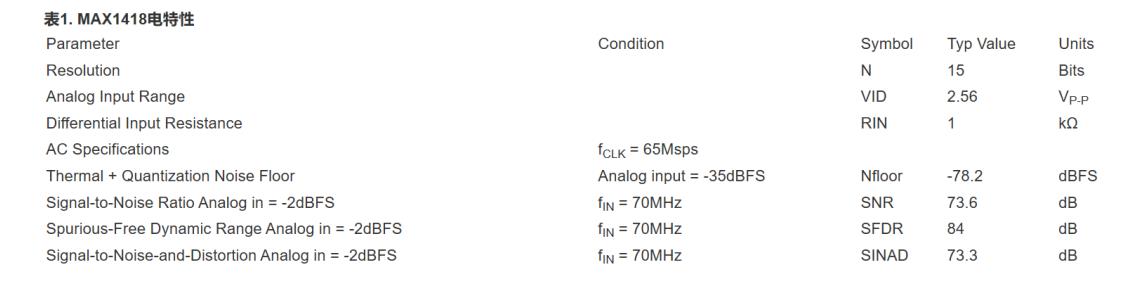

Le tableau 1 présente les principaux paramètres techniques du max1418

Le max1418 peut également fonctionner avec un périphérique d'interface 14 bits lorsque le LSB n'est pas connecté. De cette façon, le SNR sera légèrement perdu et le sfdr ne sera pas affecté.

La figure 2 montre la répartition du bruit de l'ADC en l'absence de blocage. En supposant ici un coefficient de bruit total en cascade de 3,5 DB pour tous les circuits analogiques précédant l'ADC, l'objectif de conception est que la dégradation du coefficient de bruit total résultant de l'ADC ne dépasse pas 0,2 DB pour répondre aux exigences de sensibilité du récepteur de station de base CDMA. Une telle valeur de coefficient de bruit devrait laisser une marge suffisante pour l'interface air, mais le résultat final dépend des exigences EB / No (rapport de l'énergie BIT à la densité spectrale de puissance du bruit) du détecteur du dernier étage. Basé sur la base de bruit thermique + bruit de quantification de max1418 dans le tableau 1, son coefficient de bruit équivalent est de 26,9 DB lorsque l'horloge du dispositif est de 61,44 MSPS (50 fois le débit chip). Grâce au contrôle de gain du processus, le bruit ADC à la bande passante du canal CDMA de 1,23 MHz est inférieur de 14 dB à celui de l'ADC à la bande passante de Nyquist. Typiquement, pour obtenir un facteur de bruit en cascade de 3,7 DB pour un récepteur, le gain total doit atteindre 36 db.

Figure 2: Distribution de bruit ADC sans blocage

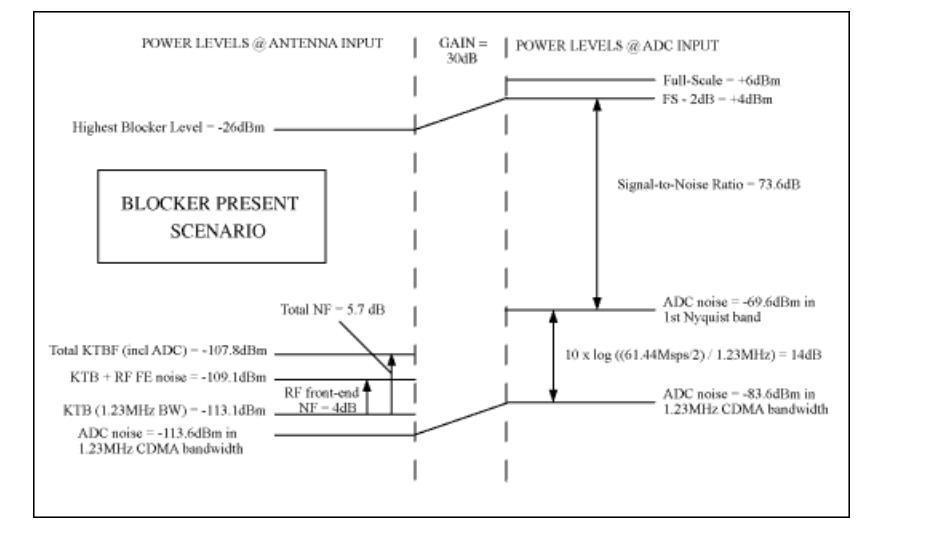

Lorsque le gain frontal de l'ADC est de 36 DB, un niveau de blocage monotone dépassant - 30 DBM à l'extrémité de l'antenne dépassera la plage d'entrée de l'ADC. La norme cdma2000® Cellular base station spécifie que le niveau de blocage maximal autorisé à l'extrémité de l'antenne est de - 30 DBM. À ce stade, le gain frontal doit être réduit de 6 DB pour permettre au signal de blocage maximal ajouté à l'ADC d'être plus important dans les limites autorisées par les spécifications standard. En supposant qu'il reste une marge de 2 DB, le niveau de blocage maximal à l'extrémité de l'antenne passera à - 26 DBM et le signal d'entrée maximal admissible de l'ADC passera à + 4 DBM lorsque le gain à l'extrémité courante diminuera de 6 DB (voir figure 3). En cas de blocage monotone, la norme cellulaire permet une dégradation de 3db de la perturbation totale (bruit + distorsion) par rapport à la sensibilité de référence, mais la répartition de 3db entre bruit et distorsion est laissée au concepteur.

Hypothèse: dans le cas d'un signal bloqué, le gain AGC est de 6 DB et la conception permet de réduire NF de 1 DB (valeur nominale de 3,5 DB) par le bruit en cascade et la distorsion en façade RF. Lorsque le gain en façade ADC n'est que de 30 DB, le rapport signal sur bruit de l'ADC détermine son coefficient de bruit effectif de 29,4 DB et celui du récepteur en cascade de 5,7 dB en "conditions bloquées", C'est 2 DB de moins que le coefficient de bruit de 3,7 DB calculé à partir de la sensibilité du récepteur. Comme les propriétés parasites ne sont pas prises en compte dans ce calcul, la plage dynamique sans parasites (sfdr) de l'ADC permet une réduction supplémentaire de 1 db. Lorsqu'un signal de blocage est présent, le sinad peut être utilisé pour calculer le NF effectif et les valeurs de base du bruit et du sfdr ne sont plus calculées séparément.

Figure 3. Réponse au bruit ADC en cas de blocage

Max11211 permet une structure de conversion de fréquence inférieure

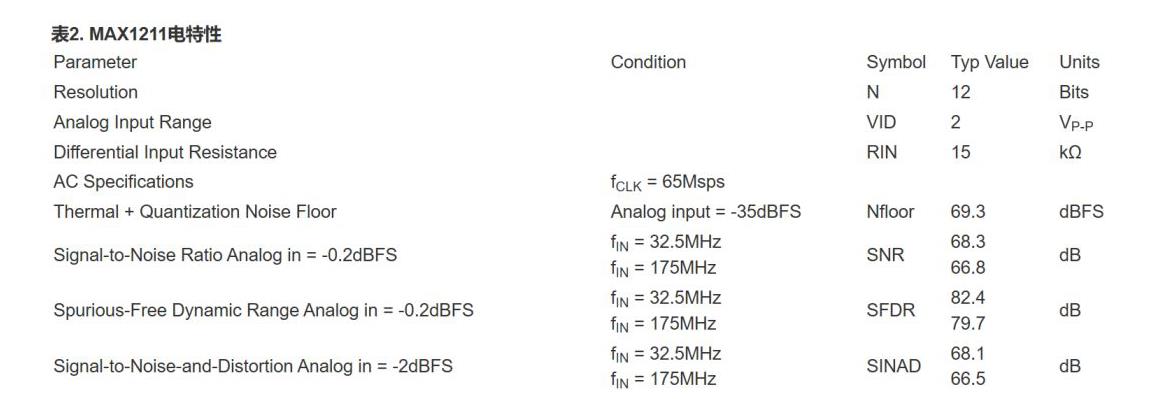

Si des indicateurs SNR et sfdr suffisants peuvent être obtenus dans les segments if supérieurs, un circuit de sous - échantillonnage peut être utilisé dans une structure de sous - conversion primaire. Le convertisseur max1211 12 bits 65msps a été conçu avec cette structure. Ses broches sont compatibles avec les prochains convertisseurs 80msps et 95msps. Cette gamme d'appareils permet d'échantillonner directement les signaux d'entrée jusqu'à 400 MHz s'ils sont nombreux. En outre, il dispose d'autres performances avancées, telles que l'entrée d'horloge peut être un signal différentiel ou un signal à extrémité unique, le rapport cyclique de l'horloge peut être compris entre 20% et 80%, en plus, il dispose d'un indicateur de validité de données (pour simplifier l'horloge et la séquence de données) et utilise un petit boîtier qfn à 40 broches (6mm x 6mm X 0,8mm), un complément binaire et un format de sortie numérique Grey Code. Le tableau 2 présente les caractéristiques AC typiques de max1211 avec une fréquence d'entrée analogique de 175 MHz.

Diagramme 2. Max1211 Caractéristiques électriques

La conversion primaire présente des avantages évidents par rapport à la structure de la conversion secondaire. Grâce à l'élimination du deuxième mélangeur à changement de fréquence inférieur, du deuxième circuit à gain de fréquence intermédiaire et du deuxième synthétiseur lo, le nombre de composants et l'espace de la carte peuvent être réduits d'environ 10% et les coûts peuvent être économisés de 10 à 20 $.

Considérez l'hétérogénéité des différentes structures. Si des économies supplémentaires sur le nombre d'éléments, l'espace de la carte, la consommation d'énergie et les coûts sont nécessaires, la structure de conversion de fréquence primaire donnée ci - dessous peut être adoptée. Supposons que le récepteur CDMA2000 conçu fonctionne dans la bande PC avec une fréquence d'échantillonnage de 61,44 MSPS, une fréquence de référence du synthétiseur de 30,72 MHz, le Centre de la première fréquence intermédiaire étant choisi dans la sixième bande Nyquist de 169 MHz avec une largeur de bande d'environ 1,24 MHz pour une structure DDS, Les mêmes 169 MHz première fréquence intermédiaire et deuxième fréquence centrale intermédiaire sont 46,08 MHz de la bande de Nyquist du deuxième ordre.

Propriétés parasites imaginaires des architectures SDC et DDC

Le tableau 3 présente les conditions hypothétiques pour la recherche parasite de porteuse RF près de l'extrémité supérieure de la bande PC lorsque l'on utilise une seule porteuse, une structure primaire à conversion descendante (SDC) et deux structures à conversion descendante (DDC). Pour la structure SDC, 134 composantes harmoniques peuvent être trouvées dans la fréquence de réception RF, la bande miroir de réception, la bande if et la bande miroir if. La plupart de ces signaux parasites sont d'ordre supérieur et ne dégradent pas les performances de réception. Pour les structures DDC, une recherche parasite trouvera plus de 2400 harmoniques, soit plus de 18 fois plus que pour les structures SDC. Ces harmoniques sont réparties dans la bande de réception RF, la bande miroir de réception, un premier niveau si la bande de fréquence, un niveau si la bande miroir, un deuxième niveau si la bande de fréquence et un deuxième niveau si la bande miroir. Pour les signaux parasites provenant des harmoniques d'horloge d'ordre supérieur et de la fréquence de référence du synthétiseur, il est possible de les supprimer en examinant attentivement la disposition de la carte ou en ajoutant un filtrage à la conception. Cependant, il est difficile d'inhiber un grand nombre de composantes parasites d'ordre inférieur.

Amplificateurs Maxim Mid - frequency: max2027 et max2055

Maxim offre également un gain de contrôle numérique de 1 DB par étage et un amplificateur if haute performance. Le max2027 est un amplificateur de gain à commande numérique (dvga). Il utilise un mode d'entrée / sortie unique et peut fonctionner dans la gamme de fréquences de 50 MHz à 400 MHz avec un facteur de bruit de gain maximal de seulement 5 db. Le max2055 est un dvga à entrée / sortie différentielle unique qui pilote des ADC haute performance dans la gamme de fréquences de 30 MHz à 300 MHz. Un transformateur élévateur peut être utilisé entre la sortie différentielle du max2055 et l'entrée différentielle de l'ADC. Le transformateur fournit un entraînement différentiel qui favorise l'équilibre entre les signaux de sortie. Les deux dvga fonctionnent avec une polarisation de 5V et ont un oip3 de + 40dbm sur toute la plage de réglage du gain. Pour plus de détails, consultez les informations pertinentes sur le site Web de Mei - heart (china.maxmantegrade.com). Mélangeurs haute linéarité de Mei - Heart: max9993 et max9982.

Dans les circuits de réception, les mélangeurs ont tendance à résister à des signaux d'entrée plus importants, avec des exigences de performance plus élevées. Dans un état idéal, l'amplitude et la phase du signal de sortie du mélangeur sont proportionnelles à l'amplitude et à la phase du signal d'entrée et la relation de proportionnalité est indépendante du signal lo. Selon cette hypothèse, la réponse en amplitude du mélangeur est linéaire avec l'entrée RF et indépendante du signal d'entrée lo.

Cependant, la non - linéarité du mélangeur engendre un signal de mélange indésirable, appelé réponse parasite, qui est la réponse de la bande if produite par le signal arrivant sur le port RF du mélangeur et qui n'est pas attendue. Les signaux parasites inutiles interfèrent avec le fonctionnement des signaux RF utiles. Si la fréquence du mélangeur peut être donnée par la formule suivante:

Si = ± mfrf ± nflo, si, RF et lo sont les fréquences des signaux des ports respectifs et m et n sont les ordres harmoniques après mélange des signaux RF et lo.

Les mélangeurs équilibrés intégrés (ou actifs), tels que max9993 et max9982, ont attiré l'attention en raison de leurs performances supérieures aux schémas de mélange passifs. Lorsque m ou n est pair, le mélangeur équilibré peut supprimer une partie de la réponse parasite et les performances en second harmonique sont meilleures. Un mélangeur à double équilibre idéal peut supprimer toutes les réponses d'un nombre pair de m ou n (ou les deux). Dans un mélangeur à double équilibrage, les ports if, RF et lo sont isolés les uns des autres. En utilisant un transformateur de déséquilibre raisonnablement conçu, le mélangeur peut se chevaucher dans les bandes if, RF et lo. Les caractéristiques max9993 et max9982 comprennent: faible coefficient de bruit, lo Buffer, Low lo Drive, commutateur lo permettant deux entrées lo, excellentes caractéristiques de bruit lo, etc. en outre, le transformateur RF balourd est également intégré dans les ports RF et lo.

Ces mélangeurs de Maxim intègrent une mémoire tampon basse avec d'excellentes performances à faible bruit, ce qui réduit les exigences en matière d'alimentation à faible bruit. En général, la combinaison d'un faible bruit et d'un signal de blocage d'entrée de niveau élevé réduira la sensibilité de réception. Les max9993 et max9982 contiennent des tampons lo à faible bruit qui réduisent l'impact sur la sensibilité de réception en cas de blocage. Par example, supposons que le bruit en bande de bord du signal d'entrée VCO soit de - 145 dBc / Hz et que la caractéristique typique de bruit lo du max9993 soit de - 164 dBc / Hz, de sorte que le bruit en bande de bord composite ne diminue que de 0,05 dBc / Hz à - 144,95 dBc / Hz. De cette façon, l'utilisateur fournit non seulement un signal Lo de bas niveau au mélangeur, Il garantit également que les caractéristiques de mélange du récepteur ne sont pas dégradées par les performances du tampon lo intégré dans le max9993.

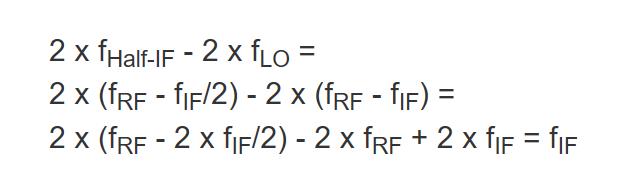

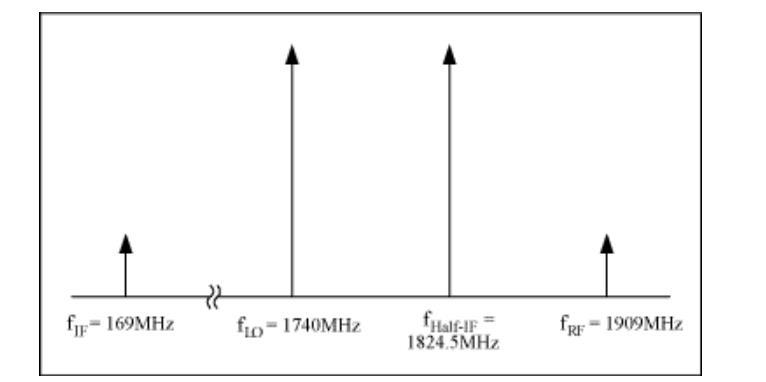

En outre, il existe une réponse parasite délicate du deuxième ordre, également appelée réponse parasite demi - if (1 / 2 if). Pour les injections bas de gamme, l'ordre du mélangeur est: M = 2, n = - 2; Pour l'injection haut de gamme, l'ordre des mélangeurs est: M = - 2, n = 2. Lorsque l'injection basse est basse, la fréquence d'entrée conduisant à une réponse parasite semi - imaginaire est inférieure à la fréquence RF requise (Figure 4). Les fréquences RF requises sont les fréquences 1909 MHz et 1740 MHz lo et la fréquence if est de 169 MHz. Bien que les largeurs de bande des porteuses RF et if du CDMA soient de 1,24 MHz, il est représenté ici comme un signal monofréquence à fréquence porteuse centrale. Dans cet example, un signal inutile de 1824,5 MHz conduit à une composante parasite demi - Fréquence intermédiaire de 169 MHz:

De là, nous pouvons obtenir:

2 x 1824,5 MHz - 2 x 1740 MHz = 169 MHz

Figure 4. Emplacement des FRF utiles, Flo, FIF et des fhalf inutiles (si fréquence)

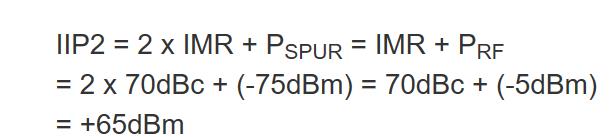

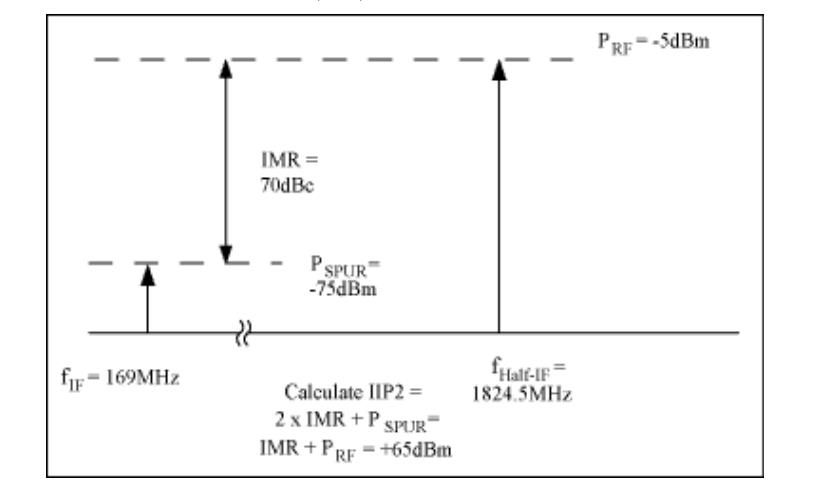

La réjection totale (également appelée réponse parasite 2X2) peut être prédite en fonction du deuxième point de coupure IP2 du mélangeur. La figure 5 montre 2X2 IMR ou valeurs parasites (données max9993 de Maxim). Remarque: le niveau du signal dans la figure est le niveau d'entrée du mélangeur calculé à partir des performances d'entrée IP2 (iip2). La formule de calcul spécifique est la suivante:

Comme la réponse parasite typique 2rf - 2lo fournie par le filtre actif Maxim max9982 900 MHz est de 65 DBC, son iip2 est calculé comme suit:

Figure 5. Calcul du deuxième point de coupure iip2 du signal d'entrée du mélangeur

Lorsque les exigences de gain du récepteur ne sont pas élevées, le Maxim 15 bits ADC max1418 a une excellente performance de bruit, de sorte qu'il peut résister à de grands niveaux de blocage ou d'interférence avec le plus petit AGC. Les produits de la série max1211 ADC sont adaptés aux structures de réception à changement de fréquence primaire avec une fréquence d'entrée initiale de fréquence intermédiaire pouvant atteindre 400 MHz. En outre, les mélangeurs max9993 et max9982 de Maxim peuvent fournir la linéarité requise, un faible coefficient de bruit et un gain de puissance élevé, de sorte que les filtres passifs peuvent être omis lors de la conception du récepteur. Les valeurs typiques de l'oip3 pour un maximum de 2027 et un maximum de 2055 dvga sont d'environ + 40 DBM sur toute la plage de réglage du gain. Un récepteur constitué de ces éléments permet d'augmenter les performances d'une solution à faible coût à un niveau supérieur. Cet article décrit certains ADC haute performance dynamique dans les récepteurs RF numériques et les dispositifs de liaison de signal pour les dispositifs RF, si vous avez des questions, bienvenue à communiquer avec IPCB.