Nuovo processo di galvanizzazione del substrato di IC: foro cieco, foro passante e riempimento incorporato della scanalatura

Astratto

Nell'era della miniaturizzazione dei prodotti elettronici, il substrato IC integrato ad alto rendimento e basso costo forniscono un modo affidabile per realizzare l'interconnessione ad alta densità (HDI) tra chip e PCB. Al fine di massimizzare lo spazio disponibile del vettore, la distanza tra il modello in rame -- la larghezza del modello e la spaziatura del modello (L/S) -- dovrebbe essere minimizzata. Nella tecnologia PCB comune, la larghezza del modello e la distanza del modello sono superiori a 40 μm, mentre la tecnologia di livello wafer più avanzata può raggiungere la larghezza del modello e la distanza del modello fino a 2 μm. Nell'ultimo decennio, le dimensioni dei chip sono diminuite significativamente con l'L/S a bordo, presentando sfide uniche sia per l'industria dei circuiti stampati che per i semiconduttori.

Fan-out Panel Level Packaging (FOPLP) è una nuova tecnologia di produzione progettata per colmare il divario tra i campi PCB e IC/semiconduttori. Sebbene FOPLP sia ancora una tecnologia emergente, è favorita dal mercato per la sua capacità di aumentare l'utilizzo dello spazio e la capacità del pavimento e di aumentare il vantaggio competitivo riducendo i costi. In questo mercato, la chiave per le prestazioni del circuito fine è l'uniformità o la planarità della placcatura. L'uniformità della placcatura, la planarità della parte superiore del filo/foro cieco (misura la planarità della parte superiore del filo) e il foro cieco sono caratteristiche delle sue prestazioni. Ciò è particolarmente importante nell'elaborazione di PCB multistrato, dove l'disomogeneità allo strato inferiore può influenzare i rivestimenti successivi, danneggiando il design del dispositivo e portando a conseguenze catastrofiche come i cortocircuiti. Inoltre, superfici irregolari possono deformare i punti di connessione (cioè fori ciechi e routing) e causare la perdita del segnale. Pertanto, soluzioni di galvanizzazione che forniscono profili uniformi e piatti senza alcun post-trattamento speciale sono attese dall'industria.

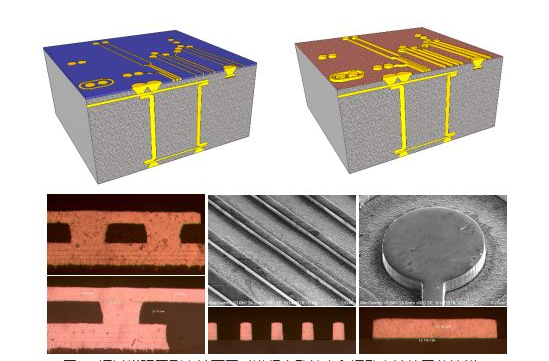

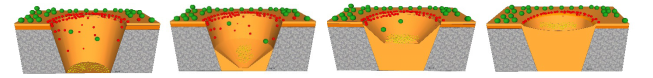

In questo articolo, viene introdotto un additivo composito innovativo per la placcatura in rame DC per il substrato IC. Il riempimento incorporato della scanalatura può essere realizzato migliorando la placcatura grafica e il riempimento del foro passante e cieco può essere completato allo stesso tempo. Questi nuovi prodotti non solo forniscono un profilo migliore del modello, ma possono anche essere riempiti fori ciechi e galvanizzati attraverso fori. Introduciamo anche due tipi di processi di galvanizzazione del rame dell'elettrolisi, che possono essere selezionati in base alla dimensione del foro cieco e ai requisiti concavi dell'applicazione specifica: Processo I può fornire un buon riempimento per fori ciechi profondi con diametro da 80μm a 120μm e profondità da 50μm a 100μm (Figura 1); Il processo II è più adatto per piccoli fori ciechi poco profondi con diametri da 50μm a 75μm e profondità da 30μm a 50μm.

Questi due processi possono ottenere un'eccellente uniformità superficiale e profilo di linea (FIG. 2). Questo articolo descrive il riempimento del foro cieco e le proprietà di galvanizzazione del foro attraverso determinati parametri all'interno della gamma di controllo. Descrive anche come ottimizzare la dissipazione del calore e le caratteristiche fisiche della metallizzazione galvanica

FIG.1 Le proprietà di processo del riempimento del foro cieco e dell'galvanizzazione del foro passante possono essere eseguite simultaneamente mediante galvanizzazione grafica migliorata

Prestazioni integrate di riempimento della scanalatura per mostrare un alto grado di coerenza tra pad e filo

L'introduzione

Il substrato IC è il più alto livello di tecnologia di miniaturizzazione PCB, fornendo la connessione tra il chip IC e il PCB attraverso una rete elettrica di fili di rame conduttori e fori passanti. La densità dei fili è un fattore chiave nella miniaturizzazione, velocità e portabilità dell'elettronica di consumo. Negli ultimi decenni, la densità lineare è aumentata notevolmente e lo sviluppo dell'imballaggio a livello di pannelli ventilatori (FOPLP) è diventato un argomento caldo nel campo della microelettronica per soddisfare i requisiti di progettazione dei circuiti stampati odierni, inclusi materiali a nucleo sottile, larghezza del modello di precisione e fori passanti e ciechi di diametro inferiore.

I principali driver di questa nuova tecnologia sono i costi e la produttività. Il tradizionale imballaggio a livello di wafer (FOWLP) utilizza wafer da 300 mm come unità di produzione perché ottenere wafer più grandi è difficile, aumenta le fasi di lavorazione, la manodopera e i costi e le rese sono inferiori. Il vantaggio di utilizzare caricatori simili a PCB rispetto ai wafer è che i produttori hanno flessibilità di progettazione e possono utilizzare un'area di pannello più ampia. Ad esempio, un pannello da 610 mmx457 mm ha quasi quattro volte la superficie di un wafer da 300 mm, riducendo notevolmente i costi, i tempi e le fasi di lavorazione, il che è un enorme vantaggio per la produzione di massa.

Tuttavia, l'applicazione della tecnologia FOPLP ai substrati richiede più ricerca e sviluppo e affronta sfide come la risoluzione e la deformazione. Se implementati con successo, si possono ottenere volumi più elevati, costi più bassi e confezioni più sottili, rendendo l'elettronica di consumo più veloce e leggera.

Riempimento del foro cieco in rame acido

Il processo di galvanizzazione è uno dei passaggi chiave nella produzione di scheda PCB. Attraverso la distribuzione corrente, il cablaggio, il foro cieco e la galvanizzazione attraverso il foro sulla scheda PCB possono essere realizzati. Il rame, come metallo conduttivo di scelta, è caratterizzato dal suo basso costo e dall'alta conducibilità. Con lo sviluppo della tecnologia del rame galvanizzato negli ultimi decenni, l'uso del rame come metallo galvanizzato è aumentato notevolmente. La progettazione avanzata del circuito stampato specializzato richiede attrezzature di galvanizzazione all'avanguardia e soluzioni di galvanizzazione innovative, quindi negli ultimi decenni, le apparecchiature di galvanizzazione a getto sono state ampiamente utilizzate.

Le soluzioni di riempimento galvanizzanti sono solitamente alte concentrazioni di rame (200 g/L a 250 g/L solfato di rame) e basse concentrazioni di acido (circa 50g/L acido solforico) per facilitare il riempimento rapido. Gli additivi organici sono utilizzati per controllare il tasso di placcatura e ottenere proprietà fisiche accettabili. Questi additivi devono essere progettati attentamente per soddisfare le esigenze del cliente per dimensioni di riempimento del foro di guida, resa, spessore superficiale del rame, tolleranza di distribuzione del rame del piatto e forma dei fori ciechi dopo la placcatura. Le formulazioni tipiche di placcatura includono inibitori, schiarenti e livellatori. In teoria, è possibile riempire il buco cieco solo con un sistema a due componenti contenente un inibitore e un illuminante, ma i sistemi a due componenti hanno problemi pratici, come grandi depressioni, riempimento di forma e il processo è difficile da controllare analiticamente.

Sia gli inibitori che i livellatori agiscono come inibitori, ma in modi diversi. Gli inibitori di tipo I come gli inibitori possono essere disattivati dagli schiarenti, mentre gli inibitori di tipo II come i livellatori non lo sono, e il vettore di solito è un composto poliossialchilico ad alto peso molecolare. Di solito adsorbono sulla superficie del catodo e formano uno strato sottile interagendo con gli ioni del cloruro, in modo che il vettore riduce la velocità di placcatura aumentando lo spessore effettivo dello strato di diffusione. I livelli di energia della superficie catodica sono equalizzati (lo stesso numero di elettroni può essere utilizzato localmente per galvanizzare tutti i punti della superficie catodica), con conseguente distribuzione più uniforme dello spessore di placcatura risultante.

Gli illuminanti, d'altra parte, aumentano il tasso di placcatura riducendo l'inibizione. Di solito sono composti contenenti zolfo di piccolo peso molecolare, noti anche come raffinatori di grano. L'agente livellante di solito consiste di catena retta contenente azoto/polimero ramificato e composti aromatici eterociclici o eterociclici, i composti sono solitamente struttura quaternaria (atomi caricati positivamente al centro e quattro sostituti), saranno adsorbimento selettivo ad alta densità di corrente, quali bordo, angolo e gonfiore locale, prevenire l'eccessiva placcatura del rame nell'area ad alta densità di corrente.

Il metodo di prova

La prova è stata eseguita in un serbatoio di galvanizzazione 8L e un serbatoio di prova 200L. Gli anodi insolubili sono utilizzati per una maggiore densità di corrente applicabile, facilità di manutenzione e distribuzione uniforme della superficie in rame. Dopo che la soluzione di placcatura è configurata, la soluzione di placcatura è galvanizzata a 1Ah/L, analizzata, regolata per correggere la concentrazione additiva e quindi viene eseguita la prova di placcatura. Ogni piastra di prova viene pulita con acido per 1 minuto, lavata con acqua per 1 minuto e decapata con acido solforico del 10% per 1 minuto prima della placcatura.

Condizioni operative e composizione del bagno di placcatura

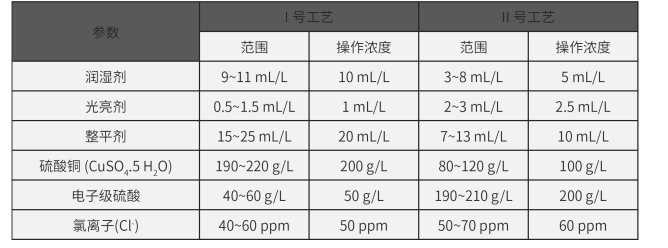

La FIG 1 mostra le condizioni operative e le concentrazioni ottimali degli additivi per le due formulazioni. Solitamente le soluzioni di galvanizzazione di riempimento del foro cieco sono ad alto contenuto di rame e basso contenuto di acido per raggiungere il riempimento inferiore del foro richiesto.

FIG1 Composizione del bagno galvanizzato e condizioni galvaniche

Meccanismo di riempimento del foro cieco

Il tasso di crescita del rame nel foro cieco e sulla piastra è controllato da additivi. FIG3 mostra un diagramma schematico della crescita del rame del foro cieco, mostrando i diversi ruoli svolti da ciascun additivo. L'adsorbimento selettivo e non selettivo può verificarsi durante la galvanizzazione anche se l'adsorbimento è localmente espanso. Gli additivi devono essere controllati all'interno delle impostazioni indicate nella Tabella 1 per ottenere il "riempimento bottom-up" richiesto. L'analisi può essere eseguita utilizzando strumenti analitici comunemente utilizzati nell'industria, come la voltammetria ciclica (CVS) e le prove a camera di sala.

In FIG3, il verde rappresenta l'inibitore, il rosso rappresenta l'agente livellante e il giallo rappresenta l'illuminante. Le molecole dell'agente bagnante sono principalmente adsorbite sulla superficie, inibendo la galvanizzazione in essa, mentre l'agente livellante è adsorbito selettivamente sull'area caricata negativamente a causa del sale amminico quaternario caricato positivamente, che può impedire l'eccessiva placcatura sul bordo ed evitare la chiusura prematura del foro cieco, con conseguente formazione di un foro nel centro. Brightener è una piccola molecola contenente zolfo che si diffonde più rapidamente nei fori ciechi per accelerare la galvanizzazione. Poiché la geometria dei fori ciechi cambia continuamente durante la galvanizzazione, l'illuminante si concentra nei fori passanti, con conseguente galvanizzazione rapida nei fori ciechi. Questo è chiamato meccanismo CEAC (Curvature Enhanced Accelerator coverage).

FIG3 Schema della meccanica CEAC m

Infine, quando la placcatura di rame nel foro cieco è quasi complanare con la superficie, il tasso di rivestimento nel foro cieco e sulla superficie diventa uguale e il riempimento dal basso verso l'alto si ferma. A seconda della forza dell'adsorbimento e del desorbimento dell'additivo, l'illuminante potrebbe non diffondersi come previsto e l'alta concentrazione di illuminante continuerà ad accelerare la placcatura, con conseguente sovraplaccatura nota come "corsa d'impulso".

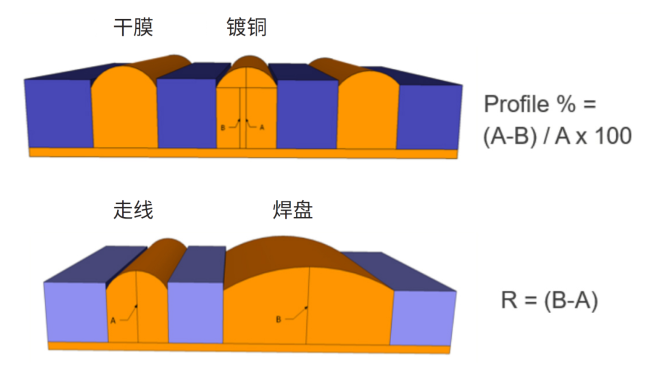

Misura del profilo del modello di precisione

FIG4 mostra il calcolo della velocità del profilo, definita come il rapporto tra la differenza di altezza tra i punti più bassi e più alti, espressa in percentuale, e il valore R, la differenza di altezza tra l'area del pad e la linea sottile, prendendo il minimo di entrambi i valori.

FIG4 Contour ratio e calcolo del valore R

Il design di processo NO.1 è stato progettato per riempire i fori ciechi, ottenendo una superficie piana e un profilo di linea migliore, e le condizioni di placcatura sono state ottimizzate, come mostrato nella FIG 5. Per ottenere la capacità di riempimento del foro cieco richiesta, una maggiore concentrazione di CuSO4 (200g/L) è stata combinata con una minore concentrazione di acido solforico (50g/L).

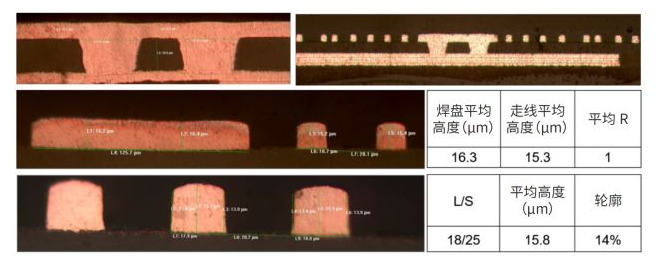

FIG5 Proprietà tipiche della galvanizzazione

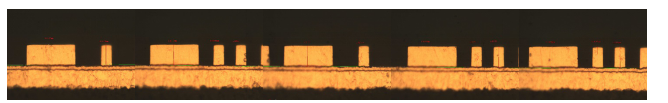

Le proprietà tipiche del processo n.1 sono mostrate in FIG5, dove la dimensione del foro cieco riempito è 60 μm*35 μm e lo spessore del rame è 15μm. Poiché il processo NO.1 può riempire il foro cieco con la superficie concava più piccola, non sono necessari ulteriori passaggi di appiattimento. Il rapporto del profilo è solitamente compreso tra il 10% e il 15%, tuttavia, in alcuni casi si osserva che la situazione effettiva è compresa tra il 15% e il 20%, lo spessore della placcatura di rame del filo è di 15 µm a 16μm e il valore R è compreso tra 1 e 2. I cuscinetti sono di forma più quadrata e hanno una superficie piana, con il cablaggio che mostra una leggera cupola.

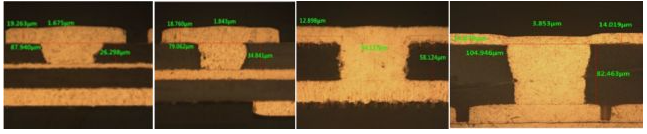

FIG6 Riempimento di fori ciechi 90 μm x 25 μm, 80 μm x 35 μm, 90 μm x 60 μm e 100 μm x80 μm di diverse dimensioni

La capacità di riempimento della formula per fori ciechi di diverse dimensioni è stata ulteriormente valutata. Sono stati testati quattro diversi fori ciechi: 90 μm x 25 μm, 80 μm x 35 μm, 90 μm x 60 μm e 100 μm x 80 μm rispettivamente. I risultati delle prove sono riportati nella figura 6. Per il riempimento di fori ciechi sotto i 90 μm*60 μm, non è stata osservata alcuna superficie concava, mentre il più grande foro cieco 100 μm*80 μm aveva una superficie concava di 4 μm.

Studio sulla durata della soluzione di galvanizzazione

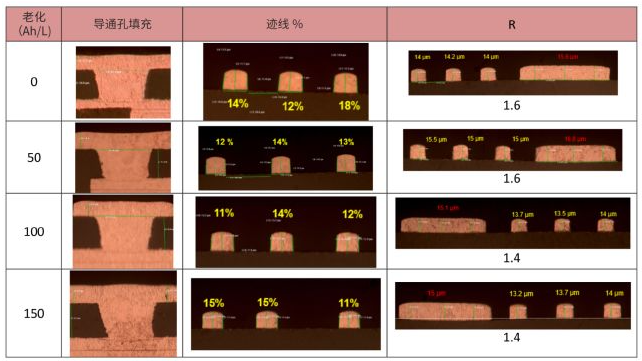

Dopo la valutazione iniziale delle prestazioni, la soluzione di placcatura è stata invecchiata a 150 Ah/L con un volume del serbatoio di 8 L. Ogni ciclo di placcatura è stato 15ASF per 45 minuti con la stessa concentrazione additiva indicata nella tabella 1.

durata della soluzione di galvanizzazione

Durante il test di invecchiamento del bagno, le schede di prova sono state elettroplaccate ad intervalli di 50Ah / L e campioni sezionati sono stati preparati e valutati al microscopio. La scheda di prova è composta da fori ciechi da 60 µm x35 μm e vari percorsi L/S. Le condizioni di placcatura sono state regolate per ottenere uno spessore di circa 15 μm sulla superficie. Durante l'intero processo di invecchiamento, il profilo del filo è nell'intervallo dal 10% al 15%, e occasionalmente dal 15% al 20%, che è coerente con i risultati iniziali della prova di prestazione e il valore R della placcatura piana è nell'intervallo da 1 a 2.

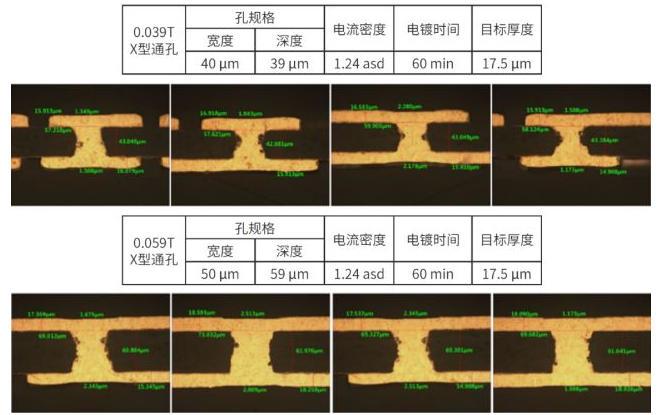

Prova la capacità di riempimento del foro passante utilizzando pannelli con spessore di 40μm e 60μm. I diametri dei fori dei due circuiti stampati sono rispettivamente 40 μm e 50 μm. I risultati sono riportati nella figura 7. Il periodo di galvanizzazione è 1.24ASD, della durata di 60 minuti

Capacità di riempimento dei fori a forma di x

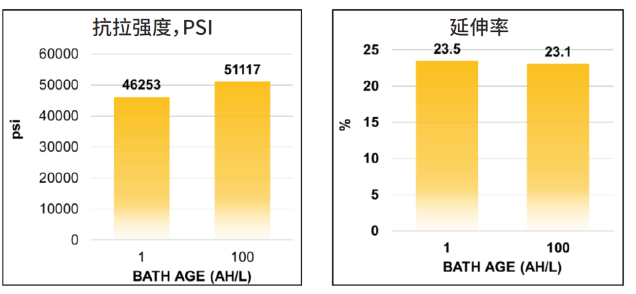

Resistenza alla trazione e allungamento

Due delle proprietà fisiche più importanti nella produzione di PCB sono la resistenza alla trazione e l'allungamento del conduttore in rame placcato, poiché queste proprietà indicano lo stress termico che il metallo rame può sopportare durante il montaggio e l'uso finale. Le proprietà fisiche sono il risultato di una combinazione di additivi tra cui inibitori, raffinatori di grano e livellatori. Queste proprietà dipendono anche dalla velocità di placcatura o dalla densità di corrente, dalla temperatura di placcatura e dalla morfologia del cristallo. Ad esempio, depositi densi di varie direzioni cristalline hanno proprietà fisiche migliori dei depositi colonnari.

Le proprietà fisiche sono state misurate secondo il metodo di prova 2.4.18.1 dello standard IPC TM-650 e poi i campioni sono stati tagliati in striscia e cotti in un forno a 125 gradi Celsius per 4 ~ 6 ore. La striscia del campione è stata testata con uno strumento di prova meccanico industriale e il valore misurato dello strumento è stato utilizzato per calcolare la resistenza alla trazione e la percentuale di allungamento. La figura 8 mostra i risultati di due diverse soluzioni per il bagno di invecchiamento: il nuovo bagno di placcatura e il bagno di invecchiamento di circa 100 Ah/L. I risultati mostrano che le caratteristiche non cambiano molto con l'aumento del tempo di galvanizzazione e soddisfano i requisiti dello standard IPC Livello III.