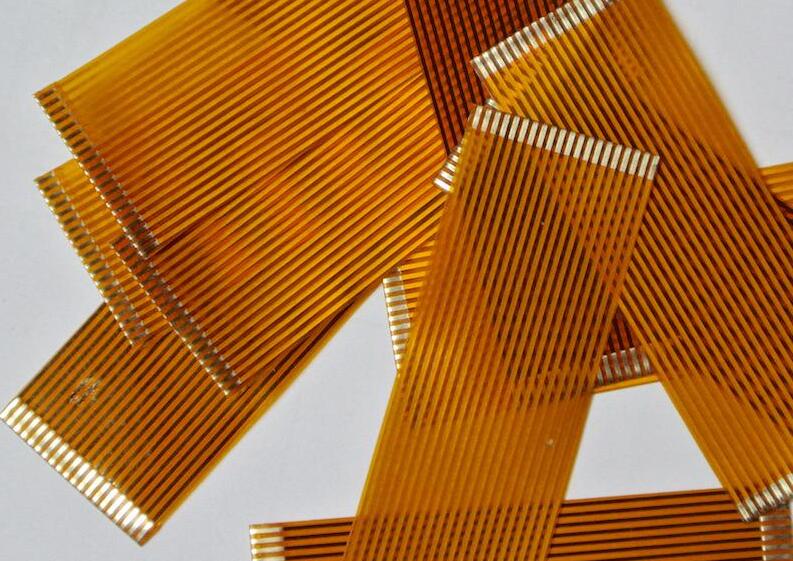

1. Sovrapposizione dei pad FPC

1.1. Sovrapposizione delle pastiglie di incollaggio (eccetto le pastiglie di incollaggio superficiale) significa fori sovrapposti, che possono causare la rottura della punta di trapano e danni ai fori durante il processo di perforazione a causa di forature ripetute in un unico luogo.

1.2. Due fori nella piastra multistrato si sovrappongono, ad esempio, un foro è il disco isolante e l'altro foro è il disco di collegamento (disco di incollaggio fiore). Di conseguenza, il negativo viene disegnato come disco isolante, con conseguente scarto.

2. Abuso del livello grafico

2.1. Alcune connessioni inutili sono state fatte su alcuni livelli grafici, ma sono state progettate linee con più di cinque livelli invece di quattro livelli, il che causa fraintendimenti.

2.2. I diagrammi del tempo di progettazione sono semplici. Prendiamo ad esempio il software Protel, per disegnare linee con il livello Board per ogni livello e per contrassegnare linee con il livello Board. Nei dati di disegno luminoso, quando il livello Board non è selezionato, le linee vengono perse e disconnesse o le linee vengono cortocircuitate perché è selezionata la linea di etichettatura del livello Board, in modo da mantenere l'integrità e la chiarezza del livello grafico durante la progettazione.

2.3. È scomodo violare la progettazione convenzionale, come la progettazione della superficie del componente nello strato inferiore e la progettazione della superficie di saldatura in alto.

3. Disordinamento dei caratteri

3.1. cuscinetti per saldatura SMD del cappuccio di carattere, che portano disagio alla prova della rottura dei pannelli stampati e della saldatura dei componenti.

3.2. Il disegno dei caratteri è troppo piccolo per rendere difficile la serigrafia e troppo grande per sovrapporre i caratteri, rendendo difficile la distinzione.

4. Impostazione dell'apertura unilaterale del pad di saldatura

4.1. i cuscinetti di incollaggio unilaterali generalmente non perforano fori. Se i fori devono essere contrassegnati, la dimensione del foro deve essere progettata per essere zero. Se viene progettato un valore numerico, la coordinata del foro apparirà in questa posizione e il problema si presenterà quando vengono generati i dati di perforazione.

4.2. l'etichettatura speciale dovrebbe essere fatta per i cuscinetti di incollaggio unilaterali come fori di perforazione.

5. Disegnare pad di incollaggio con blocchi di riempimento

I cuscinetti di disegno con blocchi di riempimento possono passare l'ispezione RDC nella progettazione del circuito, ma non è fattibile per l'elaborazione. Pertanto, tali pad non possono generare direttamente dati di resistenza. Quando si utilizza la resistenza superiore, l'area del blocco di riempimento sarà coperta dalla saldatura, il che rende difficile montare il dispositivo.

6. Strato elettrico è cuscinetto di legame del fiore e connessione

Poiché la fonte di alimentazione è progettata come un pad modellato, lo strato è opposto all'immagine sul circuito stampato effettivamente e tutte le connessioni sono linee di isolamento, su cui il progettista dovrebbe essere molto chiaro. A proposito, si dovrebbe prestare attenzione quando si disegnano set di linee di alimentazione o isolamento in diversi luoghi. Non devono essere lasciati vuoti per cortocircuito i due gruppi di alimentatori o bloccare l'area collegata (in modo che un insieme di alimentatori sia separato).

7. Definizione ambigua del livello di lavorazione

7.1. Il singolo pannello è progettato sullo strato superiore. Se il rovescio e l'avanti non sono specificati, il pannello può essere realizzato con componenti e non ben saldato.

7.2. Ad esempio, una scheda a quattro strati è progettata con quattro strati di fondo TOP mid1 e mid2, ma non viene inserita in questo ordine durante l'elaborazione, che richiede istruzioni.

8. Troppi blocchi di riempimento nel disegno o linee molto sottili che riempiono i blocchi di riempimento

8.1. Si verifica una perdita di dati di disegno della luce e i dati di disegno della luce sono incompleti.

Poiché i blocchi di riempimento sono disegnati uno ad uno nell'elaborazione dei dati di disegno luminoso, la quantità di dati di disegno luminoso generati è piuttosto grande, il che rende l'elaborazione dei dati più difficile.

9. Il pad di incollaggio del dispositivo di montaggio superficiale è troppo corto

Questo e' per il test on-off. Per i dispositivi montati in superficie troppo densi, la distanza tra i piedi è piuttosto piccola e il pad è molto sottile. Per installare il perno di prova, deve essere in una posizione sfalsata su-giù (sinistra-destra), ad esempio il design del pad è troppo breve, il che non influisce sull'installazione del dispositivo, ma non causerà il pin di prova a smarrirsi.

10. La spaziatura tra grandi griglie è troppo piccola

I bordi tra le linee che compongono una grande area di griglie sono troppo piccoli (meno di 0,3 mm). Nel processo di realizzazione dei circuiti stampati, il processo di conversione grafica è facile da produrre molte membrane rotte attaccate alle schede dopo lo sviluppo, con conseguente rottura della linea.

11. La grande area della lamina di rame è troppo vicina al telaio esterno

Una grande area di foglio di rame dovrebbe essere ad almeno 0,2 mm di distanza dal telaio esterno perché durante la fresatura della forma, come il foglio di rame, è facile causare la deformazione del foglio di rame e causare il problema di spargimento di flusso.

12. Design di bordo di forma ambigua

Alcuni clienti hanno progettato profili nello strato di mantenimento, strato di bordo, strato superiore sopra, ecc. e questi profili non sono coincidenti, il che rende difficile per il produttore di circuiti flessibili FPC determinare quale linea di profilo utilizzare.

13. Progettazione grafica irregolare

Il rivestimento irregolare causato dalla galvanizzazione grafica influisce sulla qualità.

Utilizzare le linee di griglia quando l'area di rame a 14 strati è troppo grande per evitare la formazione di bolle durante l'elaborazione della patch SMT.