Il fattore di restrizione principale del sistema di prova delle funzioni online del PCB è che la capacità del driver inverso di assorbire / scaricare la corrente è troppo forte, coprendo così il fenomeno di guasto del pin di ingresso del chip in prova. Ad esempio, l'impedenza del pin di ingresso della maggior parte dei chip è molto alta (superiore a 1 megaohm). Se la funzione interna del pin di ingresso è danneggiata, l'impedenza del pin può essere ridotta a circa 20 ohm, il che causerà problemi di fan-out nel chip che guida il pin di ingresso, guasto del circuito si verifica perché la maggior parte dei chip può guidare solo la corrente di uscita di circa 10 mA. che consente a un chip con un pin di ingresso difettoso di superare la prova funzionale. QT200 può guidare nodi superiori a 8 ohm (meno di 8 ohm sono considerati cortocircuiti), che è il problema principale di questo sistema.

Motivi del fallimento della prova PCB:

Funzione chip danneggiata

Problemi relativi alla velocità e alla tempistica

Stato del perno del chip (galleggiante, alta impedenza,

Orologio, connessione illegale)

Linea o stato della porta OC

Problema di diffusione

Classificazione dei risultati delle prove ICFT

Prova superata

Test fallito

Il dispositivo non è completamente testato

I dispositivi sono gli stessi

Il confronto dei dispositivi non è lo stesso

(2) Come trattare con i risultati differenti della prova PCB

Quando appare il risultato "test fallito"

Verificare se il dispositivo di prova è collegato al chip sbagliato e se è ben collegato al chip testato. Verificare se c'è un pin aperto (display HIZ) dalla finestra di stato del pin e se il pin di alimentazione è rilevato. Ripetere il test dopo aver corretto questi problemi.

Se il risultato è ancora "test failed", spostare il mouse alla finestra di stato del pin e fare clic sul pulsante sinistro per visualizzare l'impedenza del pin. Confrontare l'impedenza del perno con l'errore con l'impedenza di un altro perno con la stessa funzione. Se si verifica un errore di prova su un determinato pin di uscita del chip, verificare se l'impedenza di questo pin è coerente con altri pin di uscita (notare che l'impedenza in questo momento è l'impedenza a terra misurata quando il chip è alimentato).

Se le impedenze confrontate sono approssimativamente uguali, abbassare la base temporale o il valore soglia della prova e quindi riprovare. Se il test passa questa volta, significa che l'errore di test del chip è un problema di temporizzazione. Questo può essere che il pin di uscita è collegato a un dispositivo capacitivo. A causa del processo di scarica del condensatore, lo stato del pin di uscita diventa più lento. Se il test dopo aver regolato la base temporale o il valore di soglia può passare, puoi essere sicuro del 90% che il dispositivo non è danneggiato e puoi andare a testare il chip successivo in questo momento.

Se la prova continua a fallire dopo aver regolato la base temporale o la soglia, verificare se è necessario isolare. Se l'isolamento non è necessario, passare direttamente al punto 5.

Se si può vedere dallo stato del dispositivo che la ragione del fallimento della prova è che il pin di uscita non può raggiungere il livello logico normale, quindi abbassare la soglia di prova e provare di nuovo. Se la prova con un valore di soglia allentato può passare in questo momento, significa che il carico collegato al chip è troppo pesante, o la capacità di azionamento in uscita del chip stesso è deteriorata e non può assorbire o scaricare la corrente richiesta dal carico normale. Quando ciò accade, l'utente deve prestare particolare attenzione. La soluzione consiste nel ri-testare l'impedenza del perno di uscita al suolo quando la scheda in prova è accesa o meno. È inoltre possibile utilizzare il metodo QSM/VI sulla scheda in esame. Prova la curva VI di ogni pin di uscita del chip sotto i due stati di accensione e spegnimento.

Confronta l'impedenza misurata di ogni pin di uscita a terra. Se l'impedenza misurata senza alimentazione è approssimativamente la stessa e l'impedenza del pin di uscita con un errore di prova è superiore all'impedenza degli altri pin di uscita quando la potenza è accesa, significa che la funzione del chip è danneggiata (alta impedenza Lo stato non può assorbire o scaricare la corrente richiesta), il chip deve essere sostituito.

Confrontando le curve VI di ogni pin di uscita, se l'impedenza di un certo pin di uscita è significativamente inferiore all'impedenza di altri pin di uscita, significa che il problema risiede nel carico fan-out collegato a quel pin. Rilevare l'impedenza di tutti i pin di ingresso chip collegati a questo pin e scoprire il punto di cortocircuito reale.

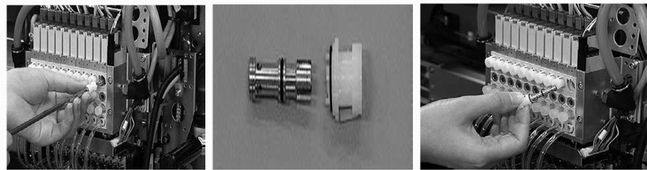

Per scoprire ulteriormente la causa principale del problema, le pinze a naso piatto possono essere utilizzate per bloccare i perni di uscita sul chip testato che hanno un errore di prova e quindi ripetere il test. Se il test passa in questo momento, indica che è davvero un problema con il carico collegato al chip.

2 Quando appare il risultato del "dispositivo non completamente testato"

Quando il pin di uscita del chip testato non gira durante il test (cioè, mantenere un potenziale fisso alto o basso nella finestra di test), il sistema chiederà "il dispositivo non è completamente testato" (la finestra della forma d'onda sullo schermo non appare quando viene visualizzato il prompt) Segnare eventuali errori di test). Ad esempio, un pin di ingresso di un gate NAND 7400 è accorciato a terra, il pin di uscita corrispondente sarà sempre alto e il prompt di cui sopra apparirà durante il test del chip.

Se l'utente ha il diagramma schematico PCB della scheda in prova, può facilmente determinare se lo stato di connessione pin del chip è normale.

Se l'utente ha imparato una buona scheda, verrà registrato anche lo stato di connessione normale del chip appreso. Quando si prova una scheda difettosa, il sistema confronta automaticamente il risultato di apprendimento con una buona scheda. Se il risultato del confronto è diverso, significa che la scheda difettosa ha una connessione illegale; Se il risultato del confronto è lo stesso, è possibile ignorare il prompt "dispositivo non completamente testato" e andare a testare il chip successivo.

Se il chip in esame è un dispositivo OC ed è progettato come uno stato "wire-OR" sul circuito PCB, l'uscita del chip può essere influenzata da altri chip che hanno una relazione wire-OR con esso. Ad esempio, se la logica di ingresso di un certo chip rende la sua uscita fissa a basso livello, anche l'uscita del chip testato sarà fissata a basso livello. In questo momento, il test del sistema chip richiederà anche "il dispositivo non è completamente testato". Gli utenti di tali dispositivi dovrebbero prestare particolare attenzione ad esso. Si consiglia di utilizzare il metodo QSM / VI per giudicare il punto di errore PCB confrontando le curve VI di tutti gli stessi pin di funzione sul chip di prova.