スイッチング電源の共通の問題は「不安定」スイッチング波形である. 時々, 波形ジッタはサウンドバンドにある, そして、磁気コンポーネントは、オーディオノイズを生成します. 問題がプリント回路基板のレイアウトにあるならば, 原因を見つけるのは難しいかもしれない. したがって, 正しい PCBレイアウト スイッチング電源の初期段階では非常に重要である. 電源設計者は、最終的な製品の技術的な詳細と機能的な要求を十分に理解しなければならない.

良いレイアウト設計は、電力効率を最適化して、熱ストレスを減らすことができます;さらに重要なことは、ノイズとトレースとコンポーネント間の相互作用を最小限に抑えます。これらの目標を達成するためには、設計者は、スイッチング電源内の電流伝導経路と信号流を理解しなければならない。非絶縁スイッチング電源の正しいレイアウト設計を実現するためには,以下の設計要素を念頭に置く必要がある。

非絶縁スイッチング電源のPCBレイアウト設計のヒントは何か

レイアウト計画?

キーは、システムの初期の設計および計画段階で、電力供給の場所およびボードスペースの需要を計画することである。時には、デザイナーは、このアドバイスを無視し、大規模なシステムボード上の“重要”または“エキサイティングな”回路に焦点を当てる。電力管理は余波とみなされ,電源は回路基板上の余分な空間に置かれる。このアプローチは、高効率で信頼性の高い電源設計に非常に有害である。

多層基板では、高電流電力成分層と高感度小信号トレース層との間にDC接地またはDC入出力電圧層を配置するのが良い方法である。接地層又は直流電圧層は、高雑音電力トレース及び電力構成要素からの干渉を防止するために、AC接地シールド小信号トレースを提供する。一般的に、多層PCBのグランドプレーン、直流電圧面は分離しない。この分離が避けられないならば、これらの層の上で跡の数と長さを減らしてください、そして、跡のレイアウトは影響を最小にするために高い流れと同じ方向に保たれなければなりません。

非絶縁スイッチング電源のPCBレイアウト設計のヒントは何か

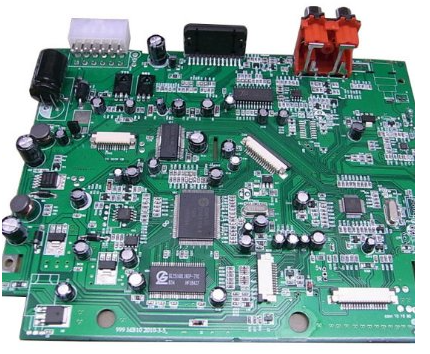

図示

これらの構造は、高電流電力層と接地層との間に小さな信号層を挟み、高電流/電圧パワー層とアナログ小信号層との間に結合された容量性ノイズを増大させる。

(b) and (d) are good structures for six-layer and 4層PCB デザイン, 層間の結合ノイズを最小化するのに役立つ, そして、基底層は、小さい信号レイヤーを遮蔽するために用いる.

外部の電力レベル層の隣にグランド層を配置し、PCBの伝導損失と熱抵抗を最小にするために、外部の高電流パワー層に厚い銅箔を使用してください。

パワーステージのレイアウト?

スイッチング電源回路は、電源段回路と小信号制御回路の2つに分けられる。パワーステージ回路は、大きな電流を伝送するために使用される構成要素を含む。一般的に、これらのコンポーネントを最初に配置する必要があり、次に、小さな信号制御回路をレイアウトの特定のポイントに配置する必要があります。PCBのインダクタンス、抵抗および電圧降下を最小にするために、高電流トレースは短くて広いべきである。高いdi/dtパルス電流を有するこれらのトレースに対し,このアスペクトは特に重要である。

同期バックコンバータ電流パス

非絶縁スイッチング電源のPCBレイアウト設計のヒントは何か

同期バックコンバータにおける連続電流路とパルス電流経路実線は連続した電流路を示し、破線はパルス(電流)電流経路を示す。パルス電流経路は、以下の構成要素に接続されたトレースを含む。

寄生インダクタンス

非絶縁スイッチング電源のPCBレイアウト設計のヒントは何か

Due to the parasitic inductance, パルス電流経路は磁場を放射するばかりでなく, しかし、PCBトレースとMOSFETの上に大きな電圧リンギングとスパイクを発生させます. 最小化するために PCBインダクタンス, the pulse current loop (the so-called thermal loop) should have the smallest circumference when laying out, そして、その跡は短くて広いべきです. 高周波デカップリングコンデンサCHFは0でなければならない.1・1・4・・・10・10・4分のF, X 5 RまたはX 7 R誘電体セラミックコンデンサ, it has very low ESL (effective series inductance) and ESR (equivalent series resistance). Larger capacitor dielectrics (such as Y5V) may cause the capacitance value to drop significantly at different voltages and temperatures, したがって、それはCHF.