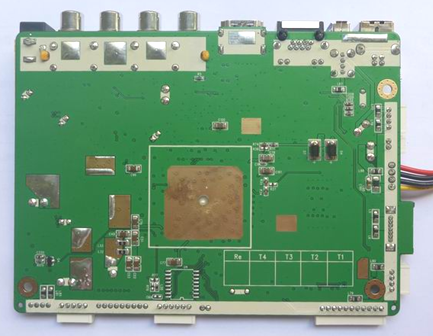

1. PCB基板メンテナンス 例

重要なヒント

チップピンが接地または電源に短絡されるとき、短絡抵抗値は10〜25ミリオームの間である。

長さ1インチの取付けられた銅線は、約40~50ミリオームの抵抗を有する。

例えば、74640がオンライン機能テストを実行するとき、そのピン6は接地への抵抗が1オームであることを示し、QT 50で測定された第6ピンの接地への抵抗は約160ミリオームである。それに接続された他のデバイスに起因する短絡故障であると考えられる。qt 50検査後,チップは抵抗バンクと設定スイッチに接続されていることが分かった。スイッチ接点で測定されたグランドに対する抵抗値は約40ミリオームであり、ピン6で測定された抵抗値よりも低いので、チップによって表示される接地へのピン6の短絡故障は、設定スイッチがグラウンドに接続されているためである。チップ自体の誤動作ではない。

通常の状況下では、バス装置のピンは、設計上の接地および電源を全く持っていない。ピン接地または電源がある場合は、再度デバイスをテストしてください。

参照と比較のために良いボードがない場合は、悪いボードはまた、ピンの状態と実際の測定波形を分析することによって修復することができます。例えば、多くのチップは、回路 基板設計において論理セルの一部を使用するだけであり、残りの未使用部分の入力ピンは、この部分がランダム動作状態にあることを防止し、回路に干渉を生じるのを防止するために一般的に接地される。チップの論理関数に従って実際の出力波形を解析することは、テストされたチップが本当に破損しているかどうかを判断するのに非常に役立つ。

例1:74123(単安定共振器)ピンが浮いている(FLT)

オンライン機能テストにおいて、デバイスの入力ピンは、一般に高インピーダンス状態(1メガオームより大きい抵抗値)として表示される。デバイスがオフラインでテストされると、TTLまたはCMOS負荷が接続されていない場合、この結果が表示されます。オンラインテストでは、チップの入力ピンは、通常別のチップの出力ピンに接続される。チップの出力ピンがファンアウト負荷を駆動することを確実にするために、通常は低インピーダンスである。

オンラインテストで, 入力ピンがピンステータスウインドウにを表示するならば, これは、ピンがフローティング状態にあることを意味します, そして、ピンは回路 基板またはトライステート装置の境界接続端に接続されてもよい, または、 PCB回路 基板.

他の入力ピンの状態と比較することにより、このピンの状態が正常か否かを判定することができる。

この例では、第6ピンはRC回路の入力端子に接続されている。回路のコンデンサは、抵抗器で充電されて、それからチップの第6のピンを経て吐き出した。高インピーダンスであれば、コンデンサを放電することができないので、入力ピンは高インピーダンス状態であることができない。チップ上でicftを実行したとき,テストエラーが発生した。第7ピンは「FLT」と表示され、他方の同じ入力ピン(ピン15)は通常の論理レベル(接地へのインピーダンスは約550オーム)を示した。チップ上のQT 200のテスト結果は「テスト不良」であるが、チップの出力ピンはフリップされるので、タイミング問題と考えられる。ユーザーが注意を払っていない場合、テスト結果は無視され、タイミングの問題と見なされます。

以上の解析により,ユーザは真の故障点を判断するのに非常に重要なピン状態情報を注意深く観察し解析することができる。入力ピンの入力インピーダンスが550オームである場合、それはフローティング状態(FLT)にない。この例の故障の実際の原因は、単安定共振器がその機能損傷によりコンデンサを正常に放電できないことである。

同様に、デバイスの出力ピンはフローティング状態(FLT)にできない。なぜなら、フローティング状態であれば、ピンは電流を吸収または放電することができず、任意のファンアウトロードを駆動することはできないからである。加えて、ユーザは注意を払うべきである:接地への任意のノードのインピーダンスは5~10オーム未満であることができない(ノードが実際に接地に短絡されない限り、インピーダンスはこのとき約2オームである)。一般的に使用されるバッファドライバは、ロジックロー状態で約15~17オームのインピーダンスを有する。

実施例2:テスタの電源器具は、接触不良により試験電力を供給することができない

テストボードの基板上にテスタの電源金具を介してテストボードに電源を供給すると、テスト中のチップの電源ピンの測定電圧は4.5 Vであり、このときのテスト結果は不安定であることがある。この理由は、テスタの電源固定部がチップピンと良好に接触しないように、チップピンの酸化によるものである。このような問題が発生すると、ユーザは異なる方法で解決できます。最も効果的な方法は、テスタの電源端子をテストボードの境界を介してテスタの電源ケーブルに接続することである。

例3:テストボードが電源を入れられたとき、チップのあるピンは接地に短絡される

この現象は解決するのが難しい。テスト結果は、テストされたチップの出力ピンのインピーダンスが10オーム(低インピーダンス状態)であり、フリップ動作がないことを示す。インピーダンスは、通常のバッファドライバ出力ピンのインピーダンスより小さい。テスト中のボードの電源を切断するとき、ピンが地面に短絡されていないことを測定するために3メートルを使用します(抵抗は1キロオームより大きいです)。

この短絡現象は、試験中のプリント基板が電源オンされたときのみ発生し、これは被試験デバイスの出力端の原因、または出力端に接続されたデバイスの入力端の原因である。テスト中のデバイスの出力端は、論理が低いときに電流を吸収することができなければならず、論理が高いときには、ファンアウト装置の入力ピンに電流を出力する。

テスト4ボードが電源オンされていない場合、3つのチップのピンの1つはすべて接地されます

電源が投入されたときに、試験中のデバイスが内部に接地されている場合、電源が印加されていない場合には、測定において接地への短絡はない。この場合、ミリオーム計を使用して、被試験デバイスの出力ピンの抵抗をグラウンドに接地し、接続されたファンアウト装置の入力ピンの抵抗を測定することができる。最も小さい抵抗を持つ測定点は、実際に破損した装置である。

特定の現象は、ICFTの間に「テスト失敗」を有する試験されたボードに3つのチップがあるということである。そして、バス・デバイス74374の第2のピン、74244の第18のピンおよび他の74244ピンはピンステータス・ウィンドウにおいて、表示される。ピン3はそれぞれ接地されている。

最初に、PCB短絡点に最も近いチップを見つけてください。テスト用のQT 50ショートトラッカーを使用する場合は、測定範囲を200ミリオームに設定し、3つのチップの短絡ピンの接地抵抗を測定し、最低抵抗でピンを見つける。方法は、1つのプローブを試験中の基板の電源グラウンドに接続し、他方のプローブを74374の第2ピンに接続し、測定された抵抗が160ミリオームであり、次いで74244の第18ピンに接続され、抵抗が90ミリオームであることを測定し、それから別の74244の第3ピンに接続され、測定された抵抗が10ミリオームである。そして、このピンはバスエラーを引き起こした短絡点である。

以下の質問は、本当の短絡点が74244の内側か、または PCB基板短絡ピン. 方法は以下の通りです:QT 50の1つのプローブを地面に使用してください, そして、74244の第3のピンのハンダ接合部より上の部分に、他のプローブを接続する, このピンの対地抵抗(約10ミリオーム)を読み取り、そして、3.番目のピンのはんだ接合部の外側に3~4 mmの接続された銅線にプローブ・ペンを接続します, そして、このときの第3ピン対接地の抵抗値(約6ミリオーム)を読み出す。この結果は、実短絡点がピン3.に取り付けられた外部銅線であることを示している.