Ethernet was born in the 1970s, and we are no stranger to it today. It has emerged in every corner of modern life. Perhaps it is because of its ubiquity that makes it mysterious. Today, the editor of the circuit board factory will One of the angles unveiled its mystery.

The network interfaces we use today are all Ethernet interfaces, and most processors currently support Ethernet interfaces. At present, Ethernet mainly includes three interfaces of 10M, 10/100M, and 1000M according to the rate. 10M applications have been very few, and they are basically replaced by 10/100M. At present, the Ethernet interface type of our products mainly adopts the twisted pair RJ45 interface, and it is basically used in the industrial control field. Due to the particularity of the industrial control field, we are quite sophisticated in the selection of Ethernet devices and PCB design. From a hardware point of view, the Ethernet interface circuit is mainly composed of MAC (Media Access Controlleroler) control and physical layer interface (Physical Layer, PHY). Most processors include Ethernet MAC control, but do not provide a physical layer interface, so an external physical chip is needed to provide an Ethernet access channel. Faced with such a complicated interface circuit, I believe all hardware engineers want to know how the hardware circuit is implemented on the PCB.

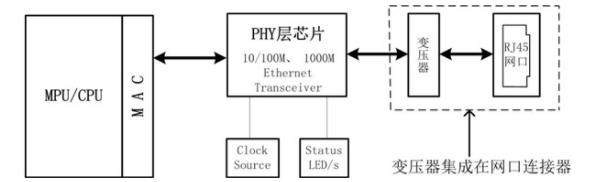

Figure 1 shows a typical application of Ethernet. Our PCB design is basically laid out and routed according to this block diagram. Now we will use this block diagram to explain in detail the main points of Ethernet-related layout and routing.

Figure 1 Typical application of Ethernet

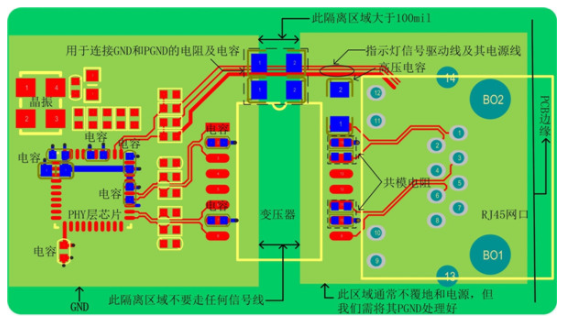

1. Figure 2 The PCB layout and wiring diagram of the reference circuit of the network port transformer not integrated in the network port connector. The following figure 2 introduces the points that need to be paid attention to the layout and wiring of the Ethernet circuit.

Figure 2 PCB layout and wiring reference of the circuit where the transformer is not integrated in the network port connector

a) The distance between the RJ45 and the transformer should be as short as possible. The crystal oscillator should be far away from the interface, the edge of the PCB and other high-frequency devices, traces or magnetic components. The distance between the PHY layer chip and the transformer should be as short as possible. Considering the overall layout, this may be more difficult to satisfy, but the maximum distance between them is about 10~12cm. The principle of device layout is usually to place according to the signal flow direction, and must not go around;

b) The power filter of the PHY layer chip is designed in accordance with the requirements of the chip. Usually, a decoupling capacitor is placed on each power terminal. They can provide a low impedance path for the signal and reduce the resonance between the power supply and the ground plane. Play the role of decoupling and bypass, so it is necessary to ensure that the loop area composed of capacitors, traces, vias, and pads of decoupling and bypass capacitors is as small as possible, and the lead inductance is as small as possible;

c) The filter capacitor of the center tap of the chip side of the PHY layer of the network port transformer to the ground should be as close as possible to the transformer pin to ensure the shortest lead and the smallest distributed inductance;

d) The common mode resistance and high voltage capacitor on the interface side of the network port transformer are placed close to the center tap, and the wiring is short and thick (≥15mil);

e) The two sides of the transformer need to cut ground: that is, the RJ45 connection base and the secondary coil of the transformer use a separate isolated ground, the isolation area is more than 100mil, and there is no power supply and ground layer under this isolation area. This segmentation process is to achieve the isolation between the primary and the secondary, and the interference from the control source is coupled to the secondary through the reference plane;

f) The power line of the indicator light and the drive signal line are routed adjacent to each other to minimize the loop area. The indicator light and the differential line should be separated as necessary, and the two should be kept at a sufficient distance. If there is space, it can be separated by GND;

g) The resistors and capacitors used to connect GND and PGND should be placed in the ground division area.

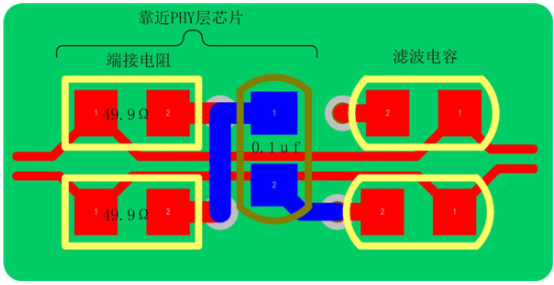

2. Ethernet signal lines are in the form of differential pairs (Rx±, Tx±). Differential lines have strong common mode rejection and strong anti-interference ability, but if the wiring is improper, it will bring serious signal integrity. Sexual issues. Let's introduce the processing points of the differential line one by one:

a) Give priority to drawing Rx±, Tx± differential pairs, try to keep the differential pairs parallel, equal length, and short distance, and avoid vias and crosses. Due to factors such as pin distribution, vias, and wiring space, the length of the differential line is likely to be mismatched, the timing will be shifted, and common mode interference will be introduced, which will reduce signal quality. Therefore, it is necessary to compensate for the mismatch of the differential pair to match the line length. The length difference is usually controlled within 5mil. The compensation principle is where the length difference is compensated;

b) When the speed requirement is high, impedance control of Rx±, Tx± differential pair is required, usually the impedance is controlled at 100Ω±10%;

c) Differential signal terminal resistance (49.9Ω, some PHY layer chips may not) must be placed close to the Rx± and Tx± pins of the PHY layer chip, which can better eliminate signal reflection in the communication cable;

d) The filter capacitors on the differential pair must be placed symmetrically, otherwise the differential mode may be converted to common mode, causing common mode noise, and there must be no stubs when routing, so as to have good suppression of high frequency noise.

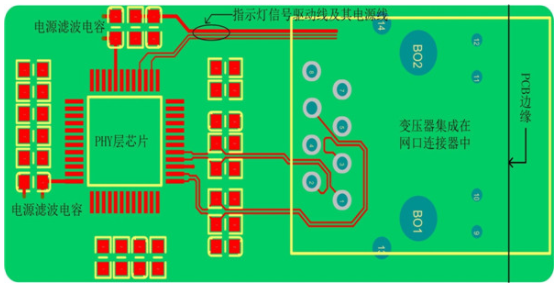

3. The PCB layout and wiring of the Ethernet circuit with the transformer integrated in the connector are much simpler than those without integration. Figure 3 below is the PCB layout and wiring reference diagram of the network port circuit with the integrated connector:

Figure 3 Network port PCB layout and wiring reference diagram of the integrated connector

As can be seen from the above figure, the difference between Figure 3 and Figure 1 is that the network port transformer is omitted, and the others are roughly the same. The difference is mainly reflected in the network port transformer has been integrated into the connector, so the ground plane does not need to be divided, but we still need to connect the shell of the integrated machine to a continuous ground plane.

The Ethernet layout and routing are roughly the same. A good PCB layou t can not only ensure circuit performance, but also improve circuit performance.