How to standardize PCB chip component package pads

When drawing component packaging in PCB, we often encounter the problem that the size of the pad is not easy to grasp, because the information we consulted gives the size of the component itself, such as pin width, spacing, etc., but on the PCB board The size of the corresponding pad should be slightly larger than the size of the pin, otherwise the reliability of soldering will not be guaranteed. The following will mainly talk about the specification of the pad size.

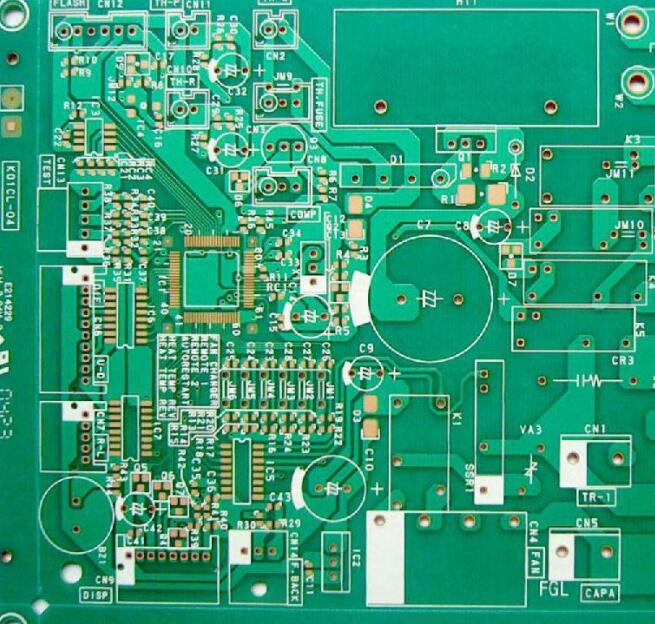

In order to ensure the soldering quality of the chip components (SMT), when designing the SMT printed board, in addition to the 3mm-8mm process edge of the printed board, the land pattern and size of various components should be designed according to relevant specifications. In addition to arranging the position of the components and the spacing between adjacent components, we believe that special attention should be paid to the following points:

(1) On the printed circuit board, all the conductive patterns (such as interconnection wires, ground wires, mutual conductive vias, etc.) and the copper foil required to be reserved under the solder mask should be bare copper foil. That is, metal coatings with a melting point lower than the soldering temperature, such as tin-lead alloys, are never allowed to avoid cracking or wrinkling of the solder mask at the coating layer, so as to ensure the soldering and appearance quality of the PCB board.

(2) When selecting or calling the land pattern size data, it should match the size of the package, solder ends, pins, etc. related to the soldering of the components you have selected. It is necessary to overcome the bad habit of copying or calling the data J or the size of the pad pattern in the software library at will without analysis or comparison. When designing, selecting or calling the size of the pad pattern, you should also distinguish the components you have selected, their codes (such as chip resistors, capacitors) and welding-related dimensions (such as SOIC, QFP, etc.).

(3) The soldering reliability of surface mount components mainly depends on the length of the pad rather than the width.

(A) As shown in Figure 1, the length B of the pad is equal to the length T of the solder end (or pin), plus the extension length b1 of the inner side (pad) of the solder end (or pin), plus the solder end (Or pin) the extension length b2 of the outer side (pad), that is, B=T+b1+b2. Among them, the length of b1 (about 0.05mm-0.6mm) should not only facilitate the formation of a good meniscus profile solder joint when the solder is melted, but also avoid the solder bridging phenomenon and take into account the placement deviation of the components. ; The length of b2 (approximately 0.25mm-1.5mm) is mainly to ensure that the solder joints with the best meniscus contour are formed (for SOIC, QFP and other devices, the ability of the pad to resist peeling should also be taken into account).

Picture 2.jpg

Pad length B=T+b1+b2

Inner pad spacing G=L-2T-2b1

Land width A=W+K

The distance between the outside of the pad is D=G+2B.

Where: L-component length (or the distance between the outer sides of the device pins);

W-component width (or device pin width);

H-component thickness (or device pin thickness);

b1-The extension length of the inner side (pad) of the solder end (or pin);

b2-the extension length of the outer side (pad) of the solder end (or pin);

K-pad width correction amount.

Typical value of extension length of common component pad:

For rectangular chip resistors and capacitors:

b1=0.05mm, 0.10mm, 0.15mm, 0.20mm, 0.30mm. The shorter the component length, the smaller the value should be.

b2=0.25mm, 0.35mm, 0.5mm, 0.60mm, 0.90mm, 1.00mm, the thinner the component thickness, the smaller the value should be.

One of K=0mm, +-0.10mm, 0.20mm, the narrower the component width, the smaller the value should be.

For SOIC and QFP devices with airfoil pins:

b1=0.30mm, 0.40mm, 0.50mm, 0.60mm, the smaller the device shape, or the smaller the center distance between adjacent pins, the value should be smaller.

b2=0.30mm, 0.40mm, 0.80mm, 1.00mm, 1.50mm. For the larger device shape, the value should be larger.

K=0mm, 0.03mm, 0.30mm, 0.10mm, 0.20mm, the smaller the center distance between adjacent pins, the smaller the value should be.

B=1.50mm~3mm, generally about 2mm.

It can be as long as possible if the outer space allows.

(4) Through holes are not allowed in the pad and at the edge (the distance between the edge of the through hole and the pad should be greater than 0.6mm), if the through hole disk and the pad are interconnected, it can be less than the width of the pad 1/2 connection, such as 0.3mm ~ 0.4mm to be interconnected to avoid various soldering defects caused by solder loss or thermal isolation.

(5) In the pads used for soldering and testing, it is not allowed to print logo symbols such as characters and graphics; the distance between the logo symbols and the edge of the pad

The distance should be greater than 0.5mm. In order to avoid all kinds of soldering defects caused by the printing material soaking the pad and affecting the accuracy of the inspection.

(6) There should be a section of thermally isolated lead for the connection between the pads, between the pad and the through-hole pad, and between the pad and the interconnection line larger than the width of the pad or the large-area grounded or shielded copper foil. The width of the line should be equal to or less than one-half of the width of the pad (the smaller one shall prevail, the general width is 0.2mm ~ 0.4mm, and the length should be greater than 0.6mm); if a solder mask is used to cover, Its width can be equal to the width of the pad (such as the connection with a large area ground or shielded copper foil).

(7) For the same component, all pads that are used symmetrically (such as chip resistors, capacitors, SOIC, QFP, etc.) should be designed to strictly maintain their overall symmetry, that is, the shape and size of the pad pattern are exactly the same (When the solder is melted, the soldering area formed is equal) and the position of the shape of the pattern should be completely symmetrical (including the position of the interconnection line drawn from the pad; if it is blocked by a solder mask, the interconnection line can be random). To ensure that when the solder melts, the surface tension acting on all solder joints on the components can be balanced (that is, the resultant force is zero), so as to facilitate the formation of ideal high-quality solder joints.

(8) Any soldering pads of components without external pins (such as chip resistors, capacitors, adjustable potentiometers, adjustable capacitors, etc.) are not allowed to have through holes between the pads (that is, there must be no underside of the component body). Through holes; except for those blocked with solder mask) to ensure the cleaning quality.

(9) For multi-pin components (such as SOIC, QFP, etc.), the short connection between the pin pads is not allowed to pass through, and the pad should be added to the interconnection line before the short connection (if solder mask is used) The film is shielded can be excluded) to avoid displacement or be mistaken for bridging after welding. In addition, try to avoid crossing the interconnection lines between the pads (especially the finely spaced pin devices); any interconnection lines that pass between adjacent pads must be shielded by a solder mask .

(10) For multi-pin components, especially those with a pitch of 0.65mm and below, a bare copper reference mark should be added on or near the land pattern (such as on the diagonal of the land pattern, add Two symmetrical bare copper optical positioning marks) are used as optical calibration for precise placement.

(11) When using the wave soldering process, the through hole on the pad of the pin should generally be 0.05 ~ 0.3mm larger than the lead wire diameter, and the diameter of the pad should not be greater than 3 times the aperture. In addition, for the land patterns of IC and QFP devices, it is necessary to add process auxiliary pads that can drag the molten solder to avoid or reduce the occurrence of bridging.

(12) Any pad used for soldering surface mount components (that is, at the soldering point) must never be used as a test point; in order to avoid damage to the components, special test pads must be designed separately. To ensure the normal progress of welding inspection and production debugging.

(13) All the pads used for testing should be arranged on the same side of the PCB as far as possible. This is not only convenient for testing, but more importantly, it greatly reduces the cost of testing (this is especially true for automated testing). In addition, the test pad should not only be coated with tin-lead alloy, but its size, spacing and layout should also match the relevant requirements of the test equipment used.

(14) If the size of the component is the maximum and minimum value, the average value of its size can be used as the basis of the pad design.

(15) Use a computer to design. In order to ensure that the designed graphics can reach the required accuracy, the size of the selected grid unit must be matched with it; for the convenience of drawing, all graphics should fall on the grid as much as possible Point. For multi-pin and fine-pitch components (such as QFP), when drawing the center spacing of its pads, not only the grid unit size must be 0.0254mm (ie 1mil), but also the origin of the coordinate drawn should always be set At its first pin. In short, for multi-pin fine-pitch components, when designing the pads, it should be ensured that the total cumulative error must be controlled within

Within +-0.0127mm (0.5mil).

(16) The designed various pads should be used together with the carrier PCB, and can be formally used for production only after passing the test welding and testing. This is especially true for mass production.