Flexible and Rigid - Superspeed on flexible PCB board is inevitable as these boards are increasingly used in electronics. These systems also require ground layers for isolation and to separate RF and digital references for wireless protocols. The high speeds and frequencies create the potential for signal integrity problems, many of which are related to the location and geometry of the grounding layers in a PCB.

A common method of providing a consistent 0V reference on flexible and rigid-flexible plates is to use a Shadowed line or grid-like ground plane on a flexible ribbon. This provides large conductors that can still provide shielding over a wide frequency range, while still allowing flexible bands to bend and fold without creating excessive rigidity. However, signal integrity problems arise in two areas:

Ensures consistent wiring impedance, shielding and isolation, and prevents effects similar to fiber braiding in hatch structures.

Grid floor plan design

In a basic sense, a profile works like any other ground plane. It is intended to provide a consistent reference so that traces can be designed to have the desired impedance. Any common transmission line geometry (microstrip line, ribbon line, or waveguide) can be placed in a hard or flexible PCB with a netted ground plane. Copper areas where shadow lines are placed on the surface layer of the flexible band provide nearly the same effect as low frequency solid copper.

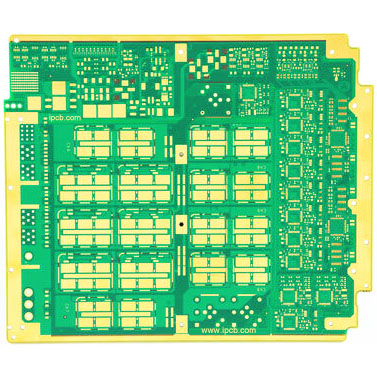

A common configuration for strip and microstrip wiring on a flexible strip with a network ground plane is shown below.

A grid grounded plane pattern on an elastic ribbon.

This mesh structure can be used on rigid boards, but I've never actually seen it, nor have clients requested it. Instead, mesh patterns are used in flexible/rigid-flexible plates to balance the need for impedance control with the need for a reasonable flexible band. Whether you are designing traces or pattern filling patterns, follow the practice of static and dynamic flexible ribbons as well as IPC 2223 standards.

Impedance control

One option to use a single end or differential pair is to place the solid copper in a flat layer directly below the wiring and place the mesh elsewhere in the circuit. If routing becomes very dense, you will need to use the grid everywhere. If a grid is chosen, there is greater flexibility, but the shielding isolation is lower, and impedance control conditions change.

As shown above, the grid plane structure has two geometric parameters: L and W. These two parameters can be combined as a fill factor or as part of the area of the grid covered by copper. Changing these parameters has the following effects:

Opening the grid region (increasing the grid opening by increasing L) increases the impedance, assuming other parameters remain constant. This also makes the ribbon easier to bend (with less force).

Increasing W while holding other parameters constant will close the grid area and thus increase the impedanc

e. This also makes the ribbon pattern harder to bend (with more force).

Other parameters that control the impedance of the standard geometry have the same effect when a grid grounding plane is used. After entering high frequency, you will excite non-TEM patterns around the transmission line and may even see an effect similar to fiber weaving.

Does the Flex carbon strip have fiber braiding?

This is where the grid grounding plane on a PCB is very interesting, because the grid pattern can start to resemble the glass woven pattern used in FR4 and other laminates. As a result, we are now back to a situation where we have to worry about fiber weaving in a normally smooth, relatively uniform substrate. These effects occur when the bandwidth of the traveling signal overlaps with one or more resonances in the mesh. For L = 60 mil on polyimide, the order resonance will be 50 GHz.

These Shadowed line structures can generate strong radiation as the digital signal propagates along the track of the grid grounding plane, whether on rigid PCB or flexible PCB substrate. With more and more Flex applications opening at a higher frequency, FOR some reason I expected these effects to get worse in Flex ribbons with grid-grounded planes.

High Q resonant

As in conventional glass-woven substrates, the mesh forms a cavity structure that can support resonance when excited at a specific frequency. These resonant cavities in the grid ground plane will have very high Q values because the walls of the cavities are highly conductive (copper). Therefore, it will have lower loss and higher Q resonance. This results in increased cavity emission and resonant power losses.

Open grid has low isolation

The reticulated ground plane usually ensures that any radiated EMI emanating from the fiber-braided cavity is emitted along the edge of the plate. Because the grid has open cavities, it is less isolated and can also radiate along the surface of the flexible carbon band. This has the opposite effect: while wiring is more likely to emit radiation, it is also more susceptible to external EMI.

To solve these problems, use a tighter mesh, just as tighter glass braiding is used to prevent fiber braiding effects. Flexible and Rigid - Flexible PCBS will continue to be part of the PCB landscape and become more advanced with newer manufacturing capabilities.