A popular way to solve the high-density interconnect (HDI) problem is to start with a simple printed circuit board and add it layer by layer. This is called a sequential lamination process. For balance, layers are always added in pairs to the top and bottom. We have a symbol to describe the sequence.

A typical example is a board, which starts with the N layer in the initial pressing, and then has three additional lamination steps. Every extra

For each electroplating line, there are four drilling rigs and one printer. In between these two are some of the most expensive equipment in the factory. These items will be printing presses. Or, maybe in the case of smaller stores, news. News is the bottleneck. This is the main reason why the sequential construction takes longer and the cost is higher. Arrange to visit local suppliers. The ratio of the press to the drilling station will indicate whether they focus on through-hole or high-density boards.

Printing plants with sufficient bandwidth can deliver on 3N3 boards while maintaining the capacity of other parts of the plant. This level of technology is sufficient for most applications. Smart phones require a stack of micro-vias that run through the entire circuit board. This is the function of their chipset and tightly packed to make way for the battery. Their factory floor will reflect these needs.

The core of the problem-starting from the through hole

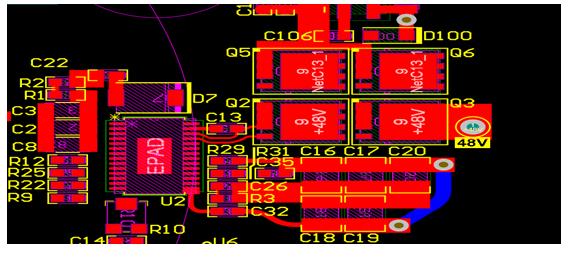

Except for the lack of solder mask and silk screen, the "simple board" is complete. The core will have at least two layers, but usually more. We talk about core and prepreg materials, but this is slightly different from the definition of "core". Our core can be two layers, in which case there will be overlapping definitions. Even if it is a core with an additional layer of prepreg, we will still call it the core. If required by the design, what will eventually become the core through hole will be a hole through the stack of multiple pieces of core material. In this case, the core is the product of the first lamination cycle.

Squeeze more from the core hole

Emphasizing the fact that core vias start from vias, the same electroplating process is required to deposit copper in the holes. This translates into using a larger minimum air gap and line width consistent with the constraints of the outer layer and the typical inner layer.

Knowing that thicker copper favors wider geometries, it makes sense to dedicate these layers to power and ground networks, and they happen to also benefit from thick copper and wide geometries. Naturally, the middle layer is a candidate for fine-wire wiring.

When the number of floors becomes busy, there are bound to be multiple sub-boards stacked together, so from the perspective of routing, the core via span is more like a local elevator. Grouping the bus and related power domains into dedicated sections will reduce cross-contamination on these epic high-level digital boards.

If the core is a multi-layer stack, you can create some micro-vias in the core before adding the first pair of additional layers in sequence. You only need to use a thin dielectric on the outer layer to make micro-vias. You will get a micro-via that does not increase the lamination cycle. It's like looking for money!

Many chips are not built for low-key circuit boards. Pushing it to the limit of the same network via pitch is to make the blind/buried vias and the capture pads of the core vias tangent to each other; contact but not overlap.

Be careful of excessive use of the transition layer. It will be busy with small snowman-shaped via pairs, so it is easy to squeeze them together. The space under fine pitch ball grid array (BGA) devices can be quite precious, so it is best to minimize their use under the device to those connections through the board, such as bypass caps or some other convincing reason. Route away from the device on a layer accessible through microvias, and then jump through larger vias, where there is more space for them to use.

Stitch vias for strong return path and EMI suppression

Trending in the return path will involve many locations with ground via patterns. The earlier you understand these details, the easier it will be to implement. Regardless of where the trace goes through the transition, there should be provisions for connecting the various reference planes together.

Need to create a heat dissipation path through the circuit board. Consider leaving some dielectric material to maintain a certain degree of impedance and structural integrity. Start with the concentration around the source, but spread out as the vias connect to the other side of the circuit board. I have never done this before, but I don't understand why you can't use thermal paste with filler to increase the dissipation factor.