L'apparition initiale du boîtier au niveau de la plaquette a été stimulée par la fabrication de composants d'E / s et de transistors à faible vitesse pour téléphones portables, tels que des capteurs sur puce passifs et des circuits intégrés de transmission de puissance. Actuellement, WLP est dans une phase de développement, stimulée par des applications telles que Bluetooth, GPS et carte son, et la demande augmente progressivement. Alors que l'industrie évolue vers la phase de production des téléphones 3G, diverses nouvelles applications pour les téléphones mobiles devraient être un autre moteur de croissance pour WLP, y compris les tuners de télévision, les émetteurs FM et les mémoires à pile. Au fur et à mesure que les fabricants d'équipements de stockage mettront en œuvre le WLP, cela conduira à une transformation standardisée dans l'ensemble de l'industrie.

Actuellement, cette technologie est largement utilisée dans divers domaines tels que les mémoires flash, EEPROM, DRAM haute vitesse, SRAM, lecteurs LCD, dispositifs RF, dispositifs logiques, dispositifs de gestion d'alimentation / batterie et dispositifs analogiques (régulateurs, capteurs de température, contrôleurs, amplificateurs opérationnels, amplificateurs de puissance). L'Encapsulation au niveau de la plaquette utilise principalement deux techniques de base: la redistribution du film mince et la formation de billes. Le premier est destiné à transformer des zones de jonction réparties le long de la périphérie de la puce en zones de jonction en Plots réparties en matrice plane sur la surface de la puce. Ce dernier est utilisé pour créer des bosses sur la zone de collage des bosses, formant un réseau de bosses.

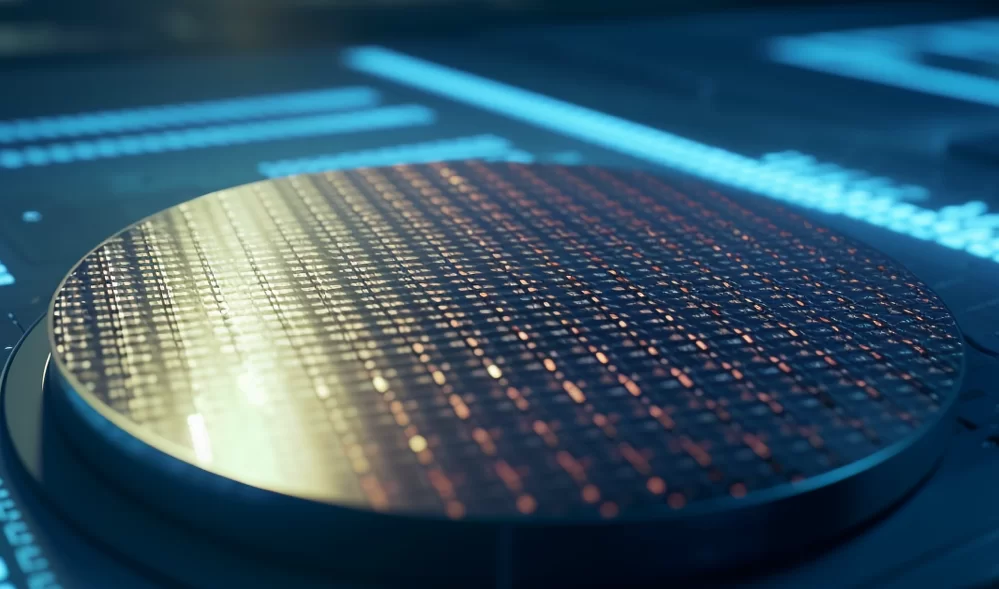

Encapsulation au niveau du Wafer

Actuellement, il existe trois chemins pour l'encapsulation au niveau de la plaquette: wlcsp, fowlp et PLP:

Wlcsp (Wafer level Chip Size Packaging), également connu sous le nom d'encapsulation sectorielle en WLP, est une méthode d'encapsulation traditionnelle utilisée pour la puce finale. Il convient aux circuits intégrés avec un petit nombre de broches. Comme le nombre de signaux de sortie IC augmente, la taille des billes de soudage devient plus stricte. Les PCB ne peuvent pas répondre aux exigences d'ajustement de la taille de l'IC encapsulé et de la position des broches de sortie de signal.

Le fowlp commence par les puces et les redistribue ensuite sur de nouvelles plaquettes artificiellement formées. Les avantages comprennent une épaisseur de boîtier réduite, un évent accru (plus d'interfaces E / s), de meilleures performances électriques et une meilleure résistance à la chaleur. Le fiwlp et le fowlp ont des applications différentes, mais ce sont tous deux des méthodes d'emballage majeures pour l'avenir. Le fiwlp est le plus largement utilisé pour les puces analogiques et à signaux mixtes, suivies par les interconnexions sans fil, et les capteurs d'image CMOS sont également encapsulés avec la technologie fiwlp. Fowlp sera principalement utilisé pour les puces de processeur dans les appareils mobiles.

Le PLP (Panel level Packaging) est similaire au fowlp, qui redistribue les puces sur des panneaux rectangulaires plus grands plutôt que sur des plaques rondes. Une plus grande surface signifie plus d'économies de coûts et une plus grande efficacité d'emballage. De plus, le découpage de la puce en carrés entraîne un gaspillage d'encapsulation de la plaquette, et un panneau rectangulaire peut résoudre efficacement ce problème. Cependant, cela impose également des exigences plus élevées en matière de lithographie et d'alignement. L'idée de base est de terminer la fabrication de la puce tout en Encapsulant directement la tranche de silicium, Encapsulant plusieurs unités de puce dans une structure d'encapsulation globale. Cela évite l'étape d'encapsulation individuelle de chaque puce dans un boîtier classique, ce qui augmente la productivité et réduit les coûts.

Le procédé d'encapsulation au niveau de la plaquette comprend généralement les étapes suivantes:

Préparation des plaquettes: les plaquettes de silicium sont lavées et préparées pour assurer la fiabilité et la cohérence du processus d'encapsulation.

Formation de la structure d'encapsulation: une couche de matériau d'encapsulation, généralement un polymère, est appliquée sur la Feuille de silicium pour former la base de la structure d'encapsulation.

Connexion de circuit: créez un fil métallique (connexion de fil) ou une autre structure de connexion de circuit sur une tranche de silicium pour connecter les circuits de la puce à la structure d'encapsulation.

Tests et vérification de la qualité: effectuer des tests de performance électrique, des tests d'intégrité de l'emballage, etc. pour s'assurer que les puces encapsulées répondent aux exigences de qualité.

Séparation des puces: les puces encapsulées sont séparées des tranches de silicium pour obtenir des puces encapsulées séparées.

WLP est basé sur la technologie BGA et est une forme améliorée et améliorée de CSP qui reflète pleinement les avantages techniques de BGA et CSP. Il présente de nombreux avantages uniques:

Haute efficacité de traitement d'encapsulation: fabriqué avec un processus de production en série sous forme de plaquettes.

Il hérite des avantages du boîtier à puce inversé, qui est léger, mince, court et petit.

Faible coût des installations de production: l'équipement de fabrication de puces peut être pleinement utilisé pour éviter d'avoir à investir dans des lignes de production d'encapsulation séparées.

Considérations de conception de puce et d'emballage unifiées: efficacité de conception améliorée et coûts de conception réduits.

Réduction des cycles de production: il réduit considérablement l'ensemble du processus, de la fabrication de la puce à l'encapsulation en passant par la livraison du produit, ce qui réduit les coûts.

Rentabilité: le coût du WLP est étroitement lié au nombre de puces par tranche. Plus il y a de puces sur la plaquette, moins son coût est élevé. Cet emballage est la méthode d'emballage minimale et la moins coûteuse.

L'avantage du WLP est qu'il s'applique à la technologie CSP (Chip level Packaging) pour les petits circuits intégrés. En utilisant des techniques d'encapsulation parallèle et de test électronique au niveau de la plaquette, WLP réduit considérablement la surface de la puce tout en augmentant le rendement. De plus, le coût par E / s est considérablement réduit par la connexion de puces conductrices parallèles au niveau de la plaquette. En outre, les procédures d'essai simplifiées au niveau du moule réduisent encore les coûts.

L'utilisation de l'encapsulation au niveau de la plaquette permet l'encapsulation et le test de la puce au niveau de la plaquette.