Первоначальное появление упаковки на уровне транзисторов было вызвано производством низкоскоростных I / O и низкоскоростных транзисторных компонентов для мобильных телефонов, таких как датчики на пассивных пластинах и IC передачи мощности. В настоящее время WLP находится на стадии разработки, движимой такими приложениями, как Bluetooth, GPS и звуковые карты, и спрос постепенно растет. По мере того, как индустрия переходит к производству телефонов 3G, новые приложения для мобильных телефонов, как ожидается, станут еще одним драйвером роста для WLP, включая телевизионные тюнеры, FM - передатчики и стеки памяти. По мере того, как производители устройств для хранения данных постепенно внедряют WLP, это приведет к стандартизированной трансформации всей отрасли.

В настоящее время эта технология широко используется в различных областях, таких как флэш - память, EEPROM, высокоскоростные DRAM, SRAM, LCD - накопители, устройства RF, логические устройства, устройства управления питанием / батареей и аналоговые устройства (регуляторы, датчики температуры, контроллеры, вычислительные усилители, усилители мощности). Упаковка на уровне кристалла в основном использует две основные технологии: перераспределение пленки и формирование выпуклых блоков. Первый используется для преобразования области соединения, распределенной вдоль периферии чипа, в область выпуклого соединения, распределенную в виде плоской решетки на поверхности чипа. Последний используется для создания выпуклых блоков в области сцепления выпуклых блоков, образуя выпуклые массивы.

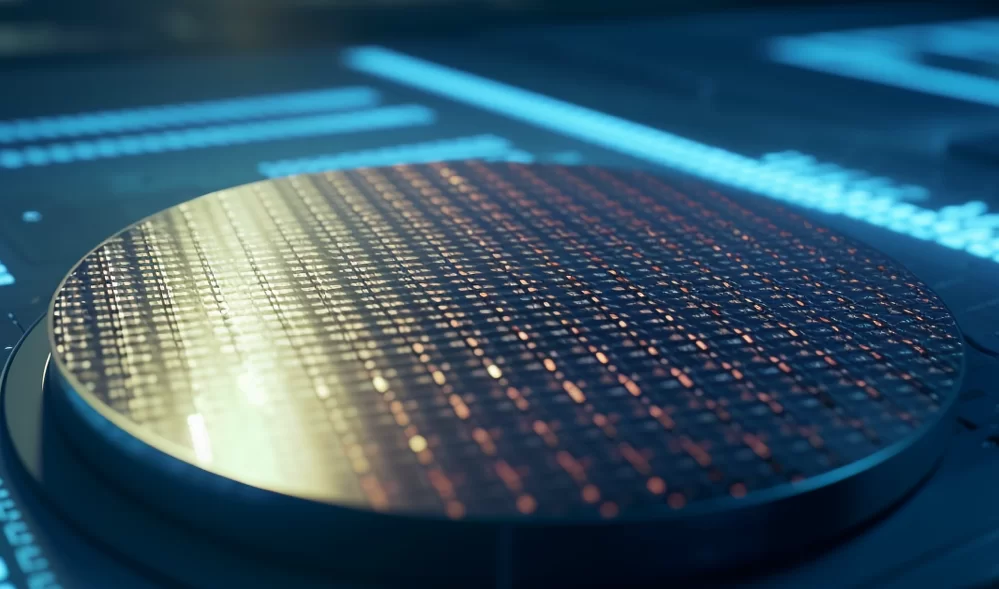

упаковка на уровне кристалла

В настоящее время существует три пути инкапсуляции: WLCSP, FOWLP и PLP:

WLCSP (инкапсуляция размеров чипа), также известная как веерная инкапсуляция в WLP, является традиционным методом инкапсуляции, используемым для окончательного чипирования чипа. Он подходит для интегральных схем с меньшим количеством выводов. По мере увеличения количества выходного сигнала IC размер сварного шара становится более строгим. PCB не удовлетворяет требованиям, предъявляемым к размеру упакованного IC и расположению выводов вывода сигнала.

FOWLP начинается с чипирования, а затем перераспределяет их на новые искусственные пластины. Преимущества включают в себя уменьшение толщины упаковки, увеличение вентиляции (больше интерфейсов I / O), улучшение электрических характеристик и лучшую термостойкость. FIWLP и FOWLP имеют разные приложения, но они являются основными методами упаковки в будущем. FIWLP наиболее широко используется для аналоговых и гибридных сигнальных чипов, за которыми следуют беспроводные соединения, а датчики изображений CMOS также инкапсулируются с помощью технологии FIWLP. FOWLP будет использоваться в основном для процессорных чипов в мобильных устройствах.

PLP (панельная упаковка) похожа на FOWLP, которая перераспределяет чипы на более крупные прямоугольные панели, а не на круглые чипы. Большая площадь означает большую экономию затрат и более высокую эффективность упаковки. Кроме того, разрезание чипа на квадрат может привести к расточительному упаковке кристаллов, а прямоугольные панели могут эффективно решить эту проблему. Однако это также предъявляет более высокие требования к фотолитографии и выравниванию. Основная идея заключается в том, чтобы завершить производство чипов при непосредственной упаковке кремниевых пластин, инкапсулируя несколько чипов в одну общую структуру упаковки. Это позволяет избежать отдельных этапов упаковки каждого чипа в традиционном корпусе, что повышает производительность и снижает затраты.

Процесс упаковки на уровне кристаллов обычно включает следующие этапы:

Подготовка кристаллического круга: очистка и подготовка кремниевых пластин для обеспечения надежности и последовательности процесса упаковки.

Формирование конструкции упаковки: на кремниевую пластину наносится слой упаковочного материала, обычно полимера, для формирования фундамента конструкции упаковки.

Соединение цепей: создание металлических проводов (соединений с выводами) или других конструкций соединения цепей на кремниевых пластинах, соединяющих схемы чипа с конструкцией упаковки.

Тестирование и проверка качества: проверка электрических характеристик, проверка целостности упаковки и т. Д. Чтобы убедиться, что чип упаковки соответствует требованиям качества.

Разделение чипов: отделить упакованный чип от кремниевого чипа, чтобы получить отдельный упакованный чип.

WLP, основанный на технологии BGA, является улучшенной и улучшенной формой CSP, которая полностью отражает технические преимущества BGA и CSP. У него много уникальных преимуществ:

Высокая эффективность обработки упаковки: серийное производство в форме кристаллического круга.

Он унаследовал преимущества упаковки перевернутого чипа, то есть легкий, тонкий, короткий, маленький.

Низкие затраты на производственные мощности: можно в полной мере использовать оборудование для производства чипов, избегая необходимости инвестировать в отдельные упаковочные линии.

Унифицированные соображения проектирования чипов и пакетов: повышение эффективности проектирования и снижение затрат на проектирование.

Сократил производственный цикл: он значительно сократил весь процесс от изготовления чипов, инкапсуляции до доставки продукции, что привело к снижению затрат.

Эффективность затрат: стоимость WLP тесно связана с количеством чипов на каждом чипе. Чем больше чипов на чипе, тем ниже его стоимость. Эта упаковка является наименьшим и наименее затратным методом упаковки.

Преимущество WLP заключается в том, что он подходит для технологии упаковки чипов (CSP) для небольших интегральных схем. Используя технологии параллельного инкапсуляции и электронного тестирования на уровне кристаллов, WLP значительно сократила площадь чипа, одновременно увеличивая производство. Кроме того, подключение к чипу с параллельной проводимостью на уровне кристалла значительно снижает стоимость каждого ввода / вывода. Кроме того, упрощенная процедура тестирования уровня формы еще больше снижает затраты.

Использование упаковки на уровне кристалла позволяет осуществлять упаковку и тестирование на уровне кристалла.