La nascita iniziale del packaging a livello Wafer è stata guidata dalla produzione di componenti I/O a bassa velocità e transistor a bassa velocità per telefoni cellulari, come sensori passivi on-chip e IC di trasmissione di potenza. Attualmente, WLP è in una fase di sviluppo, spinta da applicazioni come Bluetooth, GPS e schede audio, portando ad un graduale aumento della domanda. Man mano che l'industria progredisce nella fase di produzione dei telefoni cellulari 3G, varie nuove applicazioni per i telefoni cellulari dovrebbero diventare un altro driver di crescita per WLP, tra cui sintonizzatori TV, trasmettitori FM e memorie stack. Con i produttori di dispositivi di memoria che implementano gradualmente WLP, ciò porterà a una trasformazione standardizzata dell'intero settore.

Attualmente, questa tecnologia è ampiamente utilizzata in vari campi come memoria flash, EEPROM, DRAM ad alta velocità, SRAM, driver LCD, dispositivi RF, dispositivi logici, dispositivi di gestione di potenza / batteria e dispositivi analogici (regolatori, sensori di temperatura, controller, amplificatori operativi, amplificatori di potenza). L'imballaggio a livello di wafer adotta principalmente due tecnologie di base: ridistribuzione del film sottile e formazione di urti. Il primo viene utilizzato per convertire le aree di incollaggio distribuite lungo la periferia del chip in aree di incollaggio bump distribuite in una forma di array planare sulla superficie del chip. Quest'ultimo viene utilizzato per creare urti sull'area di adesione del bump, formando un array di bump.

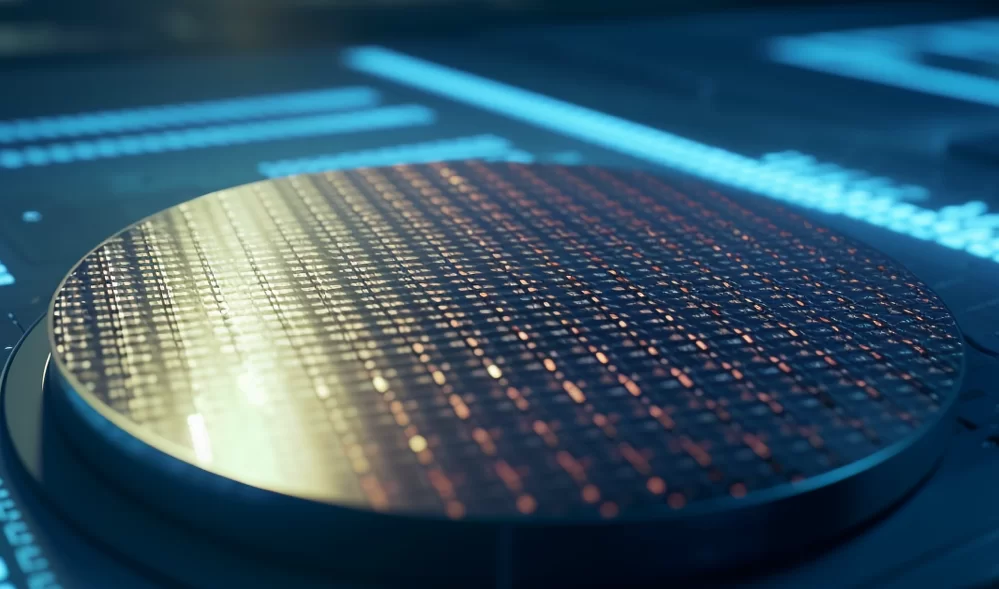

Imballaggio a livello di wafer

Attualmente, ci sono tre percorsi per il confezionamento a livello Wafer: WLCSP, FOWLP e PLP:

WLCSP (Wafer Level Chip Size Package), noto anche come WLP fan-in, è il metodo di imballaggio tradizionale per il taglio finale del chip. È adatto per circuiti integrati con un piccolo numero di pin. Man mano che il numero di segnali di uscita IC aumenta, la dimensione della sfera di saldatura diventa più rigorosa. Il PCB non può soddisfare il requisito di regolare la dimensione del IC confezionato e la posizione dei pin di uscita del segnale.

FOWLP inizia con il chip dicing e poi li ridistribuisce su nuovi wafer modellati artificiali. I vantaggi includono ridotto spessore del pacchetto, maggiore fan-out (più interfacce I/O), migliori prestazioni elettriche e migliore resistenza al calore. FIWLP e FOWLP hanno applicazioni diverse, ma entrambi sono i metodi di imballaggio dominanti del futuro. FIWLP è più ampiamente utilizzato nei chip analogici e misti, seguiti dalle interconnessioni wireless, e i sensori di immagine CMOS sono anche confezionati utilizzando la tecnologia FIWLP. FOWLP sarà utilizzato principalmente per i chip del processore nei dispositivi mobili.

PLP (Panel Level Packaging) è simile a FOWLP in quanto ridistribuisce i chip su pannelli rettangolari più grandi piuttosto che su wafer rotondi. L'area più ampia significa maggiori risparmi sui costi e maggiore efficienza di imballaggio. Inoltre, tagliare i chip in quadrati porta a imballaggi di wafer sprecati, che i pannelli rettangolari possono efficacemente affrontare. Tuttavia, questo pone anche esigenze più elevate sulla litografia e l'allineamento. L'idea di base è quella di completare la fabbricazione di chip contemporaneamente all'imballaggio diretto su wafer di silicio, imballando più unità di chip in una struttura complessiva del pacchetto. Questo evita la fase di confezionamento individuale di ogni chip in imballaggi convenzionali, aumentando così la produttività e riducendo i costi.

Il processo di confezionamento a livello Wafer include tipicamente i seguenti passaggi:

Preparazione Wafer: Pulizia e preparazione del wafer di silicio per garantire l'affidabilità e la coerenza del processo di confezionamento.

Formazione della struttura del pacchetto: Applicazione di uno strato di materiale di imballaggio, di solito un polimero, sul wafer di silicio per formare la base della struttura del pacchetto.

Collegamento del circuito: Creazione di fili metallici (legame del cavo) o altre strutture di collegamento del circuito sul wafer del silicio per collegare i circuiti del chip alla struttura del pacchetto.

Test e verifica di qualità: Condurre test di prestazione elettrica, test di integrità del pacchetto, ecc., per garantire che i chip confezionati soddisfino i requisiti di qualità.

Separazione chip: Separare i chip confezionati dal wafer di silicio per ottenere singoli chip confezionati.

WLP si basa sulla tecnologia BGA ed è una forma migliorata e migliorata di CSP, che riflette pienamente i vantaggi tecnici di BGA e CSP. Ha molti vantaggi unici:

Alta efficienza di lavorazione dell'imballaggio: è fabbricato utilizzando processi di produzione in lotti in forma di wafer.

Erede i vantaggi dell'imballaggio flip-chip, cioè leggero, sottile, corto e piccolo.

Costi bassi dell'impianto di produzione: può utilizzare completamente l'attrezzatura di produzione del chip, evitando la necessità di investire in linee di produzione separate di imballaggio.

Considerazione unificata della progettazione di chip e packaging: l'efficienza di progettazione è migliorata e i costi di progettazione sono ridotti.

Ciclo di produzione ridotto: accorcia significativamente l'intero processo dalla produzione di chip, imballaggio alla consegna del prodotto, portando alla riduzione dei costi.

Economicità: Il costo del WLP è strettamente correlato al numero di chip su ogni wafer. Più chip sul wafer, più basso è il costo di questo. Questo imballaggio è il metodo di imballaggio più piccolo e a basso costo.

Il vantaggio di WLP risiede nella sua applicabilità alla tecnologia di imballaggio a livello di chip (CSP) per circuiti integrati più piccoli. Adottando l'imballaggio parallelo e la tecnologia di test elettronici a livello di wafer, WLP riduce significativamente l'area del chip aumentando la resa di produzione. Inoltre, il costo per I/O è notevolmente ridotto conducendo connessioni chip in parallelo a livello wafer. Inoltre, le procedure semplificate di prova a livello dello stampo riducono ulteriormente i costi.

L'utilizzo di imballaggi a livello Wafer consente di ottenere imballaggi e test a livello di wafer.