Sự xuất hiện ban đầu của gói cấp wafer được thúc đẩy bởi việc sản xuất I/O tốc độ thấp của điện thoại di động và các cụm bóng bán dẫn tốc độ thấp, chẳng hạn như cảm biến trên chip thụ động và IC truyền tải điện. Hiện tại, WLP đang trong giai đoạn phát triển, được thúc đẩy bởi các ứng dụng như Bluetooth, GPS và card âm thanh, với nhu cầu ngày càng tăng. Khi ngành công nghiệp phát triển đến giai đoạn sản xuất điện thoại 3G, nhiều ứng dụng mới cho điện thoại di động dự kiến sẽ là một động lực tăng trưởng khác cho WLP, bao gồm bộ điều chỉnh TV, máy phát FM và bộ nhớ ngăn xếp. Khi các nhà sản xuất thiết bị lưu trữ dần triển khai WLP, nó sẽ dẫn đến sự chuyển đổi tiêu chuẩn hóa trong toàn ngành.

Hiện nay, công nghệ này được sử dụng rộng rãi trong nhiều lĩnh vực khác nhau như bộ nhớ flash, EEPROM, DRAM tốc độ cao, SRAM, trình điều khiển LCD, thiết bị RF, thiết bị logic, thiết bị quản lý nguồn/pin và thiết bị tương tự (bộ điều chỉnh, cảm biến nhiệt độ, bộ điều khiển, bộ khuếch đại hoạt động, bộ khuếch đại công suất). Đóng gói cấp wafer chủ yếu sử dụng hai kỹ thuật cơ bản: phân phối lại màng mỏng và hình thành khối lồi. Trước đây được sử dụng để chuyển đổi các vùng tương tác được phân phối dọc theo ngoại vi của chip thành các vùng tương tác lồi được phân phối dưới dạng mảng phẳng trên bề mặt chip. Loại thứ hai được sử dụng để tạo ra các khối lồi trên khu vực liên kết các khối lồi, tạo thành một mảng các khối lồi.

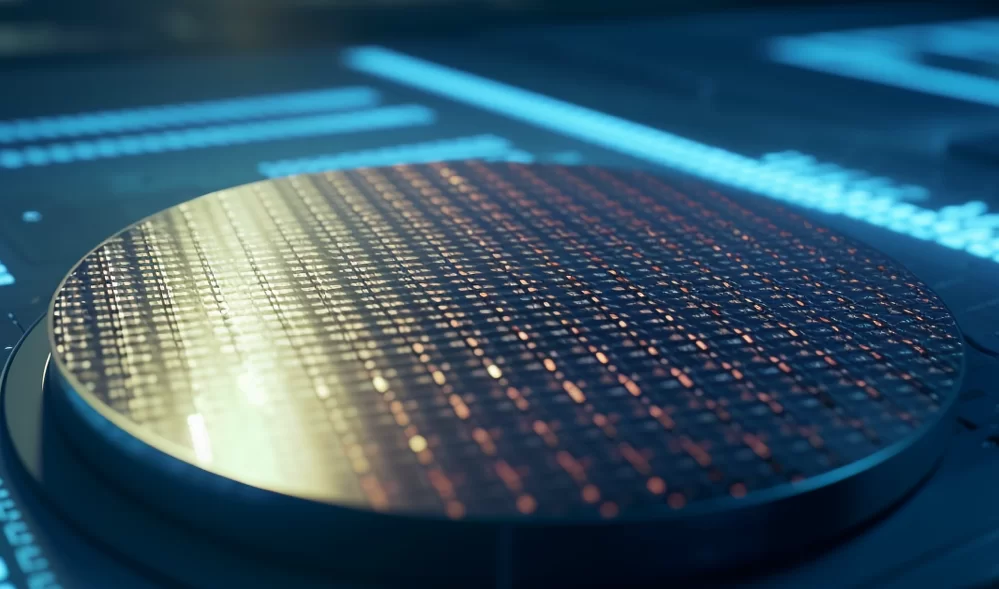

Đóng gói cấp wafer

Hiện tại, có ba đường dẫn cho gói cấp wafer: WLCSP, FOWLP và PLP:

WLCSP (wafer-level chip-size package), còn được gọi là đóng gói quạt trong WLP, là phương pháp đóng gói truyền thống được sử dụng cho chip chip cuối cùng. Nó hoạt động tốt cho các mạch tích hợp với số lượng pin nhỏ hơn. Khi số lượng tín hiệu đầu ra IC tăng lên, kích thước bóng hàn trở nên nghiêm ngặt hơn. PCB không thể đáp ứng yêu cầu điều chỉnh kích thước của IC đóng gói và vị trí của chân đầu ra tín hiệu.

FOWLP bắt đầu với các chip chip và sau đó phân phối lại chúng trên các wafer nhân tạo mới. Ưu điểm bao gồm giảm độ dày gói, tăng quạt (nhiều giao diện I/O hơn), hiệu suất điện tốt hơn và khả năng chịu nhiệt tốt hơn. FIWLP và FOWLP có các ứng dụng khác nhau, nhưng cả hai đều là phương pháp đóng gói chính trong tương lai. FIWLP được sử dụng rộng rãi nhất cho các chip tín hiệu tương tự và lai, tiếp theo là kết nối không dây, với các cảm biến hình ảnh CMOS cũng được đóng gói bằng công nghệ FIWLP. FOWLP sẽ được sử dụng chủ yếu cho chip xử lý trong các thiết bị di động.

PLP (Panel Level Packing) tương tự như FOWLP, phân phối lại các chip trên các tấm hình chữ nhật lớn hơn thay vì các chip tròn. Diện tích lớn hơn có nghĩa là tiết kiệm chi phí hơn và hiệu quả đóng gói cao hơn. Ngoài ra, việc cắt chip thành hình vuông dẫn đến việc đóng gói wafer lãng phí, và các tấm hình chữ nhật có thể giải quyết vấn đề này một cách hiệu quả. Tuy nhiên, điều này cũng đặt ra yêu cầu cao hơn về in thạch bản và liên kết. Ý tưởng cơ bản là hoàn thành sản xuất chip trong khi đóng gói trực tiếp các tấm silicon, đóng gói nhiều đơn vị chip trong một cấu trúc gói tích hợp. Điều này tránh được bước đóng gói từng chip riêng lẻ trong một gói truyền thống, do đó tăng năng suất và giảm chi phí.

Quá trình đóng gói cấp wafer thường bao gồm các bước sau:

Chuẩn bị wafer: Làm sạch và chuẩn bị các tấm silicon để đảm bảo độ tin cậy và tính nhất quán của quá trình đóng gói.

Hình thành cấu trúc đóng gói: Một lớp vật liệu đóng gói, thường là polymer, được phủ lên một tấm silicon để tạo thành cơ sở cho cấu trúc đóng gói.

Kết nối mạch: Tạo dây kim loại (khớp chì) hoặc cấu trúc kết nối mạch khác trên chip silicon để kết nối mạch của chip với cấu trúc gói.

Kiểm tra và xác minh chất lượng: Kiểm tra hiệu suất điện, kiểm tra tính toàn vẹn của gói, v.v. được thực hiện để đảm bảo chip gói đáp ứng các yêu cầu chất lượng.

Tách chip: Tách chip đóng gói khỏi chip silicon để có được chip đóng gói riêng biệt.

Dựa trên công nghệ BGA, WLP là một hình thức cải tiến và nâng cao của CSP, phản ánh đầy đủ các ưu điểm kỹ thuật của BGA và CSP. Nó có nhiều ưu điểm độc đáo:

Hiệu quả xử lý gói cao: được sản xuất bằng quy trình sản xuất hàng loạt dưới dạng wafer.

Nó thừa hưởng những ưu điểm của gói chip đảo ngược, đó là nhẹ, mỏng, ngắn và nhỏ.

Chi phí cơ sở sản xuất thấp: thiết bị sản xuất chip có thể được sử dụng đầy đủ và tránh sự cần thiết phải đầu tư vào dây chuyền sản xuất gói riêng biệt.

Cân nhắc thiết kế chip và gói thống nhất: Cải thiện hiệu quả thiết kế và giảm chi phí thiết kế.

Rút ngắn chu kỳ sản xuất: Nó rút ngắn đáng kể toàn bộ quá trình từ sản xuất chip, đóng gói đến phân phối sản phẩm, do đó giảm chi phí.

Chi phí hiệu quả: Chi phí của WLP liên quan chặt chẽ đến số lượng chip trên mỗi wafer. Càng nhiều chip trên chip, chi phí càng thấp. Loại bao bì này là phương pháp đóng gói tối thiểu và chi phí thấp nhất.

Ưu điểm của WLP là nó phù hợp với công nghệ đóng gói cấp chip (CSP) cho các mạch tích hợp nhỏ hơn. Bằng cách áp dụng công nghệ đóng gói song song và thử nghiệm điện tử ở cấp độ wafer, WLP làm giảm đáng kể diện tích chip trong khi tăng sản lượng. Ngoài ra, chi phí cho mỗi I/O được giảm đáng kể bằng cách dẫn kết nối chip song song ở cấp wafer. Ngoài ra, quy trình kiểm tra mức khuôn đơn giản hóa giúp giảm chi phí hơn nữa.

Sử dụng đóng gói cấp wafer cho phép đóng gói chip và thử nghiệm ở cấp wafer.