ウェハレベルパッケージの最初の出現は、受動オンチップセンサや電力伝送ICなどの携帯電話の低速I/Oと低速トランジスタコンポーネントの製造によって推進された。現在、WLPは発展段階にあり、Bluetooth、GPS、サウンドカードなどの応用に後押しされ、需要は徐々に増加している。業界が3 G携帯電話の生産段階に発展するにつれて、携帯電話の各種の新しい応用はWLPのもう一つの成長駆動要素になることが期待されており、テレビチューナー、周波数変調送信機、スタックメモリを含む。ストレージ機器メーカーがWLPを導入するにつれて、業界全体の標準化された移行につながります。

現在、この技術はフラッシュメモリ、EEPROM、高速DRAM、SRAM、LCDドライバ、RFデバイス、論理デバイス、電源/電池管理デバイス、アナログデバイス(レギュレータ、温度センサ、コントローラ、演算増幅器、電力増幅器)などの様々な分野に広く応用されている。ウエハレベルパッケージは主に2つの基本技術を採用している:薄膜再分配とバンプ形成。前者は、チップの周囲に沿って分布する接合領域を、チップ表面上に平面アレイ状に分布するバンプ接合領域に変換するために用いられる。後者は、バンプ結合領域にバンプを作成し、バンプ配列を形成するために使用されます。

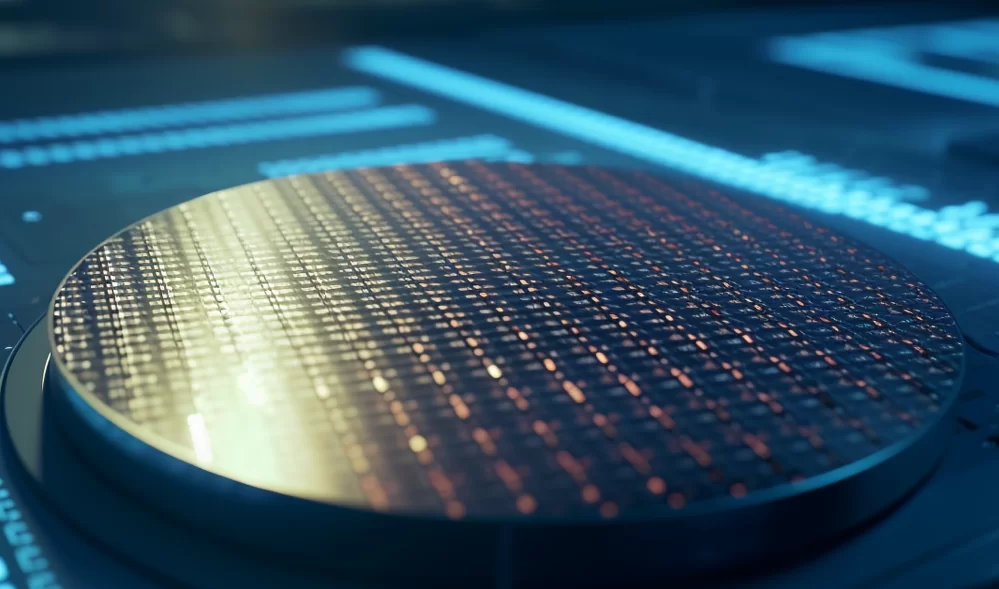

ウェハレベルパッケージ

現在、ウェハレベルのパッケージには、WLCSP、FOWLP、PLPの3つのパスがあります。

WLCSP(ウェハレベルチップサイズパッケージ)は、WLPにおける扇形パッケージとも呼ばれ、最終チップスライスのための従来のパッケージ方法である。ピン数の少ない集積回路に適しています。IC出力信号数の増加に伴い、ハンダボールサイズはより厳しくなっている。PCBはパッケージICのサイズと信号出力ピンの位置を調整する要求を満たすことができない。

FOWLPはチップダイシングから始まり、新しい人工成形ウェハに再配置されます。利点としては、パッケージの厚さを減らすこと、ファンアウト(より多くのI/Oインタフェース)を増やすこと、より良い電気的性能とより良い耐熱性が挙げられる。FIWLPとFOWLPは異なる応用があるが、いずれも将来の主要な包装方法である。FIWLPは最も広くアナログとハイブリッド信号チップに用いられ、次に無線相互接続であり、CMOSイメージセンサーもFIWLP技術を用いてパッケージ化されている。FOWLPは主にモバイルデバイスのプロセッサチップに使用されます。

PLP(パネルレベルパッケージ)はFOWLPと同様で、円形ウェハではなく、より大きな矩形パネルにチップを再割り当てします。より広い面積は、より多くのコスト削減とより高い包装効率を意味します。また、チップを正方形にカットすると無駄なウエハパッケージになり、矩形パネルが効果的に解決することができます。しかし、これはリソグラフィとアライメントに対してより高い要求を提出している。その基本的な考え方は、シリコンウェハを直接カプセル化しながらチップ製造を完了し、複数のチップユニットを1つのパッケージ構造にカプセル化することである。これにより、従来のパッケージで各チップを個別にパッケージ化する工程が回避され、生産性が向上し、コストが削減されます。

ウェハレベルパッケージのプロセスには、通常、次の手順があります。

ウェハ製造:シリコンウェハを洗浄して製造し、パッケージプロセスの信頼性と一貫性を確保する。

封止構造形成:封止構造の基礎を形成するために、シリコンシート上に封止材料の層をコーティングする。

回路接続:シリコンウエハ上に金属線(ワイヤボンディング)またはその他の回路接続構造を作成し、チップの回路をパッケージ構造に接続する。

テストと品質検証:電気性能テスト、パッケージ完全性テストなどを行い、パッケージチップが品質要求に合致することを確保する。

チップ分離:パッケージされたチップをシリコンチップから分離して、個別のパッケージチップを得る。

WLPはBGA技術に基づいており、CSPの改善と強化形式であり、BGAとCSPの技術的優位性を十分に体現している。これには、次のようなユニークな利点があります。

高パッケージ加工効率:ウエハ形式の量産プロセスを用いて製造する。

フリップチップパッケージの利点、すなわち軽量、薄さ、短さ、小さを継承しています。

生産施設のコストが低い:チップ製造設備を十分に利用でき、単独のパッケージ生産ラインへの投資を避けることができる。

統一されたチップとパッケージ設計の考慮:設計効率を高め、設計コストを削減した。

製造サイクルの短縮:チップ製造、パッケージから製品納入までのプロセスを大幅に短縮し、コストを削減します。

コスト効果:WLPのコストは各ウエハ上のチップ数と密接に関連している。ウェハ上のチップが多ければ多いほど、そのコストは低くなります。この包装は最小でコストが最も低い包装方法である。

WLPの利点は、小さな集積回路のチップレベルパッケージ(CSP)技術に適していることにある。ウェハレベルで並列パッケージと電子テスト技術を採用することにより、WLPは生産量を向上させると同時にチップ面積を大幅に減少させた。また、ウェハレベルでの並列伝導チップ接続により、I/Oあたりのコストが大幅に削減されます。また、簡略化された金型レベル試験プログラムはさらにコストを削減しました。

ウェハレベルパッケージを利用することで、ウェハレベルでチップパッケージとテストを実現することができる。