PCB tahtasındaki LVDS sinyalinin tasarımı sadece farklı bir sinyal değil, hızlı bir dijital sinyali de. Bu yüzden, LVDS transmisi ortamın PCB tahta kabloları veya kabloları kullandığına rağmen, sinyali medya terminalinde refleks edilmesini engellemek için ayarlar alınmalıdır ve elektromagnet araştırması sinyal integritesini sağlamak için azaltılmalı. Bu elementleri gezerken, yüksek hızlı farklı devre tahtalarını tasarlamak çok zor değil. Aşa ğıdaki kısa olarak PCB tahtasında LVDS sinyalinin tasarım noktalarını tanıtır: 2.1 LVDS sinyalleri ile çok katı tahtası oluşturulması genellikle çok katı tahtası olarak dizinler. LVDS sinyali yüksek hızlı sinyal olduğundan dolayı, yakın katı araştırmaları önlemek için LVDS sinyalini korumak için yeryüzü katı olmalı. Eğer fiziksel uzay koşulları izin verirse, LVDS sinyalleri ve diğer sinyalleri farklı katlara yerleştirin. Örneğin, dört katı tahtasında, katlar genelde böyle yerleştirilebilir: LVDS sinyal katı, yeryüzü katı, güç katı ve diğer sinyal katları. 2.2 LVDS sinyal impedance hesaplaması ve kontrol. LVDS sinyalinin voltaj dönüşü sadece 350mV. Şimdiki yönlendirilen farklı sinyal operasyonuna uygun. Sinyalin yayıldığında gösterilen sinyal tarafından etkilenmemesini sağlamak için LVDS sinyali yayılma hatlarının kontrol edilmesini istiyor ve farklı impedans genellikle 100 +/- 10Ω olur. İmparans kontrolünün kalitesi sinyal bütünlüğüne ve gecikmesine doğrudan etkiler.

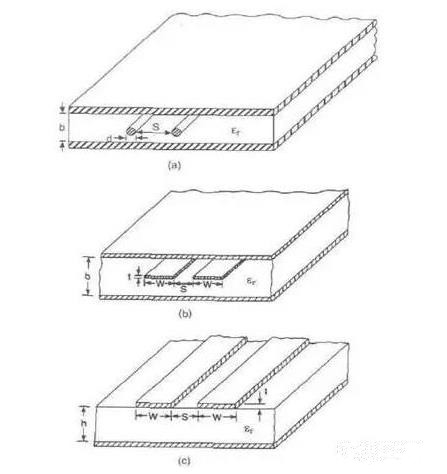

PCB tahtasını nasıl kontrol edecek? 1. 1 Düzenleme modunu, parametreleri ve impedance hesaplamasını belirleyin. LVDS dış katı mikrostrip hattı farklı moduna ve iç katı strip hattı farklı moduna bölüyor. Parametrleri mantıklı ve bağlı yazılım kullanarak hesaplanabilir. Hesaplama üzerinde, impedans değeri, izolatör katının kalınlığına doğrudan proporsyonal ve dizilektik konstantiyle tersiyle proporsyonal, kabın kalınlığına ve genişliğine uyun paralel eşit uzak hatların prensipine ve sıkı bağlantılara uyun. Çizgi genişliğini ve boşluğunu belirledikten sonra, yönlendiğinde hesaplanmış çizgi genişliğini ve boşluğunu ve iki çizgi arasındaki boşluğu her zaman sürekli sürekli tutmalı, yani paralel olmalı (resim yerleştirebilirsiniz). Aynı zamanda, çizgi genişliğini ve uzanımı hesapladığında sıkı birleşme prensipi, yani farklı çizginin uzanımı çizgi genişliğinden az veya eşittir. İki farklı sinyal çizgileri çok yaklaştığında, şu anki transmis yöntemi tersidir, manyetik alanlar birbirlerini iptal ediyor, elektrik alanlar birbirlerine bağlanır ve elektromagnet radyasyonu çok daha küçük. Ayrıca, iki kablo aynı katta olmalı. Çünkü PCB tahtasının gerçek işlemesinde, çubukların arasındaki laminasyon derecesi aynı katının etkileme doğruluğundan çok daha düşük ve laminasyon sürecinde dielektrik kaybı, farklı çizgilerin arasındaki uzağın karışık katmanın kalınlığına eşit olduğunu garanti edemez. Bu da katlar arasındaki farklı çiftlerin farklı impedans değişimini neden ediyor.

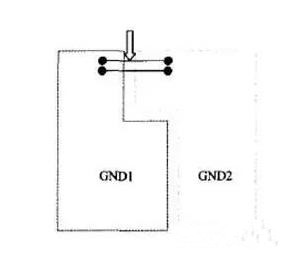

1.3 Kısa ve düz. Sinyalin kalitesini sağlamak için, LVDS farklı çift izleri mümkün olduğunca kısa ve düzgün olmalı, sürücükte vial sayısını azaltmak ve çok uzun farklı çift dönüşünden kaçırmak ve çok fazla dönüş olmalı. Köşelerde 45° ya da arca kullanmaya çalışın. 90° dönüşünden kaçın. LVDS çift yönlendirme metodlarının seçiminin farklı çizgi çift arasında sınırı yok. Mikrostrip çizgi ve strip çizgi kullanılabilir, ama iyi bir referans uça ğı olduğunu belirtmeli. Farklı farklı çizgiler arasındaki yer çok küçük olmamalı ve en azından 3-5 kat farklı çizgiler arasındaki uzay olmalı. Eğer gerekirse, karşılaştırma konuşmasını engellemek için farklı farklı çizgi çiftleri arasında yer deliğini toplayın. LVDS sinyalleri mümkün olduğunca diğer sinyallerden uzak tutun. LVDS farklı sinyaller uçakların arasında bölünemez. İki farklı sinyaller birbirlerine dönüş yolları olsa da, karışık bölümleme sinyalin dönüşünü kesmeyecek, fakat bölümünün karşısındaki transmis çizgi bir referens uça ğının eksikliği yüzünden impedance'e son vermeye sebep olacak (görüntülere göre, GND1 ve GND2 LVDS Toprak uçağına yakın olduğu yerde). Alıcı sonun ve alıcının eşleşen direnişinin arasındaki mesafe mümkün olduğunca yakın olmalı. Aynı zamanda, eşleşen dirençliğin doğruluğu kontrol edilmeli. Topoloji noktaları için, izlerin imkansızlığı genelde 100Ω üzerinde kontrol edilir, fakat uyuşturucu dirençliği gerçek durumlara göre ayarlanabilir. Yüzde %1-2 dirençlik derecede. Çünkü tecrübelerine göre %10 uygulama uygulaması %5 refleksiyonu üretir.

2. Seri LVDS sinyallerinin simülasyonu analizi. Yukarıdaki LVDS sinyallerini tasarladığında dikkati çekilmeli konuları analiz ediyor. Yukarıdaki kurallar genellikle PCB tasarımı sırasında takip edilir, tasarımın doğruluğunu ve doğruluğunu geliştirmek için, PCB'nin tamamen sinyal simülasyonu simülasyonuyla gerçekleştirilmeli. Sinyalin karışık konuşmasını, gecikme, yansıtma ve göz örneklerinin dalga formlarını alın, doğru tasarımın amacını başarmak için. Sinyal integritet sorununun simülasyonu ilk olarak komponentlerin simülasyon modelini oluşturmak ve sonra dönüştürme sürecinin parametrelerini ve sınırlarını belirlemek için önceki simülasyonu gerçekleştirmek. Fiziksel gerçekleştirme sahnesi sınırlara göre tasarlanmış ve sonrası simülasyon tasarımın tasarım taleplerinin uyumlu olup olmadığını doğrulamak için gerçekleştiriliyor. Tüm süreçte model in doğası simülasyon sonuçlarına doğrudan etkiler, önceki simülasyon ve post simulasyon fazlarında kullanılan simülasyon analiz metodlarına da etkiler. Simülasyon sonuçlarına da kritik oluyor ve bu tasarımda daha yüksek derece uyuşturucu modeli kullanılır. Aşa ğıdaki projeler, bu tasarımda simulasyon sürecini göstermek için gerçek projelerin kombinasyonu.2.1 PCB tahtasının üstündeki analiziden ayarlanması için, PCB tahtasının ayarlanması sinyal ve impedans hesaplamasına yakın bağlı olduğunu biliyor. Bu yüzden, PCB tahtası tasarımından önce stacking tasarımı gerçekleştirmek zorunda, sonra da sinyalin impedance hesaplaması.2.2 DC voltasyon değerini ayarlayın. Bu adım, genellikle belli ağlar için DC voltasyon değerini belirtmek için (genellikle elektrik alanı, etc.), ağda uygulanacak DC voltasyonu belirlemek için, EMI simülasyonu yapmak için bir ya da daha fazla voltaj kaynağını belirlemek gerekiyor. Bu voltaj değerleri simülasyon sürecinde modelde kullanılan referans voltaj bilgileri belirtildi.2.3 Aygıt ayarları aletro simülasyonu sırasında aletro ayrılır ayrılır ayrılır üç kategoriye: IC, bağlantılar ve diskret aygıtlar (dirençlik kapasiteleri, etc.), aletro aygıt türüne göre aygıt türüne göre simülasyon özelliklerini verir. Diskretli aygıtlar ve bağlantıcı pins Bu özellik UPSPEC ve IC'in pin özelliği IN, OUT, BI, etc.2.4 Model allokasyonu olabilir.The main models used in the board-level high-speed PCB board simulation process are device models and transmission line models. Aygıt modeli genellikle aygıt üreticisi tarafından temin edilir. Yüksek hızlı seri sinyalinde evlatlığımız SPICE modeli simülasyon analizi üzerinde devam etmek için daha değerli. İletim hattı modeli simülasyon yazılım modellerinden oluşturulmuş. Sinyal yayınlandığında, yayınlama çizgi sinyal integritet sorunu önemli yapar, böylece yayınlama çizgisini modellemek için simulasyon yazılımının yeteneğinin doğrudan simülasyon sonuçlarına etkileyecek.2.5 SI kontrolü SI Denetim fonksiyonu özel bir a ğ veya ağ grupu analiz için çıkarılabilir mi kontrol etmek için kullanılır. Genellikle, dikkatimizi çekmek zorunda olduğumuz yüksek hızlı ağ ayarlamak. Bu tasarım genellikle LVDS seri sinyallerine odaklanır. Ağ bu yollardan geçtiğini topolojiden görebiliyor, bu sinyal yayınlama etkisi sebebi olacak. Bu makale sadece sinyallerden birinin ağ topolojik diagram ını örnek olarak alır: 4:2.7 Şekil'de gösterilen şekilde, yukarıdaki ilişkili adımların ayarlandıktan sonra, simülasyon gerçekleştirilebilir. Alegro sinyal refleks simülasyonu ve karışık konuşma simülasyonu gerçekleştirebilir ve farklı çizgi de göz diagram analizi gerçekleştirmesi gerekiyor. Tabii ki, simülasyon aynı zamanda önceki simülasyon ve sonraki simülasyon olarak ayrılır. Alegro'yu PCB tahtasını tasarlamak için kullandığında, tasarımı gerçek zamanda simülasyon sonuçlarıyla değiştirmek gerekir. Çünkü simulasyon süreci karmaşık ve adımlar karmaşık, onları birbirine tanımayacağım. Farklı çiftlerin düzenlenmesine dikkat etmek için iki nokta var. Birincisi, iki çizginin uzunluğu mümkün olduğunca kadar uzun olmalı ve eşit uzunluğu, iki farklı sinyal her zaman tersine tutulmasını sağlamaktır. Ortak mod komponentlerini azaltmak için Polonyalık. Diğeri, iki çizgi arasındaki mesafe (bu mesafe farklı impedans tarafından belirlenmiş) her zaman sürekli tutulmalıdır, yani paralel tutulmalıdır. İki paralel yol var, birisi, iki kablo aynı tarafta çalışıyor, diğeri de yukarıda ve aşağıda (aşağıda) iki kablo üzerinde çalışıyor. Genelde eskisinin bir tarafından daha fazla uygulamaları var. Aynı mesafe, ikisinin arasında aynı farklı engelleme ve refleksiyonun azaltmasını sağlamak. Farklı çiftin düzenleme yöntemi yakın ve paralel olmalı. Böyle denilen uygun yaklaşık, çünkü bu uzakta farklı impedans değerini etkileyecek. Bu, farklı çift tasarlamak için önemli bir parametre. Paralelizm ihtiyacı ayrıca farklı impedans konsistencisini korumak. Eğer iki çizgi birden uzak ve yakın olursa, farklı impedans uygunsuz olacak, bu da sinyal büyüklüğüne ve zamanlama gecikmesine etkileyecek. Simüle edilmiş S-Parametre grafiğinden, farklı çift ve sinyal yeteneğinin farklı engellemesi analiz edilebilir. Bu tasarımdaki anahtar sinyal simülasyon dalga formları açıklama için altında verilir. Simülasyon efsanesinden 5. Şekil olarak görülebilir ki S11'in frekans alanında 0-3.0GHz'in düşürme indeksi: aşağıda.