オンライン機能テストを行うとき PCB基板バス装置 ((74245)), テストは双方向入力/出力ピンは、バスを介してそれに接続された他のデバイスに影響され得る. テスト中のボードが電源投入された後、バス装置はイネーブル状態にある, その出力/入力ピンはトライステート高インピーダンス状態にない. テストバスデバイスでバス競合が発生したときに結果ウィンドウをテストする. バス競合の影響を排除し、試験されたチップの試験に合格するために, ユーザは関連バス装置を隔離しなければならない.

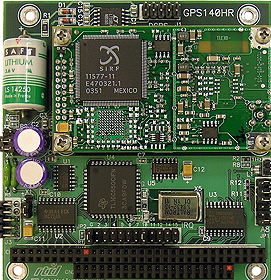

試験結果は74245の3,4,9番ピンが反転しなかったことを示し,試験は失敗した。このとき、ユーザは、ピンの状態からチップの各ピンの動的インピーダンスをチェックして、接地に短絡されたピンが存在するか、または接地に対して非常に低い抵抗(5オーム未満)があるかどうかを判断する必要がある。右上の画像から、地面に対する第11、第16、および第17のピンのインピーダンスがおよそ290オームであると気がつくことができて、グランドに対する他の出力および入力ピンのインピーダンスは、17 - 23オームの間である。前者はピンが論理ハイ状態であり、後者が論理ロー状態であることを示す。第2ピンは試験に合格し、出力ピンが接続されたデバイスのプルダウン効果に耐えることができるので、バス競合によって影響を受けなかった。

ユーザーがテスト失敗がバス競合によって引き起こされるか、または破損したデバイス機能に起因するかどうか識別することができなければなりません。この例では、テスト失敗の理由はバス競合である。デバイス上の完全なテストを実行するために、ユーザーは関連バス装置を分離しなければならなくて、被試験デバイスに影響を及ぼすことのない高インピーダンス状態のその出力ピンを作る必要がある。

チップの第3のピンが出力ピンとして使用されるとき、それは接続されたチップによってプルダウンされて、反転することができない。ピン3が入力ピンとして使用される場合、QT 200の最大駆動電流は650 mAであるので、ピン3を他のチップでプルダウンしても、QT 200はピン3を高電位に引き抜くことができるので、ピン17をテストすることができる。チップの機能が損なわれると、今度はピン17に出力テストを渡すことはできない。

実際のテスト結果は、17番ピン出力テストが合格したことです, 明らかにチップの機能が損なわれない, しかし、バス論争問題.

どのチップがPCBバス競合を引き起こして、孤立しなければならないかについて決定する方法?

ユーザーがテストされたボードの回路図ダイヤグラムを有する場合、まず、試験されたチップに接続している他の全てのバスチップを見つける。通常、回路内のバスチップは以下の3つの範疇に分けることができる。

イネーブル端子は他のチップの出力端子に接続される

つ以上のバスチップのイネーブル端子は接続される

c .イネーブル・ターミナルは直接接地または+5 V電源に接続される。

バス・チップの第1のタイプのために、分離はQT 200(FC 0からFC 7)までの対応する論理レベルをQT 200のフライング・リード・チャンネルにセットすることによって、各々の有効な端末のためにセットされなければならなくて、それからそれぞれ、これらのイネーブル端末に接続するバス・チップのための第2のタイプのために、1つの絶縁チャネルは提供される。そして、それはチップの一つのイネーブル終末に対する連結である第3の種類のバス・チップのために、分離チャンネルがその有効端末上の逆ドライブを実行することができないので、絶縁設定は直接実行されることができない。一般的な処理原理は、第1の2種類のバスチップを最初にセットして、テストされたチップのテスト結果が満足しているかどうか(すなわち、チップの品質を判定することができるか)を参照することである。まだ不満があるならば、第3のタイプのバス・チップを孤立させる処置をしてください。一般に、secant方式は、イネーブル端子を接地または+5 Vの電源から切り離して分離するために用いられる。

分離点を設定した後、チップを再検査します。テストが通過するならば、セットされた分離チャンネルを1つずつ取り除いて、再テストしてください。テストが失敗すると、分離設定が解除されたバスチップはバス競合を生成するチップである。チップの分離チャネルを再接続し、上記の方法に従って他の未決定のバスチップをチェックし続ける。最後まで(ボードの学習モードでは、ノートパッドを起動する必要がありますすべてのバスチップを見つけるには、チップは、壊れたボードを修復するときに大きな助けとなるバスチップのテストのために絶縁される必要があります記録)。

ユーザーが回路図を持っていない場合、彼はテストのチップに接続されている他のバスチップを見つけるためにQSM / VIテストメソッドでスキャンテストを使用することができます。具体的な方法は:ICFTテストモードから直接対話型QSM / VIテストウィンドウを入力し、テストするチップの名前をカスタマイズし、ピン数を40に設定し、312 Hzまでの測定周波数を設定し、回路のトラッキングのためのQT 200ケーブルを使用します(2つの20ピン固定具があります)。機能テスト(固定の最初のピンがチップの第1のピンに直面する)の下でバス・チップに固定具1を接続してください、そして、検査の下のボードの他のどのバス・チップにもフィクスチャ2を接続してください、そして、次に、スキャンテストを開始してください。つのチップ間の接続がある場合は、画面上のウィンドウに表示されます。このうち、ピン1〜20は固定具1に接続されたチップを示し、ピン21〜40は固定具2に接続されたチップを示す。ウィンドウの第5のピンと35番のピンがL 1シンボルでマークされるならば、それは第1のチップの第5のピンが第2のチップの15のピンに接続していることを意味します。

どのようにバスデバイスの品質を判断するためにシステムのデジタルオシロスコープ機能を使用するには?

デバイスをテストする場合、デバイスの品質が分離によって判断できない場合は、このシステムデジタルオシロスコープ(DSO)の最新機能を使用してテストすることができます。基本的な操作方法は以下の通りです。

基板が正常なクロック動作をするように、テスト中のPCB上に結晶をはんだ付けする。

テストプローブを適切なチャネルに接続します(注:選択したプローブチャネルはシステムソフトウェアの異なるバージョンでは異なります)

テストウィンドウのツールバーからDSOキーを押してデジタルオシロスコープモードを起動します。

試験の電源を入れる PCBボード

順番にテストされたバスデバイスの異なるピンにプローブを接続し、画面上のテストされたピンの実際の信号を見ることができます。信号がハイからローに変化すると、ピンが正常に機能することを意味する。信号電位を2 Vと1.8 Vの間に固定すれば、ピンに特別な注意を払うべきである。これは、ピンの機能が損なわれたり、ピンが開回路状態の出力ピンであるためである。このとき、このチップはクロック回路でよく使用されるので、クリスタル近傍の7404チップを検出することができる。7404の出力ピンをプローブでテストするには、波形信号を示す。そうでなければ、テストされたPCBボードの電源が正常であるかどうか、そして、水晶が損害を受けるかどうかチェックする。なお、オシロスコープは、水晶発振回路への影響を避けるために、クロック信号を検出する際に100 Kのインピーダンスを選択すべきである。

ピンがフローティング状態にあるかどうか検出するために, オシロスコープのインピーダンスは10 Kとして選択できる.ピンが確実に浮遊している場合(インピーダンスが1メガオームより大きい場合), その後、プローブがピンに触れると, 10 Kのインピーダンスはピンを低レベルに引き上げる. ピンが浮いていないならば, しかし、固定レベル, プローブはそれを引き下げない. これから, の真の状態 PCB基板ピン 判断できる.