Analysis of common preventive measures against ESD in панель PCB design

The static electricity in the human body, the environment, даже электронное оборудование может причинить различный ущерб конкретному оборудованию полупроводниковый чип, for example, просачивать изоляционный слой в сборку; взломать двери элементов Mosfet и CMOS.

триггер в периферийном устройстве CMMOS; короткозамкнутый смещённый PN PN - переход; прямое разделение pn на соединения; плавильные провода или алюминий в активных приборах.

для устранения помех и разрушений, связанных с ионизирующим зарядом (Э) в электронном оборудовании, необходимо принять различные технические меры для их предотвращения.

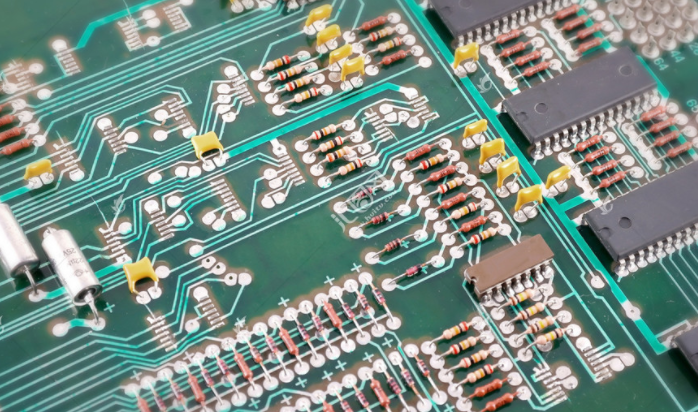

В настоящем документе содержится информация о конструкции печатных схем для защиты от электростатических разрядов (ESD), включая их установку, правильное расположение, монтаж и монтаж.

(1) Stacking By using the multilayer printed circuit board as much as possible, как важный источник нагрузки на энергосистему многослойный PCB the surface of the ground can compensate the load of the electrostatic discharge source, Таким образом, уменьшить проблемы, связанные с электростатическим полем. The quality surface of the printed circuit can also be used as a щит for the signal line (of course, Чем больше открыта поверхность протона, the greater the efficiency of protection). Кроме того, if discharged, нагрузка может легко вливаться в поверхность печатной платы, а не в сигнальную линию. This will help protect the components, Потому что заряд может быть удалён перед повреждением узла. Of course, для снижения стоимости некоторых систем, only double-layer boardscan be used.

(2) Loop The induced current on the панель PCB, замкнутая цепь с переменным магнитным током. The magnitude of the current is proportional to the surface of the ring. более большое кольцо содержит больше потока, which generates a higher current in the circuit. поэтому, the area of the loop must be reduced.

(3) длина соединения цепи, пожалуйста, убедитесь, что линия сигнала как можно короче. для того чтобы антенна была эффективной, ее длина должна быть значительной частью длины волны. Это означает, что более длинные линии будут способствовать приему частот, генерируемых импульсами EDD, в то время как более короткие линии будут иметь лишь меньшую Частотную составляющую.

Таким образом, энергия электромагнитного поля, создаваемая электростатическим разрядом проводника короткого замыкания, сокращается до источника энергии в цепи. когда длина сигнальной линии превышает 300 мм (12 дюймов), требуется параллельная массовая линия.

можно также предоставить протонные линии на сигнальной или смежной поверхности. в соответствующей группе компонентов есть много взаимосвязанных компонентов, которые должны быть близко друг к другу. например, периферийное оборудование E / S как можно ближе к соединителям E / S, с тем чтобы сократить длину межсоединенных печатных схем.

4) при прямом разряде с наземных свалок статического электричества могут быть повреждены чувствительные схемы. Помимо использования диодов TVS, используется один или несколько конденсаторов высокочастотной производной, которые расположены между скоропортящимися частями и электропитанием. функция обходного канала позволяет уменьшить приток заряда и поддерживать разницу напряжения между питанием и заземленным соединением порта. TVS сохраняет индуктивность и сохраняет напряжение отключения TVS. телевизоры и конденсаторы должны быть как можно ближе к защищенным интегральным схемам. чтобы уменьшить эффект паразитной индукции, необходимо обеспечить кратчайшую длину конденсатора и количество листов на канале TVS.

(5) Parasitic inductance in the protection circuit When an ESD event occurs, the parasitic inductance in the path of the TVS diode can cause a serious voltage overshoot. Although the induced voltage of VL = l * di / DT для индуктивного конца, over-boosting may always exceed the damage voltage threshold of the protected integrated circuit. общее напряжение защитной цепи - сумма напряжения, создаваемого разрывным напряжением на ТВС - диоде, VT = vC + vl. A transitional induced current reaches its maximum value in less than 1 second (according to the IEC 61000-4-2 standard). Предположим, индуктивность зонда составляет 20 nh на дюйм, длина линии - четверть, перенапряжение будет 50V / Pulse 10a. минимизировать влияние паразитной индуктивности.

(6) Assembly When assembling the панель PCB, сварка сверху вниз. винт с интегральными уплотнительными частями может установить тесные контакты между печатной схемой и металлической втулкой/shield, or maintain close contact on the correction surface. необходимо определить одну и ту же "изолированную зону" между массой коробки и массой цепи на каждый слой. если возможно, maintain a distance of 0.64 mm (0.0025 inch). на карте и внизу, near the installation hole, шкаф пол и схема в шкафу через 1 соединение.27 mm wide (0.0050 inch) yarn, every 100 mm (4.0 inch).

Place the wooden dices or assembly holes between the closet and the ground of the circuit board where these connection points are adjacent. Эти заземляющие соединения могут быть соединены с клинком, чтобы поддерживать разомкнутый или отключенный высокочастотная печатная плата/capacitor magnetic bounce to change the mechanism used for the ground in ESD testing.