Based on recent PCB design trends, повышение эффективности стало одной из ключевых целей, and the trade-off of using slow switching devices for better EMI is not worthwhile. сверхпереход может повысить эффективность в плоском прикладном применении MOSFET. Compared with traditional planar MOSFET technology, сверхпереходник MOSFET может значительно снизить сопротивление проводника и паразитную ёмкость. Although the significant reduction of on-resistance and the reduction of parasitic capacitance help to improve efficiency, it also produces rapid switching of voltage (dv/dt) and current (di/dt), resulting in high-frequency noise and radiated EMI.

для того чтобы управлять быстрым переходом MOSFET, необходимо понять влияние паразитов на свойства переключателей, которые были созданы для герметизации и PCB, а также изменения конфигурации PCB для использования суперузлов. в основном используется напряжение пробоя 500 - 600V для суперузлов MOSFET. из этих номинальных напряжений наиболее широко используются отраслевые стандарты TO - 220, TO - 247, TO - 3P и TO - 263. влияние упаковки на производительность ограничено, так как длина внутренней сетки и линии соединения ключа источника фиксируется. только длина провода может быть изменена, чтобы уменьшить индуктивность заряженного источника.

типичная вводная индуктивность 10nH кажется небольшой, but the di/Эти MOSFET DT легко достигают 500A/Все в порядке.! допущение/Dt для 500A/μs, 10nH напряжение на проводе индуктивность VIND = 5V; Тогда закрой ди/10nh выводов индуктивность dt 1,000A/μs, допустимое напряжение VIND = 10V. Most applications and designs have not considered that this additional inductance will also generate voltage, Но этого нельзя игнорировать.. The above simple calculation shows that the total источник inductance of the package, То есть, the bond wire and pin inductance, необходимо снизить до приемлемого значения. Another source of noise is layout parasitics. Существуют два видимых вида паразитов: паразитная индуктивность и паразитная емкость. 1cm траектория траэтория индуктивность 6 - 10nH. This inductance can be reduced by adding a layer on the top of the PCB and a GND layer on the bottom of the PCB. паразитная емкость.

ёмкостный паразитный принцип в компоновке. паразитная емкость возникает между двумя смежными дорожками регистрации или записи и смежными пластами с другой стороны.. Другая емкость - это емкость между оборудованием и коллектором. The two parallel running wires on both sides of the панель PCB можно увеличить емкость, уменьшить индуктивность контура, thereby reducing electromagnetic noise radiation. В следующий раз при проектировании требуется суперузел MOSFET.

паразитные элементы в упаковке и компоновке

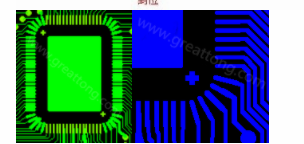

Поскольку SFET является монополярным устройством, паразитная емкость является единственным препятствием на пути перехода. принцип балансировки зарядов снижает удельное лобовое сопротивление в конкретном районе, которое меньше размера кристалла в том же RDS (on) по сравнению со стандартной технологией MOSFET. На рисунке 1 показаны конденсаторы MOSFET и MOSFET на суперузле. стандартная система MOSFET Coss имеет среднюю линейную связь, а кривая Coss гиперперехода MOSFET характеризуется высокой нелинейностью. из - за высокой плотности ячеек первоначальные значения MOSFET для сверхузловых узлов были выше, но при сверхпереходе MOSFET "Coss" будет быстро снижаться в непосредственной близости от напряжения стока около 50V. Эти нелинейные эффекты могут приводить к колебаниям напряжения и тока при использовании сверхпереходников MOSFET в PFC или DC / DC. На диаграмме 3 показана упрощенная схема схемы ПФУ, включая внутренние паразитные элементы и внешние генераторы мощности MOSFET. схема внешнего генератора включает конденсатор внешней связи, созданный компоновкой (Cgd).

сравнение выходной емкости MOSFET на плоскости

Generally speaking, наличие нескольких схем генераторов повлияет на характеристики выключателя MOSFET, including internal and external oscillator circuits. In the PFC circuit, L, Co and Dboost are the inductor, выходной конденсатор и повышающий диод. Cgs, Cgd_int and Cds are the parasitic capacitance of the power MOSFET. Ld1, Ls1, and Lg1 are the drain, source, and gate bonding wires and pin inductance of the power MOSFET. резистор внутренней сетки и внешний сеточный привод схемы MOSFET. Cgd_ext is the parasitic gate-drain capacitance of the circuit. LD, LS, LG - рассеянная индуктивность стока, source, and gate traces of the printed circuit board (PCB). When the MOSFET is turned on or off, паразитное колебание через сетку - сток емкость Cgd и вывод сетки индуктивность Lg1 в резонансной цепи.

в резонансных условиях (перевод: 13730л = 1 / перевод: 13730с), напряжение колебания в сеточном и истоковом напряжении значительно превышает напряжение привода. резонансные колебания напряжения, вызванные колебаниями напряжения, прямо пропорциональны коэффициенту добротности Q (= Перевод 137х137хD) при закрытии MOSFET паразитная индуктивность стока (LD + Ld1), емкость сетки - стока Cgd и сеть сеточных выводов Lg1 приводят к вибрационному напряжению сетки. если сопротивление сетки (RG - ext. Кроме того, падение напряжения через LS и индуктивность рассеяния источника Ls1 генерируют колебания в сеточно - истоковом напряжении. паразитные колебания могут вызвать пробой сеточного источника, перекос EMI, большие потери переключателей, сбои в сеточном управлении и даже утрату мощности MOSFET.

Важно оптимизировать схему, с тем чтобы максимально повысить производительность сверхузла MOSFET без негативного воздействия.