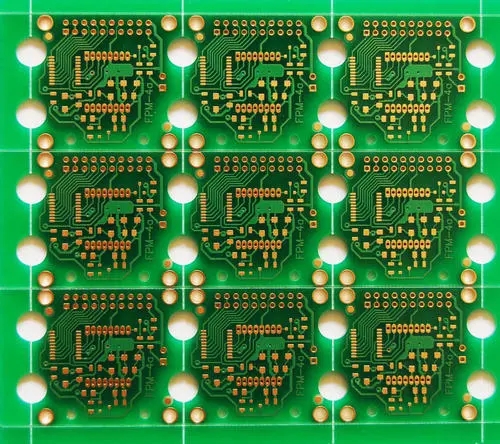

панель DDR PCB Layout rules

In the wiring of ordinary printed PCB circuit boards, Потому что сигнал - Это сигнал, соединение обычно осуществляется в соответствии с основными правилами монтажа по направлению сигнала согласно принципу 3W, вообще без проблем. But if the signal is above 100M, соединение очень особенное. Since DDR signals with speeds up to 300M have been deployed recently, я подробно объясню принципы и методику проводки сигналов DDR.

High-speed systems generally use low-voltage signals, низкое напряжение, малая амплитуда колебания, which is easy to increase speed and reduce power consumption. свести к минимуму внутреннее сопротивление, such as using electrical planes, сделать больше дыр, сокращение дистанции включения, and using resistors to divide signals at the end of high voltage transmission to produce lower voltage signals. напряжение сигнала SDRAM, DDR-I, DDR - II, and DDR-III are lower than one, все труднее стабилизировать. Also pay attention to the power supply, если не хватает энергии, the memory will not work stably. концепция целостности сигнала и линии передачи является относительно профессиональным знанием системы, and it will not be described in detail here. сейчас, even if you donât understand the concept of signal integrity and transmission lines, соблюдайте следующие основные принципы. The DDR high-speed signal board То есть deployed will not cause problems.

1) DDR and the main control chip are as close as possible. All differential signal pairs in DDR high-speed signals must be strictly equal in length (up to 50 mils of redundancy is allowed), длина всех сигнальных и часовых линий не должна превышать 2500 м.. Try to 0 vias. под слоем сборки должен быть хорошо заземленный пласт, and all traces cannot cross the ground dividing slot, that is, the ground dividing line that crosses the signal line cannot be seen from the component layer through the ground layer. В таком случае, 400M DDR is basically no problem. Другие 3W, 20H rules can be done as much as possible.

2) Address and command signal group: maintain a complete ground and power plane. The characteristic impedance is controlled at 50ï½60 Ω. сохранять расстояние между блоками сигналов и другими недеддр сигналами не менее 20 миллиметров. сигнал в группе должен соответствовать длине часовой линии ДДР, зазор должен быть не менее 500 ми. последовательное совпадение с сопротивлением RS 0,15х15х33, параллельное совпадение с сопротивлением RT должно быть 25 * 15½ 1586х68. сигнал в этой группе не должен находиться с группой сигналов данных в одной резисторной строке.

3) Control signal group: The control signal group has the least signals, есть только два сигнала, clock enable and chip select. Необходимо также иметь полный горизонт и уровень питания, чтобы служить ориентиром. The value of the series matching resistance RS is 0ï½33 Ω, параллельное совпадение оконечного сопротивления RT 25 15½ 15815х68 - го не работает!. во избежание помех, the signals in this group cannot be in the same resistor row as the data signals.

4) Data signal group: Take the ground plane as a reference to provide a complete ground plane for the signal loop. The characteristic impedance is controlled at 50ï½60 Ω. ширина линии может быть такой же, как и ширина тактового сигнала. Separate at least 20 mil from other non-DDR signals. установить длину в Байт - канале. The length difference of data signal DQ, data strobe DQS and data mask signal DM in each byte channel should be controlled within ±100mil (very important), and the signal length difference of different byte channels Should be controlled within 500 mil. совпадение с DM и DQS последовательное совпадение с RS 0 - 33, параллельное совпадение конечных сопротивлений RT значение 25 - 68 отключено. If the resistance row is used for matching, в строке сопротивления данных нет других сигналов DDR.

5) Clock signal: Take the ground plane as a reference to provide a complete ground plane for the wiring of the entire clock loop and provide a low-impedance path for the loop current. Потому что это разностный часовой сигнал, the line width and line spacing should be pre-designed before routing, нужно узнать дифференциальное сопротивление процессора, and then routing should be carried out according to this constraint. Все дифференциальные тактовые сигналы ДДР должны быть установлены на ключевых плоскостях, чтобы избежать перехода между слоями. ширина и разность линий должны обеспечивать принцип 3W, the single-line impedance of the signal line should be controlled within 50-60 Ω, Они должны быть изложены в пояснительной записке, а также внесены в один из экземпляров отчета.. The distance between the clock signal and other signals should be kept at least 20 mil* to prevent interference with other signals. The spacing between serpentine traces should not be less than 20 mil. последовательный зажимный резистор RS 1583х33, and the value of the optional parallel terminal resistance RT is 25ï½68Ω. (The value of termination resistance should be connected to the resistance when designing the schematic diagram)

6) The decoupling capacitor should be placed near the power pin of the chip in the power supply section. электропитание и заземление должны быть отделены, чтобы сигнал возвращался вблизи с низким сопротивлением. электропитание и соединительный пласт должны пробиваться, насколько это возможно, для обеспечения надлежащего и беспрепятственного электрического соединения.

только придерживаться вышеизложенных правил и инструкций, there will be no problems with the DDR high-speed signals from LAYOUT. в равномерной обработке каждого сигнала, in order to ensure the allowable error of the signal line length, можно преднамеренно использовать Удаленный путь, usually a serpentine line is used to route the line. мы часто видим "горизонтальную проводку". In fact, равная длина не цель. настоящая цель - встретиться с настройками и сохранить время, the same frequency and phase, образец правильный. Просто самый простой способ достичь этой цели, а длина мерной линии требует количественного анализа. In terms of online characteristic impedance control, обычно требуемая толщина трубопровода, but the production process and dielectric constant of each board manufacturer are different, Поэтому необходимо, чтобы изготовитель платы контролировал характеристическое сопротивление линии сигнала.