представление

Уровень сигнала относится к качеству сигнала в цепной системе. Если сигнал может быть передан от источника к приемному концу без искажений в течение требуемого времени, говорят, что сигнал является полным. с быстродействующей полупроводниковой технологией и повышением скорости вывода переключателей интегральных схем, проблемы целостности сигнала (включая перерегулирование и недорегулирование сигнала, звук, отражение, обнаружение, отскок земли, сортировку) стали одной из проблем, на которые следует обратить внимание в высокопроизводительных системах. скорость проектирования печатных плат. . обычно, частота цифровой логической схемы достигает или превышает 50 МГц, а схема, работающая на этой частоте, занимает более 1/Общесистемный, можно назвать быстродействующей схемой. Фактически, по сравнению с частотой самого сигнала частота гармоники фронта сигнала выше, а быстрые изменения (нарастание и спад) сигнала вызывают неожиданные эффекты передачи сигнала. Это также является источником проблем с целостностью сигнала. следовательно, как полностью учесть факторы целостности сигнала в процессе проектирования высокоскоростной печатной платы и принять эффективные меры контроля для повышения качества проектирования схемы, является проблемой, которую необходимо учитывать.

With the help of the powerful Cadence SPEECTRAQuest simulation software, using the IBIS model to perform signal integrity simulation analysis on high-speed signals is an efficient and feasible analysis method that can find signal integrity problems, и оптимизация вопросов, связанных с полнотой сигнала по результатам имитации, so as to achieve the purpose of improving the design quality and shortening the design cycle.

Пример 1 приложения

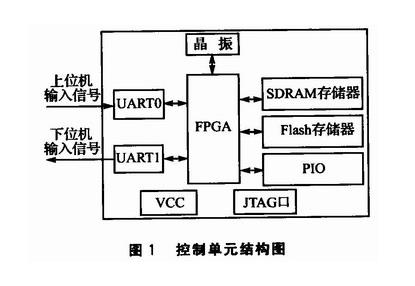

Данная статья предназначена для управления модулями во всей системе для передачи кодированных сигналов от наземных приемных устройств в центр обработки данных основной станции. конкретный рабочий процесс заключается в том, чтобы сначала сохранить данные хоста, а затем проверить и вычислить с помощью ошибки, выбрать путь с наименьшей частотой ошибок в качестве пути передачи данных, и, наконец, передать хранимые данные хоста в центр обработки данных основной станции для обработки. после комплексного рассмотрения был выбран Cyclone II - 2C8 Altera в качестве основного кристалла, а также внешние расширенные SDRAM, Flash, различные схемы ввода / вывода и интерфейс MAX232 в сочетании с набором инструментальных средств для разработки программного обеспечения Nios II. структура модуля управления показана на диаграмме 1.

The clock frequency of CycloneII-2C8 is up to 150 MHz or more. Because the data storage area inside FPGA is relatively small, SDRAM для расширения внешней памяти данных. SDRAM adopts Hy-nix Company's HY57V651610/SO, the clock frequency reaches above 75 MHz. поэтому, it is necessary to consider the signal integrity problems caused by the excessively high signal frequency. Я выбрал мощное программное обеспечение Cad, интегрированный проект, PCB Layout, скоростной имитационный анализ. It can solve the problems related to electrical performance in all aspects of the design and greatly improve the design. процент успеха.

2 Key signal topology and simulation

The higher frequency parts in this system are FPGA and SDRAM. частота часов FPGA может быть выше 150 МГц, тактовая частота SDRAM может быть выше 75 МГц. Because the internal high frequency of FPGA has no effect on other devices, связь между FPGA и SDRAM бесшовны, the signal integrity directly affects whether FPGA can read and write SDRAM correctly. In PCB design, SPECTRAQUEST с использованием программного обеспечения Cadence, анализ полноты сигнала с использованием модели IBIS, and the impedance matching and topology structure are optimized to ensure the normal operation of the system. Здесь только отражение сигнала и помехи, and other simulations are similar.

2.1 переосмысление

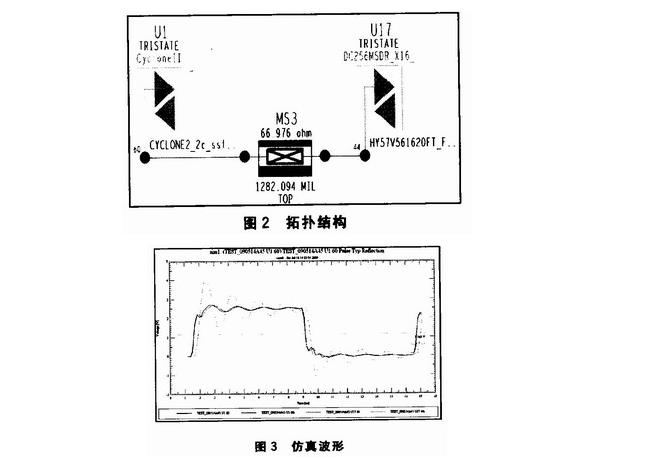

конец отправки для 44 ссылок HY57V561620, the receiving end is 60 pins of Cyclone II, возбуждение - квадратичная волна 66MHz. Figure 2 shows the topological structure, На рисунке 3 показаны смоделированные формы волн.

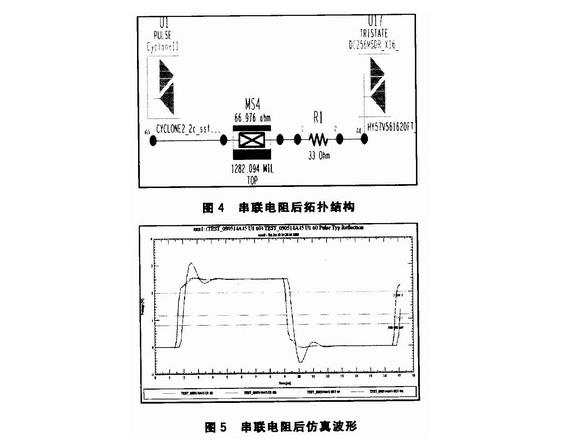

It can be seen from the simulation waveform that the waveform distortion is caused by the signal reflection, и возник явный вызов. The existence of the ringing phenomenon causes the signal to cross the level logic threshold many times, Это приводит к нарушению логической функции. эффективный способ снижения шума вызова состоит в том, чтобы соединить небольшое сопротивление с цепи, which provides damping for the circuit, можно значительно уменьшить амплитуду вызова, сократить время его колебания, while hardly affecting the circuit speed. в инженерном применении, the resistance is usually 33 Ω. на рис. 4 и 5 показано топологическое строение и моделирующая форма колебаний после последовательных сопротивлений.

явление вызова после тандемного сопротивления было хорошо устранено. На самом деле, это решение называется совпадением импедансов. импеданс занимает чрезвычайно важное место в вопросе целостности сигнала.

2.2 соучастие

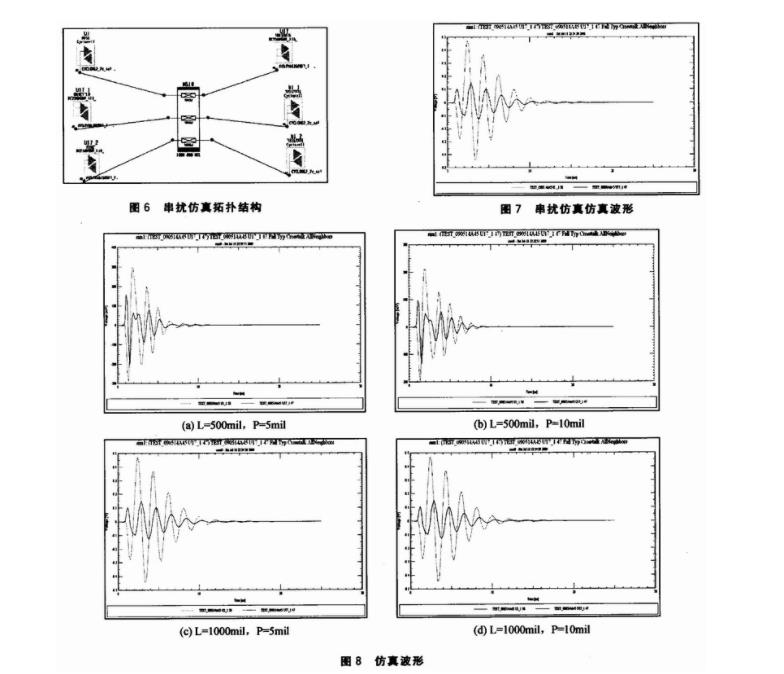

извлечение SD u DQLO (59 труб, соединяющих Cyclone II, и 45 труб, соединяющих HY57V561620), SD DQ DQll (58 шт, соединяющих Cyclone II, и 47 шт. HY57V561620), SD DQ - L2 (57 шт, соединяющих Cyclone II, и 48 шт. HY57V561620) для моделирования последовательности действий между ними. среди них, SD DAU DQL как сеть для атаки, SD Dieu DQLO и SD Lau D - QL2 как сеть для атаки. их топологическая структура и аналоговая форма волны показаны на рисунках 6 и 7 (параллельная длина связи линии передачи - L = 1000 миллиметров, шаг P = 5 миллиметров).

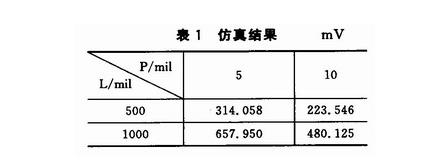

The simulation waveform is shown in Figure 8. Как видно из диаграммы 7, соучастие оказывает значительное воздействие на подвергшиеся нападению сети. последовательный значение.95 mV is related to the parallel coupling length L and spacing P of the transmission line. Чем меньше длина связи, Чем больше шаг. The smaller the crosstalk. Результаты моделирования показаны в таблице 1.

поэтому, when making the PCB, в допустимых случаях следует сводить к минимуму параллельную длину между разными профильными сигнальными линиями, the spacing between them should be widened, ширина и высота некоторых линий должны быть изменены. Конечно, there are many factors that affect crosstalk, например, время нарастания направления и частоты сигнала от источника помех, which should be considered comprehensively.

Concluding remarks

In this high-speed PCB design of the control unit, the powerful Cadence software was used to achieve good results from the production of schematic diagrams, высокоскоростной имитационный анализ. According to the reasonable topology and layout obtained by SPEECTRAQuest simulation analysis, планшет может нормально работать. This design method greatly shortens the hardware debugging time, повысить эффективность работы, and saves design costs.