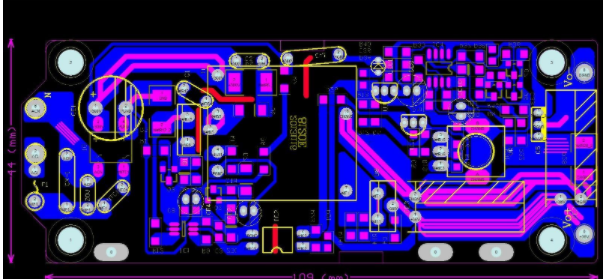

This article focuses on дизайнер PCB кто использует IP, and further uses topology planning and routing tools to support IP to quickly complete the entire PCB design. Как показано на диаграмме 1, the design engineer has the responsibility to obtain IP by arranging a small number of necessary components and planning the critical interconnection paths between these components.

получение IP - адреса, IP - информация может быть доступна дизайнеру PCB, дизайнер PCB завершит оставшуюся конструкцию. дизайнер PCB further use topology planning and routing tools to support IP to quickly complete the entire PCB design. Теперь нет необходимости в том, чтобы получить правильное проектное намерение за счет процесса взаимодействия и итерации между инженером и дизайнером PCB. The design engineer has obtained this information and the result is quite accurate, Это очень помогло разработчикам PCB. In many designs, инженер - конструктор дизайнер PCB необходимо выполнить интерактивную компоновку и монтаж, Это может отнимать много ценного времени у обеих сторон. From past experience, необходимо взаимодействие, Но это.

The preliminary plan provided by the design engineer may only be a manual drawing, отсутствие надлежащей доли компонента, bus width or pin output prompts.

когда дизайнер PCB участвует в проектировании, инженеры, использующие Топологические методы планирования, могут получить некоторые компоненты компоновки и взаимодействия. для такого проектирования могут также потребоваться компоновка других компонентов, сбор другой структуры IO и шины, а также завершение всех межсоединений.

дизайнер PCB need to adopt topology planning and interact with the схема PCB реализация оптимальной компоновки и взаимодействия компонентов в компоненте, Таким образом, повысить эффективность проектирования PCB. With the completion of the layout of key areas and high-density areas and the acquisition of topology planning, компоновка может быть произведена до окончательного топологического планирования. Therefore, Некоторые Топологические маршруты могут быть использованы в существующих схемах. Although they have a lower priority, Они все еще нуждаются в связях. Therefore, часть планирования разворачивается вокруг компоновки компонентов производства.

Кроме того, Планирование на этом уровне может потребовать дополнительных подробностей, с тем чтобы обеспечить необходимый приоритет для других сигналов. некоторые препятствия перед автоматической маршрутизацией конкретной шины могут предоставить алгоритму другие параметры маршрутного слоя. Since the bus is organized into tight lines on the first layer, конструктор начал Планирование перехода на третий уровень, with the details "3", и рассчитайте расстояние до шины через PCB. Note that this topology path on layer 3 is wider than the top layer because it requires extra space to accommodate the impedance. In addition, the design also specifies the exact location of the layer transition (17 holes). при перемещении топологических дорожек с правой стороны диаграммы 3 на деталь "4", many single-bit T-shaped connection points need to be drawn from the topological path connection and each component pin. дизайнер PCB Опция для сохранения большей части соединений на третьем этаже, а также для проникновения в другие слои для соединения с выводом компонента.

Таким образом, они нарисовали топологическую область, показывающую связь между первичным пучком и четвертым (розовым) слоем, соединяющую элемент Т - образные контакты со вторым слоем, а затем соединяющие его через другие отверстия с выводом устройства. топологический путь на третьем этаже будет продолжен с подробным сообщением "5", чтобы соединить активные устройства. Затем эти соединения соединяются с активными зажимами и отсоединяются к резистору нижней вытяжки в активных приборах.

Конструкторы используют другую топологическую региональную норму, связывающую третий слой с первым слоем, где выводом элементов являются активные приборы и нисходящие резисторы. подробное планирование этого уровня может быть завершено примерно через 30 секунд. после получения программы разработчик PCB может пожелать сразу же подключиться к сети или создать новую топологическую схему, а затем завершить все Топологические программы с помощью автоматической проводки. от запланированного завершения до автоматической проводки результатов меньше 10 секунд. На самом деле, эта скорость не важна. На самом деле, если проигнорировать намерения конструктора, автоматическая проводка будет очень плохой, это пустая трата времени. высококачественная автоматическая проводка занимает около 10 секунд. повысив уровень абстрактного планирования до топологии, продолжительность всего взаимодействия значительно сократилась. перед началом межсоединений конструкторы имеют очень четкое представление о плотности и возможностях выполнения проектирования. например, почему это должно быть сохранено в дизайне? Почему бы не продолжить планирование и не добавить нить сзади? Когда планируется полная топология?

если вы рассмотрите приведенный выше пример, то можно абстрактно применить план к другому плану, а не к 17 самостоятельным сетям, в каждой из которых много сегментов и дыр. Эта концепция очень важна при рассмотрении заявок на изменение работ (экология, проект).

В приведенном ниже примере работ по внесению изменений в перечень работ (ECO) вывод выводов FPGA еще не завершен. Проектировщики информировали конструктора ПКБ об этом факте, однако по причинам, связанным с графиком работы, им необходимо, по возможности, продвинуться вперед в разработке проекта до завершения вывода вывода вывода вывода выводов из FPGA. в тех случаях, когда известно о выводе выводов, конструкторы ПКБ приступили к планированию пространственного пространства FPGA, а конструкторы одновременно завершили планирование и рассмотрели вопрос о внедрении в состав FPGA другого оборудования. первоначально планировалось, что IO будет расположена на правой стороне FPGA, но сейчас находится на левой стороне FPGA, что привело к тому, что вывод пяток полностью отличается от первоначального плана.

дизайнер PCB can use topology planning tools at the beginning of the design, также можно использовать после того, как инженер - конструктор получит IP, depending on who uses this flexible tool to best adapt to their design environment. топологическая проводка предоставляется только по плану или замыслу конструктора высокое качество PCB wiring results. экология, topology planning is much faster than a separate connection operation, Таким образом, Топологические монтажные устройства могут использоваться быстрее, чем ECO, Таким образом, можно получить быстрые и точные результаты.