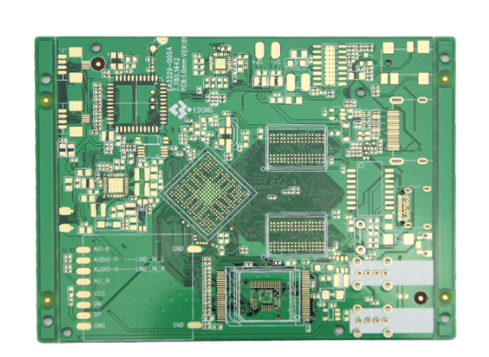

Common sense of high frequency PCB wiring (4)

1. С чего начать плата цепи пуск отладки?

As far as digital circuits are concerned, первый шаг - последовательное определение трех задач: 1. Acknowledge that all power values have reached the planning requirements. Некоторые системы с несколькими источниками энергии могут нуждаться в конкретных критериях последовательности и скорости питания. 2. Acknowledge that all clock signal frequencies are operating normally and there are no non-monotonic problems on the edges of the signal. три. Acknowledge whether the reset signal meets the standard requirements. если это нормально, the chip should announce the first cycle (cycle) signal. След., debug according to the operating principle of the system and the bus protocol.

когда размеры платы фиксируются, то, как правило, при планировании необходимо принимать больше функций, чтобы увеличить плотность линии PCB, однако это может привести к увеличению помех линии следов и увеличению сопротивления линии следа. не могли бы вы поделиться с экспертами методиками планирования высокой плотности PCB (> 100MHz)?

плановое время высокая плотность PCB, crosstalk (crosstalk interference) really needs special attention, Потому что это сильно влияет на точность времени и сигнала. Here are a few places to pay attention to:

Control the connection and matching of the characteristic impedance of the trace.

размер интервала слежения. обычно видно, что интервал в два раза превышает ширину линий. Благодаря моделированию можно понять влияние интервала между дорожками на время и целостность сигнала и найти минимально допустимый интервал. Результаты различных чипов могут быть разными.

выберите соответствующий метод прекращения.

не допускать того, чтобы проводки в двух соседних слоях были одинаковыми, даже если они укладываются сверху или снизу, поскольку такие помехи больше, чем помехи на соседней проводке на одном и том же этаже.

Неактивная панель/buried vias to increase the trace area. Однако, the production cost of the панель PCB увеличиться. It is indeed difficult to achieve complete parallelism and equal length in practice, но все же необходимо сделать как можно больше.

Кроме того, можно сохранить разностный конец разъема и сопутствующего конца модуля для плавного влияния на точность времени и сигнала.

обычно для имитации фильтра в месте питания используются схемы LC. Но почему эффект фильтрации LC иногда хуже, чем у РК?

сравнить эффект фильтрации LC и RC, необходимо рассмотреть целесообразность выбора частот фильтрации и значений индуктивности. Because the inductance (reactance) of the inductor is related to the inductance value and frequency. Если уровень шума у источника низкий, значение индуктивности недостаточно большое, the filtering effect may not be as good as RC. Однако, the value to be paid for using RC filtering is that the resistor itself consumes energy and has poor efficiency, и обратите внимание на приемлемую мощность выбранного резистора.

какой способ выбрать значение фильтра и емкости?

В дополнение к частоте шумов, которую необходимо фильтровать, при выборе значения индуктивности следует также учитывать способность мгновенного тока реагировать. если у выводного конца LC есть возможность мгновенно выводить большой ток, то избыточные значения индуктивности предотвратят большой ток через индуктивность и повысят шумы текстурных волн. емкость связана с допустимым уровнем шума. Чем меньше шумов, тем больше емкость. конденсатор ESR / ESL также оказывает влияние. Кроме того, если LC будет помещена на выходную точку регулируемого питания переключателя, то следует учитывать полярную / нулевую стабильность LC, а также стабильность контура управления с отрицательной обратной связью (управление с отрицательной обратной связью). влияние.

как можно выполнить требования EMC, не создавая чрезмерного финансового давления?

увеличение стоимости EMC до PCB, как правило, объясняется увеличением количества коллекторных пластов для усиления экранирования, а также увеличением количества ферритовых магнитов, дросселей и других высокочастотных гармоник для подавления высокочастотных гармоник. Кроме того, обычно необходимо развернуть защитные структуры других организаций, с тем чтобы вся система прошла по требованиям EMC. Ниже приводятся лишь некоторые электромагнитные радиационные эффекты схем для снижения навыков планирования панелей PCB.

максимально использовать устройство с медленной скоростью преобразования сигнала, чтобы уменьшить высокочастотную составляющую сигнала. обратите внимание на положение высокочастотного оборудования, не приближайтесь слишком близко к внешнему соединителю.

обратите внимание на совпадение сопротивлений высокочастотного отражения и излучения с высокочастотными сигналами, проводами и траекториями их обратного течения.

на каждом устройстве достаточно развязывающих конденсаторов для сглаживания слоя питания и наложения шумов на пласты. особое внимание уделяется тому, соответствуют ли частотные и температурные характеристики конденсаторов требованиям планирования.

заземление, прилегающее к внешнему соединению, может быть надлежащим образом отрезано от заземления, и заземление соединителя должно быть связано с заземлением в соседнем аппарате.

рядом с некоторыми особенно высокоскоростными сигналами вы можете правильно использовать защиту от приземления / шунт для сопровождения. Но обратите внимание на влияние защитной / разделительной линии на сопротивление характеристики линии следов. уровень питания уменьшается с поверхности земли на 20H, а H - расстояние между слоем питания и наземным слоем.

6. When there are multiple digital/аналоговый функциональный блок в a панель PCB, the usual practice is to separate the digital/аналоговое заземление. What are the reasons?

причина разделения цифровых / аналоговых заземлений заключается в том, что при переключении потенциалов выпуклых точек Цифровые схемы шумят от источника питания и заземления. размер шума зависит от скорости сигнала и размера тока. Если пласт не вырезан, а цифровые региональные схемы производят большой шум, и схемы в имитационной области очень близки, и даже если несколько мод не вставлены, имитационные сигналы все равно подвергаются шуму заземления. Это означает, что только в тех случаях, когда район аналоговой схемы находится вдали от района цифровых схем, создающих большие шумы, может использоваться метод, при котором цифровое заземление не может быть измерено как аналоговое приземление.

другой подход заключается в обеспечении того, чтобы цифровая / имитационная схема разделения и цифровые / аналоговые линии сигнализации не пересекались, чтобы не резали землю на всех панелях PCB и чтобы цифровое / имитационное заземление соединялось с этим соприкосновением. Правда?

цифровая линия аналоговых сигналов не может быть вставлена, потому что более быстрый цифровой сигнал обратного тока по маршруту следования будет идти по соседним наземным линиям ниже цифрового источника сигнала. Если сигнал нескольких мод проникает в область аналоговой схемы, то возникает шум от обратного тока.

как можно учитывать совпадение импедансов при планировании схем высокоскоростных PCB?

при планировании высокоскоростных цепей PCB одним из элементов планирования является согласование сопротивлений. значение импеданса, безусловно, связано с методикой проводки, например, расстояние между поверхностью (микрополосой) или внутренней (ленточной / двухполосной линией), базовым слоем (слоем питания или соединительным слоем), шириной линии, PCB и т.д. Иными словами, значение импеданса должно быть определено после подключения. обычно, из - за модели схемы или точности математического алгоритма, эмуляционное программное обеспечение не может принимать во внимание некоторые условия подключения, не связанные с сопротивлением. в это время принципиальная схема может сохранять только некоторые терминалы (терминалы), такие как последовательное сопротивление. сглаживание импедансов траектории разрыва. Настоящий способ решения этой проблемы - попытаться предотвратить прерывистое сопротивление при проводке.

где я могу предложить более точную матрицу IBIS?

точность модели IBIS непосредственно влияет на результаты моделирования. по существу, IBIS можно рассматривать как данные о электрических характеристиках эквивалентных схем для реальных чипов I / O буфера, которые, как правило, могут быть получены в результате преобразования модели SPICE (также может быть выбран вариант измерений, но большинство из них могут быть измерены) и производства данных SPICE и чипов, и поэтому данные SPICE, полученные от различных производителей чипов, отличаются друг от друга в том же оборудовании, данные в модели IBIS после преобразования будут соответствующим образом изменены. Иными словами, если использовать оборудование изготовителя а, то при условии, что они способны предоставить точные данные моделирования для своего оборудования, поскольку никто не знает лучше, чем они это делают. если поставщик предоставляет IBIS неточно, единственным решением является постоянное требование к производителю улучшить его.

10. плановое время высокая скорость PCB, which aspects should planners consider EMC and EMI regulations?

как правило, при планировании EMI / EMC необходимо учитывать аспекты радиации и проводимости. первый относится к высокочастотной части (> 30 МГц), а второй - к низкочастотной части (< 30мгц). Поэтому он не может сосредоточиться только на высоких частотах и игнорировать низкие частоты. план EMI / EMC должен учитывать ориентацию оборудования, организацию стека PCB, способы подключения, выбор оборудования и т.д., а если раньше не будет улучшена организация, то переработка превысит прибыль и увеличит расходы.

например, расположение часового генератора не должно быть близко к внешнему соединению. сигнал с большой скоростью следует передавать как можно больше на внутренний слой. обратите внимание на совпадение характеристических импедансов с базовым слоем, чтобы уменьшить отражение. чтобы снизить высоту, скорость преобразования сигналов, движущихся устройством, должна быть как можно меньше. при выборе развязывающего / обходного конденсатора частотный элемент должен следить за тем, отвечает ли его частотная реакция требованиям для снижения уровня шума на уровне питания.

Кроме того, pay attention to the return path of the high-frequency signal current to make the loop area as small as possible (that is, the loop impedance as small as possible) to reduce radiation. You can also use the method of cutting the ground to control the scale of high-frequency noise. наконец, appropriate Select the chassis ground between the панель PCB А квартира.