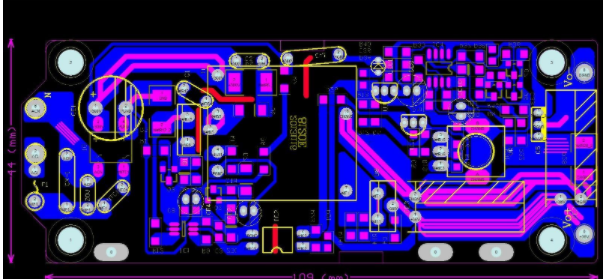

Bu makale, IP kullanan PCB tasarımcılara odaklanır ve bütün PCB tasarımını hızlı tamamlamak için IP desteklemek için topoloji planlama ve yönlendirme araçlarını kullanır. Şekil 1'den görülebilir ki, tasarım mühendisi, bu komponentler arasında kritik bağlantı yollarını düzenleyerek IP'i elde etmek için sorumluluğu var.

IP alındığında, IP bilgileri PCB tasarımcısına teslim edilebilir ve PCB tasarımcısı kalan tasarımı tamamlayacak. PCB tasarımcıları tüm PCB tasarımını hızlı tamamlamak için IP desteklemek için topoloji planlama ve yönlendirme araçlarını kullanır. Şimdi tasarım mühendisi ve PCB tasarımcısı arasındaki etkileşim ve tekrarlı süreç aracılığıyla doğru tasarım niyetini elde etmeye gerek yok. Tasarım mühendisi bu bilgileri aldı ve sonuç tamamen doğrudur. Bu, PCB tasarımcısına büyük yardımdır. Çoğu tasarımlarda tasarım mühendisleri ve PCB tasarımcıları iki parti için çok değerli zamanı tüketebilecek etkileşimli tasarım ve rotasyon yapmalıdır. Geçmiş tecrübelerden, etkileşimli operasyonlar gerekli, ama zamanlı ve etkileşimli.

Tasarım mühendisinin sunduğu ilk plan ı sadece doğru komponent ölçüsü, otobüs genişliği veya pin çıkış prompleri olmadan elimden gelen bir çizim olabilir.

PCB tasarımcıları tasarımına katılırken topoloji planlama teknolojisini kullanan mühendisler bazı komponentlerin dizaynını ve bağlantısını alabilir. Bu tasarım da diğer komponentlerin, diğer IO ve otobüs yapılarının toplantısını ve tüm bağlantıların tamamlamasını isteyebilir.

PCB tasarımcıları topoloji planlaması ve düzenleme altında PCB düzenleme komponentleri ile en iyi düzenleme ve etkileşimli planlama sağlamak için, bu şekilde PCB tasarımın etkileşimliliğini geliştirmesi gerekiyor. Anahtar bölgelerin, yüksek yoğunluklık bölgelerinin ve topoloji planlamasının alınmasını tamamlayıp, dizim son topoloji planlamasının önünde olabilir. Bu yüzden bazı topolojik yollar mevcut düzeni kullanmak zorunda olabilir. Daha düşük öncelikleri olsalar da hala bağlantılı olmalılar. Bu yüzden planlamanın bir parçası üretilen komponentlerin düzeni çevresinde dönüyor.

Ayrıca, bu planlama seviyesi diğer sinyaller için gerekli prioriteti sağlamak için daha detay gerekebilir. Özellikle otobüs otomatik yolculuğundan önce bazı engeller diğer yolculuğu katmanların seçenekleri için algoritme sağlayabilir. Otobüs ilk kattaki sıkı çizgilere organize edildiğinden beri tasarımcı, dönüştürme kısmını üçüncü katı olarak planlamaya başlar, detaylarla "3" ve otobüsün PCB'den geçtiğini düşüner. 3. kattaki topoloji yolunun en yüksek katından genişliğini unutmayın çünkü impedance'i uygulamak için ekstra uzay gerekiyor. Ayrıca tasarım da katı geçişimin (17 delik) tam yerini belirtir. Topolojik yol 3. Şekil sağ kısmından "4" detayla aşağıya taşındığında, topolojik yol bağlantısından ve her komponent pipinden birçok T şeklindeki bağlantı noktaları çizelmeli. PCB tasarımcıları 3. katta bağlantıların çoğunu tutmayı ve diğer katlara komponent pinleri bağlamak için diğer katlara girmeyi seçiyorlar.

Bu yüzden, temel katından dördüncü katına bağlantısını göstermek için topolojik bir alan çizdiler ve birimi T-bağlantısını ikinci katına bağladılar, sonra aygıtlara bağlamak için diğer viallar kullandılar. Topolojik yol aktif aygıtları bağlamak için 3. katta detaylı bilgi "5" ile devam ediyor. Sonra bu bağlantılar etkili pinlerden aktif cihazın altında çekilme dirençlerine bağlanılır.

Tasarımcı 3. katından 1. katına bağlanmak için başka bir topoloji alanı belirlenmesini kullanır. Komponentlerin aktif cihazlar ve indirme dirençleri olduğu yerde. Bu detaylı planlama seviyesi yaklaşık 30 saniye içinde tamamlanabilir. Bu plan ı aldıktan sonra, PCB tasarımcıları hemen yola çıkarmak veya daha fazla topoloji planlaması isteyebilir ve sonra otomatik yolculuğu aracılığıyla tüm topoloji planlamasını tamamlayabilir. Planın tamamlamasından 10 saniyeden az sürer, otomatik sürücü sonuçlarına kadar. Aslında bu hızlık önemli değil. Aslında tasarımcının niyetini görmezden gelerseniz, otomatik yolculuğun kalitesi çok fakir, bu tamamen zaman kaybıdır. Yüksek kaliteli otomatik düzenleme yapmak için 10 saniye sürer. Topoloji planlamasına abstraksyon seviyesini yükseltmek üzere bütün bağlantı zamanı çok kısayılır. Ara bağlantı başlamadan önce tasarımcısın yoğunluğu ve tasarımı tamamlama potansiyeli hakkında gerçekten a çık bir anlama sahiptir. Örneğin, neden bu noktada dizaynda çizgi tutuyorsun? Neden arkadan planlamaya devam etmeye ve çizgileri eklemeye devam etmiyorsun? Tam topoloji ne zaman planlanıyor?

Eğer yukarıdaki örnekleri düşünüyorsanız, plan abstraksyonu 17 bağımsız ağ yerine, her ağda birçok bölüm ve birçok delik vardır. Mühendislik değiştirme emirlerini (ekoloji, proje) düşündüğünde bu fikir çok önemlidir.

Mühendislik Değiştirme Düzeni (ECO) Bu örnekte, FPGA pin çıkışı henüz tamamlanmadı. Tasarım mühendisleri bu gerçekliğin PCB tasarımcılarını bildirdiler, ama ilerleme sebepleri için, FPGA pin çıkışı tamamlamadan önce tasarımın mümkün olduğu kadar ilerlemesi gerekiyor. Bilinmiş pin çıkışı durumunda, PCB tasarımcıları FPGA uzayını planlamaya başladılar ve tasarımcılar planlamayı aynı zamanda tamamladılar, ayrıca diğer aygıtlardan FPGA'ye yönetmeyi düşünüyorlar. IO ilk olarak FPGA'nin sağ tarafında olması planlandı, ama şimdi FPGA'nin sol tarafında, pinin çıkışı orijinal plandan tamamen farklı olması nedeniyle.

PCB tasarımcıları tasarımın başlangıcında topoloji planlama araçlarını kullanabilir, ya da tasarım mühendisi IP'i aldıktan sonra kullanabilir, tasarım ortamına en iyi uyum sağlamak için bu fleksibil araçları kullanarak kullanabilir. Topolojik düzenleme tasarımcının plan ına ya da yüksek kaliteli PCB düzenleme sonuçlarına uyuyor. EKO'ya karşı karşılaştığında topoloji planlaması ayrı bir bağlantı operasyonundan daha hızlı, bu yüzden topoloji düzenleme ekipmesi EKO'yu daha hızlı kabul edebilir, bu yüzden hızlı ve doğru sonuçlar sağlayabilir.