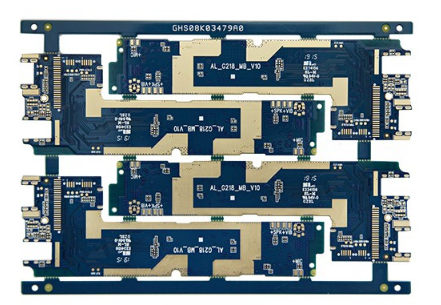

Yüksek hızlı PCB tasarımı ve düzenleme içinde, çizgi uzunluğu eşleşme genellikle gerekiyor. Bu zamanlar, sınırlı kuralları ayarlamak ve bu kuralları farklı ağ gruplara teslim etmek gerekir. Bu kısıtlıkları ayarlamanın özel adımlarını göstermek için ddr'ı örnek olarak alır.

1. PCB tasarımı ve düzenleme ihtiyaçları

DDR saat: satır genişliği 10mil, iç uzay 5mil, dış uzay 30mil. Farklı PCB tasarımı ve düzenleme gerekiyor ve farklı çift düzenleme hatası +20mil içerisinde tam olarak eşleşmelidir.

DDR adresi, çip seçimleri ve diğer kontrol çizgileri: 5 mil genişliği, 15 mil iç uzay, 20 mil dış uzay, süylü zincir topolojisinde olmalı. Bu, ddrclk çizgisinden 1000-2500 mil uzun olabilir ve daha kısa olmamalı.

DDR veri hatları, ddrdqs, ddrdm hatları: 5 mil genişliği, 15 mil iç uzay, 20 mil dış uzay, aynı PCB katında dizayn ve yol yapmak en iyisi. Veri çizgisinin ve saat çizgisinin arasındaki çizgi uzunluğu 50 mil içinde kontrol ediliyor.

2. Yukarıdaki taleplere göre PCB tasarımı Allegro'da farklı sınırlar ayarlayın.

Satır genişliği (fiziksel), sadece 3 sınır ayarlanması gerekiyor: DDR_CLK, DDR_ADDR, DDR_DATA

Yukarıdaki sınırları ayarladıktan sonra, bu sınırları ağa ekleyebilirsiniz. Bağlama... fiziksel kural setinde ve sağdaki kontrol panelde daha fazla tıklayın,

pop- up dialogu kutusu

ckn0 ve ckp0'u bul, uygulama tıklayın, açılacak

Soldaki listede NET_PHYSICAL_TYPE seçin, sağdaki alanda DDR_CLK girin ve pop up için uygulayın.

İki ağ NET_PHYSICAL_TYPE özelliğini ekledi ve değer DDR_CLK.

Aynı şekilde DDR veri çizgisinin NET_PHYSICAL_TYPEsini, veri çizgisini ve veri koruması çizgisini DDR_DATA'ya ve DDR adres çizgisinin NET_PHYSICAL_TYPEsini, çip seçim çizgisini ve diğer kontrol çizgilerini DDR_ADDR'e ayarlayabilirsiniz.

Yukarıdaki adımlar tamamlandıktan sonra, ayarlanan sınırlar bu ağ gruplara takılmalı.

Görev tablosuna tıklayın...

pop- up dialogu kutusu

Farklı sinyal grupları için kendi fiziksel sınırlarını seçin

Birisi sorabilir ki neden area1 ve a0 var? Çünkü bu sınırlar bazı yerlerde ulaşabilmek imkansız. Örneğin, bga paketinin cpu'nda, sonuçlar çıktığında, satır boşluğu 30, 20 ya da 10 mil bile ulaşamaz. Bu yerlerde, eğer bu sınırı takip ederseniz, PCB'deki doktoru yok etmek imkansız. Bu zamanlar, bu yerleri oda olarak klasifik etmek ve sonra oda özelliğini (yani oda area0, 1, etc.) eklemek için uygun sınırlar (ibir.).

Çizgi boşluğu hakkında, herkes grupun içindeki boşluğuna ve grupun dışındaki boşluğuna bölünmesi için toplam 6 sınırlar var:

DDR_CLK_INNER,DDR_CLK_OUTER,

Sadece bu altı sınırlar için çizgi ve çizgi olarak ayarlayın ve bunları yukarıdaki ihtiyaçlarına göre ayarlayın.

Kalan adımlar fiziksel ayarlar ile aynı. Ama bu zamanda görev masası sonraki olacak.

Yukarıdaki yer, PCB tasarımı için Allegro sınırlı kurallarının ayarlama adımları hakkında detaylı içerik.