Под упаковочной платой ИС (IC) понимается процесс обработки измеренной пластины в соответствии с моделью изделия и функциональными требованиями для получения самостоятельных микросхем. Упаковочные платы (IC) в первую очередь служат средой для соединения тонких кремниевых микросхем с широко расположенными печатными платами и защищают устройства от влаги.

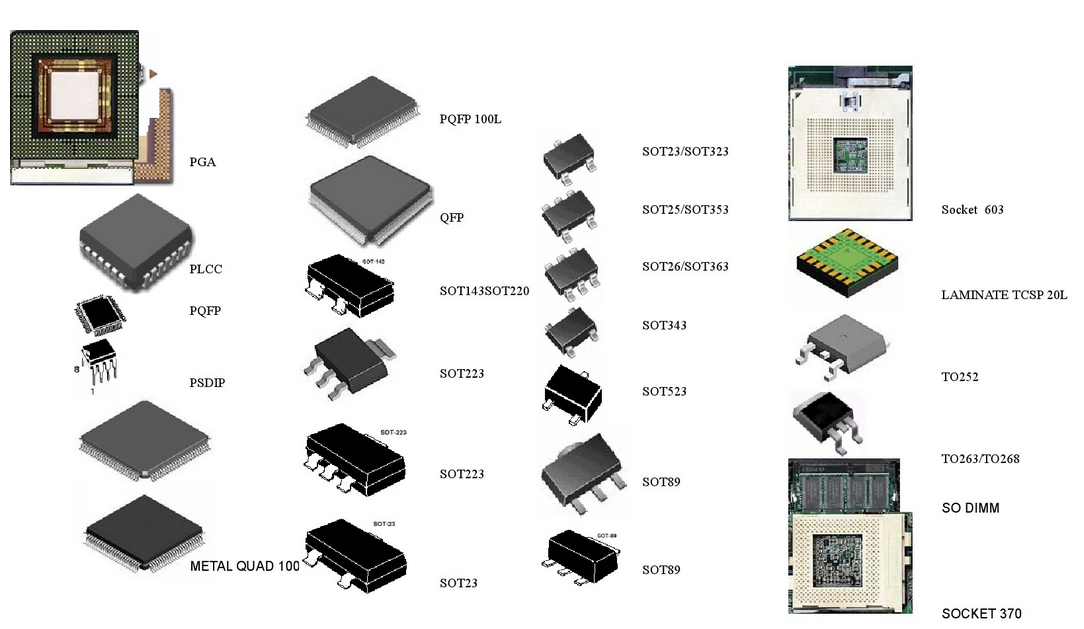

К специфическим формам упаковки относятся:

форма упаковки

1. свинцовая упаковка

В конце 1970-х гг. первым широко распространенным на рынке корпусом стал dual-in-line (DIP) - корпус из керамики и пластика. Выводы выведены с обеих сторон пакета и расположены перпендикулярно ему. Пакет можно установить на печатную плату, вставив вывод в сквозное отверстие в плате, затем зажать вывод на другой стороне платы и припаять его с помощью технологии пайки волной. Пакет рассчитан на максимальное количество выводов 40 и расстояние между пластинами 0,65 мм.

В конце 1970-х - начале 1980-х годов появился поверхностный монтаж. Выводы (штырьки) и компоненты микросхемы привариваются к поверхности печатной платы, а не проходят сквозь нее. Это позволяет использовать обе стороны платы для приклеивания микросхемы, применяя при монтаже технологию пайки оплавлением, при этом максимальное количество выводов составляет 80.

К середине 1980-х годов появились пакеты с выводами со всех сторон. Такая упаковка называется quad flat package (QFP) (вывод имеет форму крыла чайки) или lead chip carrier (вывод изогнут). J). Наиболее часто используемый типовой четырехугольный плоский пакет имеет шаг 0,65 мм или 0,5 мм и количество выводов до 208. Такие пакеты широко использовались в начале 1990-х годов на рынках жестких дисков и графики.

В конце 1980-х - начале 1990-х годов появился пакет со свинцовыми выводами с открытой площадкой. Этот пакет представляет собой четырехугольный плоский или меньший по форме пакет с обнаженным снизу торцом для склеивания микросхем. Эти открытые концы могут быть приварены к печатной плате, создавая эффективный теплоотвод для микросхемы.

Семейство корпусов miniature Lead Frame (MLF) было разработано в 1990-х годах. MLF близок к пакету Chip Scale Package (CSP), нижний выводной конец пакета используется для обеспечения электрического контакта с печатной платой, в отличие от пакетов Soic и Qual с выводом типа "крыло чайки", поэтому такой пакет помогает обеспечить теплоотвод и электрические характеристики.

2. Многослойная упаковка

Многослойная упаковка

В 1990-х годах появился новый тип упаковки, получивший название ball Grid Array (BGA), использующий в качестве материала подложки слоистые пластины. В упаковке на основе свинцовых рамок выводы могут быть выведены только на периферию упаковки... Выводы пакета с шариковым решетчатым массивом могут быть направлены к шарику припоя, расположенному в нижней части всего пакета. Первоначально типичный шаг шариков для плат упаковки BGA составлял 1,27 мм.

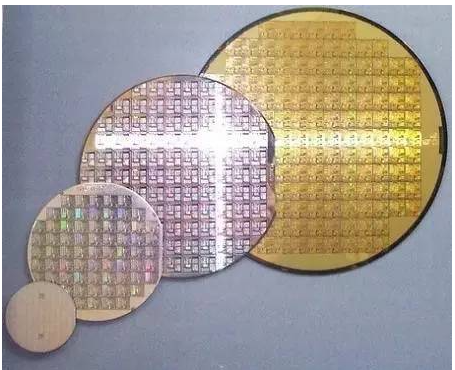

3. Упаковка на уровне пластин

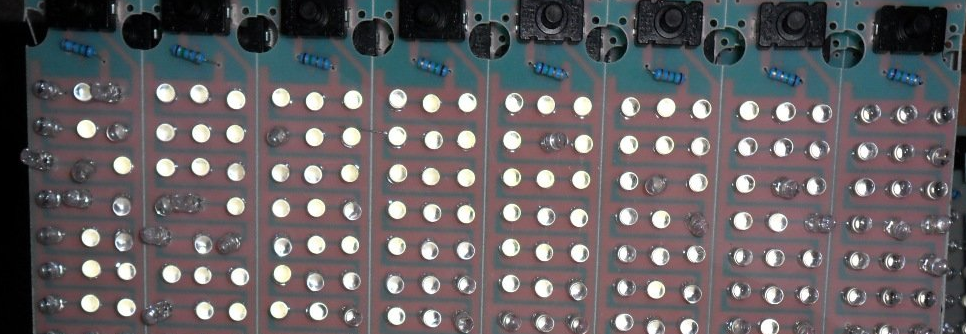

упаковка класса вафли

Когда требуется много места, наилучшим вариантом упаковки является полное отсутствие упаковки. Для получения устройств, которые могут быть установлены непосредственно на печатную плату, на уровне полупроводниковой пластины может быть проведена дополнительная обработка. Этот процесс обычно включает в себя использование слоя перераспределения для переноса мелкого шага на пластине на более крупный шаг (обычно 0,5 мм) на самом чипе, а затем создание точек неровности на функции перераспределения. Ядро будет выделено отдельно, а пакет на уровне пластины представляет собой выпуклое блочное ядро.

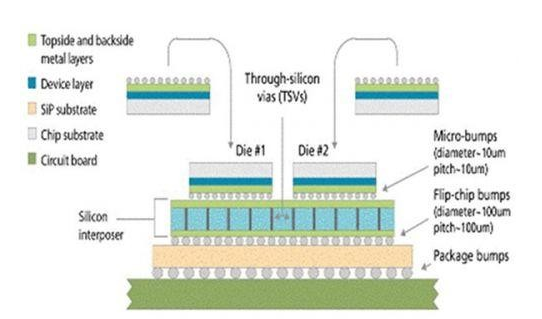

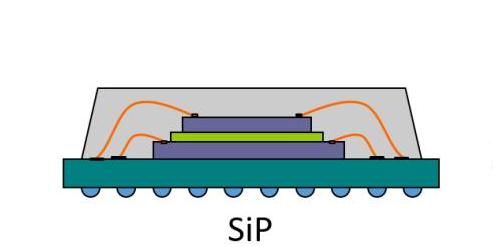

4. Инкапсуляция на системном уровне (SIP)

В настоящее время в рамках нового раунда интеграции в пакет под названием « системный пакет» (СиП) помещаются несколько чипов. многочипный пакет может быть реализован путем установки двух или более чипов в одной и той же упаковке (обычно с использованием ламинарного фундамента) или путем укладки одного чипа на другой в одной и той же упаковке.

5. Развитие технологии межсоединений в упаковке

Интерконнект описывает способ соединения микросхем с подложкой пакета. В большинстве корпусов сначала корпус пакета соединяется с передней поверхностью выводов для подключения микросхемы на подложке (выводная рамка или наслоение), а затем площадка микросхемы соединяется с выводным пальцем подложки с помощью золотой или алюминиевой проволоки. Превосходство. Такая технология межсоединения называется lead bonding и подходит для большинства упаковочных приложений. Новая схема межсоединения называется Flip Chip Bonding. На поверхности микросхемы в месте расположения площадки формируется проводящий бугорок. Затем микросхема переворачивается и подключается непосредственно к подложке. В большинстве случаев используется многослойная подложка. Для приклеивания шариков используется процесс пайки оплавлением. После соединения с подложкой и пайки оплавлением между микросхемой и подложкой используется процесс заполнения дна для снижения напряжений, возникающих в сварочной части устройства в процессе эксплуатации.

6. Упаковочные материалы. Пластиковая упаковка подвержена воздействию сырости и влаги. Промышленность работает над совершенствованием комбинаций пресс-форм и материалов для соединения микросхем, чтобы исключить необходимость сухой сборки. Еще одно недавнее требование к упаковочным материалам - полное отсутствие свинца и использование "зеленых материалов", отвечающих экологическим требованиям.

7. процесс упаковки на полупроводниковой пластине Процесс полупроводниковой пластины после процесса скрайбирования был вырезан ChengXiaoJing круглый (Die), а затем вырезать полупроводниковую палку на подложке (свинцовая рамка) соответствующий остров рамки, затем использовать супертонкий с металлом (золото, олово, медь, алюминий) или между проводящей смолы чип связующей площадки и IC пакет подложки соответствующего свинца соединения, сформировать схему; отдельные чипы затем заключены и защищены пластиковый корпус. 7. процесс упаковки на полупроводниковой пластине Процесс полупроводниковой пластины после процесса скрайбирования был вырезан ChengXiaoJing круглый (Die), а затем вырезать полупроводниковую палку на подложке (свинцовая рамка) соответствующий остров каркаса, затем использовать супертонкий с металлом (золото, олово, медь, алюминий) или между проводящей смолы чип связующей площадки и IC пакет подложки соответствующего свинца соединения, сформировать схему; отдельные чипы затем заключены и защищены пластиковый корпус. После упаковки в пластиковый корпус необходимо выполнить ряд операций, таких как отверждение после формовки, формовка с обрезкой, нанесение гальванического покрытия и печать. После завершения упаковки готовая продукция проходит проверку, обычно через поступление материалов, тестирование, упаковку и, наконец, складирование и отгрузку. Типичный процесс упаковки: резка, загрузка, склеивание, упаковка в пластик, удаление заусенцев, нанесение гальванического покрытия, печать, резка ребер и формовка, проверка внешнего вида, испытание готовой продукции, упаковка и доставка.