Процессы проектирования чипов IC

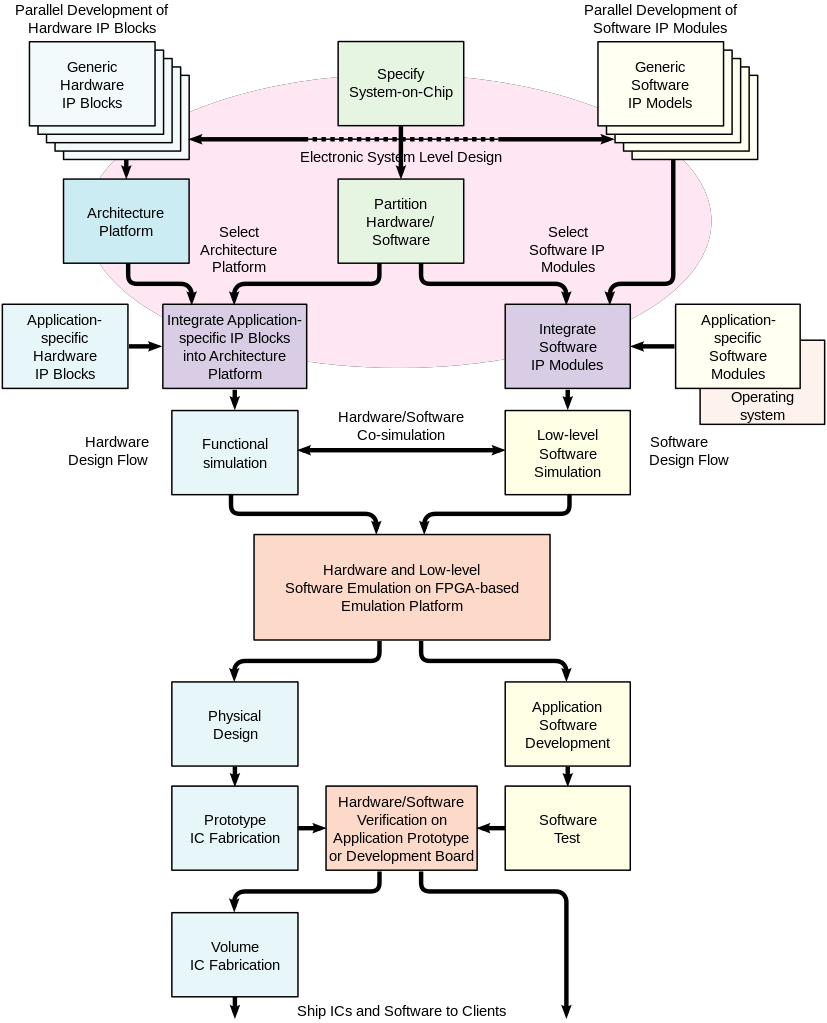

Дизайн чипов IC делится на передний и задний дизайны, передний дизайн (также известный как логический дизайн) и задний дизайн (также известный как физический дизайн) не имеют единообразных строгих границ, а процессы, связанные с дизайном, - это дизайн заднего конца. проектирование печатных плат

Дизайн передней части чипа IC:

1. Разработка спецификаций.

Как и в списке функций, спецификации чипа - это требования, которые клиенты предъявляют к компании по проектированию чипов (известной как Fabless), включая конкретные функциональные и эксплуатационные требования, которые должны быть выполнены чипом.

2. Детальный дизайн.

Fabless предлагает дизайнерские решения и архитектуру реализации в соответствии с клиентскими спецификациями и делит модульные функции.

3.Код HDL

Использовать язык описания аппаратного обеспечения (VHDL, Verilog HDL, как правило, используется отраслевыми компаниями в последнем) Модульный код описания функций, то есть фактические функции аппаратной схемы описаны на языке HDL, образуя код RTL (уровень передачи регистров).

4. Эмуляционная проверка

Эмуляционная проверка предназначена для проверки правильности дизайна кода, и стандарт проверки является первым шагом к разработке спецификации. Проверьте, точно ли дизайн соответствует всем требованиям спецификации. Нормы - это золотой стандарт правильного дизайна, и все, что не соответствует нормам, должно быть переработано и кодировано. Проверка дизайна и моделирования является итеративным процессом до тех пор, пока результаты проверки не покажут полное соответствие спецификации. Synopsys VCS и Cadence NC Verilog.

6. SТА

Статический анализ временных рядов (STA): Это фундаментальное знание цифровых схем, регистр имеет два конфликта временных рядов, и нет способа правильно отобрать и вывести данные, поэтому функция цифрового чипа, основанная на регистре, безусловно, будет проблематичной. Инструменты STA имеют Synopsys Gold Time.

7. Проверка формы

Это также категория проверки, которая функционально проверяет синтетическую сетевую таблицу (STA - таймер). Обычным методом является проверка эквивалентности. Используя в качестве ориентира HDL - конструкцию после проверки функции, сравните интегрированные функции таблицы, чтобы определить, являются ли они функциональны эквивалентными. Это делается для обеспечения того, чтобы функции схемы, первоначально описанной в HDL в процессе логического синтеза, не изменились. Форма является инструментом Synopsys. Процесс проектирования интерфейса временно записан здесь. С точки зрения дизайна, результатом дизайна передней части является получение входной схемы чипа интегральной схемы.

Встроенный дизайн микросхем IC:

1. DFT

Конструкция для испытания. Чипы часто имеют встроенные испытательные схемы, и DFT разработаны с учетом будущих испытаний. Общий подход к DFT заключается во встраивании цепочки сканирования в конструкцию для преобразования несканирующего устройства (например, регистра) в сканирующее устройство. Некоторые книги имеют подробную информацию о DFT, поэтому легко понять его, сравнивая фотографии. DFT компилятор DFT tool Synopsys

2. План этажей здания

Планировка заключается в размещении модуля макроблока чипа и определении размещения различных функциональных цепей в целом, таких как IP модуль, ОЗУ, пин ввода/вывода и так далее. Планировка может напрямую влиять на окончательную чип-зону. Инструмент Astro для синопсии

3. Организация по техническому сотрудничеству

Синтез дерева часов, проще говоря, проводка часов. В связи с глобальной командной функцией часового сигнала в цифровом чипе, его распределение должно быть симметричным для каждого регистрационного блока, так что часы от одного и того же источника часов к каждому регистру, разница задержки часов минимальна. Вот почему сигналы часов должны быть соединены отдельно. CTS tool, физический компилятор для синопсии

4. Место и маршрут

Проводка здесь является обычной проводкой сигнала, включая проводку между различными стандартными блоками (основные логические ворота). Например, мы обычно слышим, что процесс 0.13um, или 90nm процесс, на самом деле минимальная ширина металлической проводки здесь, что является длиной канала трубы MOS с микро точки зрения. Астро инструмент синопсии

5. Извлечение паразитарных параметров

Из-за сопротивления самой проволоки взаимная индуктивность между смежными проводами, емкость сцепления внутри чипа может создавать сигнальный шум, скрещивание и отражение. Эти эффекты могут вызывать проблемы целостности сигнала, приводя к колебаниям и вариациям напряжения сигнала, а в случае серьезных ошибок искажения сигнала. Очень важно проанализировать проблему целостности сигнала путем извлечения паразитарных параметров и повторной проверки. Инструмент Synopsys star-rCXt

6. Проверить физическое расположение

По завершении проводки физической схемы функции и проверки по времени проверка многих элементов, таких, как LVS (макет Vs схематическая проверка), короче говоря, представляет собой проверку схемы и логического синтеза сопоставления схем на уровне ворот; ДРК (проверка правил проектирования) : проверка правил проектирования, проверка расстояния между линиями, ширины линии для выполнения технологических требований, проверка эрс (проверка правил электроснабжения) : проверка правил электроснабжения, проверка короткого замыкания и открытого замыкания и другие нарушения правил электроснабжения; И так далее. Инструмент для Synopsys Hercules

Фактический бэкторный процесс также включает анализ потребления энергии цепи и DFM (конструкция изготовления) проблемы, как производственный процесс продолжает улучшаться, которые не будут упомянуты здесь.

Проверка физической компоновки — это завершение всего этапа проектирования чипов, а ниже — производство чипов. Физическое расположение дается в виде файла GDS II литейному заводу, или литейному заводу, который делает фактические схемы на силиконовой вафле, упаковывает их и тестирует, и вы получаете фактический чип, который видите.

Технологическая документация для чипов

В важных звеньев дизайна чипов, таких как синтез и анализ времени, чертеж макета и т.д., необходимы файлы библиотеки процессов. Тем не менее, людям часто не хватает понимания технологических документов, поэтому трудно узнать что-то о чипах дизайна самостоятельно. Например, дизайн учебного макет-это просто бумажный проект без файла библиотеки диаграмм процессов. В этой статье в основном представлены знания, связанные с библиотекой процессов.

Технологическая документация предоставляется производителями чипов, поэтому необходимо иметь общее понимание отечественных и международных производителей чипов. На международном уровне существуют крупные производители полупроводников, такие как TSMC, Intel и Samsung. В китае, в основном SMIC, China Resources Shanghai, Shenzhen учредитель и другие компании. Эти компании предоставляют соответствующие документы библиотеки процессов, но предпосылка заключается в сотрудничестве с этими компаниями, чтобы получить, эти документы процессов являются конфиденциальными документами.

Полный файл библиотеки процессов состоит в основном из:

1. Библиотека процессов моделирования, главным образом, поддерживает использование двух программных спектров hSPICE, suffix SCS -- spectre, lib -- hSPICE.

2. Аналоговая версия файла библиотеки карт, в основном для программы рисования карты cadence, суффикс tf, DRF.

3. Всеобъемлющая библиотека в цифровой форме, включающая главным образом библиотеку временных рядов, основные компоненты netlist и другие соответствующие всеобъемлющие и хронологические анализы, требует наличия библиотечных файлов. В основном используется для синтеза программного обеспечения постоянного тока и PT анализа времени программного обеспечения.

4. Цифровая библиотека карт, в основном для программного обеспечения cadence Encounter для автоматического макета и маршрутизации, конечно, инструменты автоматического макета и маршрутизации будут также использовать библиотеку времени, интегрированные файлы ограничений и так далее.

5. Карта верификационная библиотека, в основном ДРК,LVS проверить. Некоторые специализированные калибр поддержки, а также некоторые специализированные инструменты поддержки Dracula, Diva и другие инструменты проверки карт. Каждый файл библиотеки имеет соответствующий документ с описанием в формате PDF.

Обратный дизайн будет использовать библиотеки процессов файлов 1,2,5, 3 и 4 не будет использоваться. Форвардный дизайн (форвардный дизайн, который начинается с кода) требует всех файлов. Документация по надлежащей процедуре занимает очень важное место в чип-дизайне, используется ключевой дизайн на каждой ссылке, плюс ее конфиденциальные свойства, поэтому трудно найти полные документы процесса в сети для индивидуального обучения, имеют cadence EETOP открытый для личного обучения библиотечные файлы могут быть удобны для всех, чтобы узнать, но и, кажется, является неполным. проектирование печатных плат