Высокопроизводительные и надежные интегральные схемы

Направления развития рынка электронных компонентов (для компонентов печатных плат PCBA)

Для зрелых технологий LSI с более высокой степенью интеграции и скоростью необходимо разработать технологии изоляции с использованием материалов с низким содержанием K. Но чтобы удовлетворить высокую производительность этих блоков, изоляционные слои становятся все тоньше и тоньше из - за пористой и многослойной структуры. В результате ЛСИ становится уязвимым. С другой стороны, ток LSI постоянно увеличивается, чтобы соответствовать требованиям высокой скорости. В дополнение к размерам чипа от большого до малого, плотность тепла и энергопотребление также растут. Таким образом, для будущей полупроводниковой инкапсуляционной подложки (инкапсуляция ИС - фундамента) необходимо решить эти проблемы, а именно хрупкость, высокая температура, высокая скорость и низкая стоимость межслойной среды. Будущая предустановка полупроводникового процесса будет на уровне 20 нм и ниже, что будет намного слабее.

Технология упаковки для поколения 20 нм

Для следующего поколения 20 нм требуются следующие спецификации:

Низкое напряжение в K - слое

Высокое тепловое излучение для высокопроизводительных LSI 5W

Высокоскоростная скорость 10 ГГц, высокая функциональность

Направления развития упаковки полупроводников

Чтобы адаптироваться к функциональному росту и снижению затрат на электрооборудование, включая мобильные устройства, правила предустановки кристаллического круга переходят к более крупным и сложным правилам предустановки. С этой целью, чтобы снизить затраты, технология упаковки полупроводников быстро переходит от стандартной технологии соединения золотой проволоки к соединению медной проволокой, что уменьшает использование золота. Кроме того, использование технологии инвертирования чипов в значительной степени соответствует более высокой интеграции и производительности LSI. В 2010 году инвертированные чиповые соединения составляли 15% глобальной технологии упаковки полупроводников, а проводные соединения - 85%. Ожидается, что к 2015 году доля инвертированных чипов достигнет 25%, а доля проводных соединений достигнет 75%. В частности, для высокоинтегрированных и высокопроизводительных LSI, требующих высокой тепловой радиации и высокой скорости сигнала, технология перевёрнутых чипов активно рассматривается как подходящая.

Технология перевёрнутых чипов

Подходит для низких K

Часто используемые технологии обратной загрузки:

Сварка соседних сторон, основная конструкция C4 (совместная конструкция управляемого осадочного чипа)

Для выпуклости Au и прессования типа ACF

УЗИ подписи типа AU - AU

Соединения давления и ультразвуковые связи оказывают высокое давление и механические колебания на LSI, поэтому эти методы не могут быть использованы для LSI с низким уровнем K. Таким образом, в вышеупомянутом методе C4 может быть использован надлежащим образом, и из - за сравнения трех методов сочетание согласуется с тем фактом, что C4 наносит минимальный ущерб чипу.

Технология C4 была разработана в начале 40 - х годов для использования в компьютерах общего назначения и используется до сих пор. С увеличением количества низкоK - чипов C4 используется для низкоK, заменяя структуры, материалы и улучшения UBM.

Недавно разработанные Cu - цилиндрические выпуклые блоки (примерно аналогичные прогрессу C4) подходят для прямолинейных или перекрывающихся сварных дисков, а не для низкоK - чипов. Сообщается, что из - за высокого модуля упругости Cu (130GPA) упаковка колонны Cu может повредить нижний K - слой. Рассогласование коэффициента теплового расширения (CTE) является фактором ускорения.

Кроме того, считается, что технология C4 изначально использовала высокоэластичный модуль расплавленного металлического узла и флюса (50GPA) после флюса, поэтому количество напряжений добавляется к LSI во время связывания и установки материнских плат из - за различий в нагревательном расширении. Таким образом, технология C4 не может быть использована для будущих LSI, которые намного слабее.

Тепловое излучение

До сих пор органическая подложка использовалась для инкапсуляции чипов. Органическая подложка имеет небольшую теплопроводность 0,5 Вт / МК и ее трудно применять к LSI с высоким энергопотреблением. Если добавить системы охлаждения или охлаждения для улучшения теплового излучения, стоимость упаковки, размер и высота плоскости или поверхности возрастут.

На самом деле, из - за низкого теплового излучения, LSI немного ограничивает его потенциал, чтобы не производить много тепла. Кроме того, из - за плохого теплового излучения температура перехода повышается, ток утечки увеличивается, что еще больше увеличивает энергопотребление, а увеличение энергопотребления приводит к повышению температуры. Это опасный порочный круг. Поэтому улучшение теплового излучения является тесно связанной с этим проблемой.

Скорость сигнала.

Потери диэлектрического повреждения в центральном слое органической подложки высоки (0,02), а сопротивление сквозного отверстия в центральном слое (T / H) высокое. В результате потери от повреждения вставки в высокочастотном диапазоне высоки. Тем не менее, использование безъядерной матрицы из того же материала, что и традиционная органическая матрица, не является фундаментальным решением. Кроме того, композитные материалы могут быть разнообразными, поэтому пользователям сложнее выбрать лучший материал, и все требования по умолчанию должны учитывать высокоскоростную производительность.

Поскольку фундамент тонкий, необходимо заменить ряд объектов. Это стало препятствием для производства. Из - за этой проблемы переход на безжильную подложку сопряжен с высоким риском и подходит только для локализованных продуктов.

Традиционные технологии вряд ли смогут удовлетворить потребности будущего поколения 20 нм. Поэтому необходимо разработать новые полупроводниковые упаковки с новыми основными технологиями.

Типы и методы Monsterpac

Monsterpac typec был разработан для 20 - нм процесса, который трудно адаптировать к традиционным технологиям упаковки. Это полностью отличается от традиционного процесса упаковки и конструкции.

Конструкция упаковки

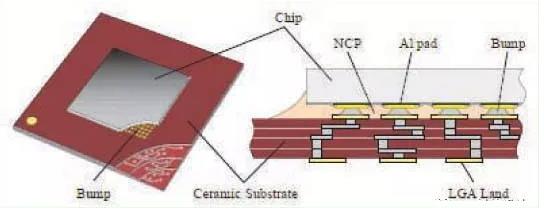

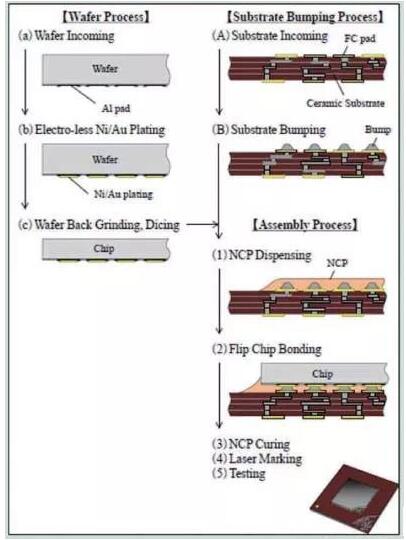

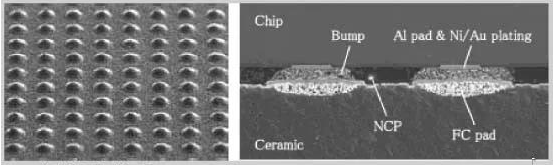

Наша конструкция упаковки, подложка керамическая, полупроводниковые чипы с выпуклыми блоками в обратном виде, чипы и подложка для дополнения NCP (непроводящая паста). Он не изготовлен из эпоксидного газа или натуральной смолы. Так что задняя часть чипа открыта. Обратная сварка имеет меньший высокотемпературный деформационный изгиб, менее 30 - 50 мкм, поэтому инкапсулируется как LGA (инкапсуляция контактной решетки) без сварного шара, а не BGA (инкапсуляция сеточной решетки). Серебряная электропроводящая паста используется в выпуклых точках, которые печатаются на основной пластине, поэтому модули больше не изготавливаются на сварных дисках. Только на Al - сварочном диске чипа не покрыты никелем и золотом, процесс без выпуклой точки кристалла (рис. 1 - 3).

FIC - 1 Упаковочная конструкция

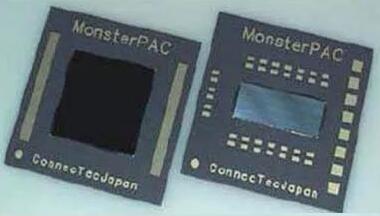

Фотографии упаковки FIC - 2

Процесс FIC - 3

Примерно так же, как описано выше, наша упаковка состоит только из 4 материалов (чипы, выпуклые блоки, керамика и NCP). Эта простая структура делает упаковку небольшой, тонкой и легкой.

На выбор доступны два основных типа керамических базовых материалов: HTCC (высокотемпературная керамика с общим горением) и LTCC (низкотемпературная керамика с общим горением). Особые свойства керамики (например, электрические свойства, теплопроводность, CTE и деформация) и соединение с перевернутыми чипами делают наши упаковки лучшими решениями для удовлетворения различных требований от электрических продуктов до полупроводниковых чипов.

Уникальная структура Monsterpac

Эти уникальные места описаны ниже:

• Соединение без повреждений

Высокое тепловое излучение

Низкие потери при вставке

· Высокая надежность

Сочетая эти основные преимущества, MonsterPac TypeC успешно обеспечивает максимальную производительность для 20 - нм LSI.

Соединение без повреждений

Основной технологией нашего инкапсуляции является технология безотказного перевёрнутого чипа, которая успешно обеспечивает безотказное и высоконадежное соединение полупроводниковых чипов, изготовленных с использованием передовых прецизионных процессов.

Неповрежденные полупроводниковые чипы означают:

склеивание при низком давлении

Мы можем достичь давления сцепления 0,12 г / bump, что составляет 1 / 20 нормального давления C4 2,4 г / bump. Уменьшая нагрузку на соединение до этого предела, можно избежать повреждения межслойной среды, вызванного соединением.

Низкое напряжение рефракции при выпуклом отверждении

Сжаточное напряжение в процессе затвердевания выпуклой точки меньше 10 МПА / выпуклой точки, очень мало. Высокопроизводительная и надежная обратная сварка была успешно достигнута за счет снижения верхнего предела температуры, нагрузки и напряжения отжима, наложенного на средний слой хрупкой среды (например, сварочные диски с низким K и Al и линии и т. Д.), избегая разрыва линии и трещин.

Из этих преимуществ видно, что это единственная упаковка, которая имеет структуру, которая избегает повреждения слабого низкого K - слоя.

Высокое тепловое излучение

Понимая, что тепло полупроводниковых чипов излучается упаковочной подложкой, мы выбрали керамическую подложку вместо обычной органической подложки (теплопроводность 0,5 Вт / мк), потому что ее теплопроводность на 14 Вт / мкм выше, чем у органической подложки. Когда размер упаковки 21 * 21 мм, при использовании керамической подложки расход энергии достигает 6 Вт, Это в 1,7 раза больше мощности органической подложки с потреблением 3,6 Вт.

Низкая вставка может навредить вам.

Электронное оборудование требует высокого уровня производительности в высокочастотном диапазоне. Потеря при вставке керамической подложки составляет 0,42 дБ (@ 20 ГГц, L = 5 мм), а при вставке органической подложки - 0,62 дБ. Допустимая частота керамической пластины составляет более 10 ГГц, а частота органической пластины - 3 ГГц.

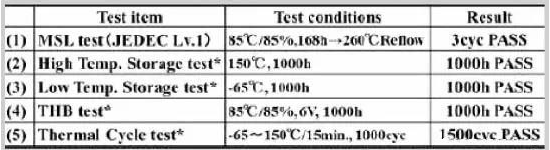

Высокая надежность и влагонепроницаемость

Нормальное сопротивление обратного тока (MSL: уровень увлажнения) имеет уровень 3 (@ 30DEG / 60 100% RH192Hr). У Monsterpac typec есть неповрежденный полупроводниковый чип, выпуклый блок, изготовленный из неплавленного материала. При высокотемпературном возврате выпуклые блоки не расплавляются, поэтому повторное переплавка и повторное отверждение не повторяются, а керамическая подложка не поглощает влагу. Таким образом, MonsterPac TypeC имеет класс MSL 1 (@ 85DEG / 85 100% RH192Hr) и удаляет влажную и влагонепроницаемую упаковку без предварительной выпечки, а срок службы растений MonsterPac Type C неограничен.

Высокие темпы роста растений

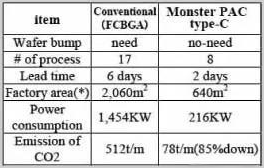

Для удобства производства мы разработали конструкцию эпоксидных газовых выступов, а не сварных выступов. Таким образом, требуется большое количество установок для обработки выпуклых блоков кристалла, а также стоимость большого количества сварки can +, прилегающей к обратному потоку. Таким образом, размер плоскости или поверхности устройства может быть уменьшен на 69% по сравнению с традиционным технологическим устройством C4 того же размера, а энергопотребление устройства может быть уменьшено на 85%. Успешно могут быть реализованы энергосберегающие и низкофоновые электростанции.

Вместимость

Уникальность технологии Monsterpac Typec

Керамическая выпуклость

Monsterpac typec считает целесообразным использовать крем, содержащий серебро, в качестве выпуклого материала. Используя обычную сварочную печать SMD - деталей для печати, на керамической основе образуется выпуклость (в зависимости от обстоятельств). Не требуется предварительная обработка и очистка поверхности керамической подложки перед высокой обработкой или гальваническое покрытие поверхности после образования высоты. Традиционные органические FCBGA требуют длинных выпуклых точек на Al - сварочном диске полупроводниковых чипов, таких как флюс, Au и Cu. Однако выпуклые блоки на основе керамики не требуют этого процесса длинных выпуклых пластин. Вместо этого они производят негальванизированные Ni и Au на полупроводниковых чипах. Выдающиеся блоки, основанные на керамической технологии, успешно реализуют простой и недорогой процесс обработки.

Кроме того, в отличие от жестких выпуклых точек (твердость 10 ГВ), используемых в технологиях здравого смысла, таких как флюс, выпуклость Au и Cu, мягкие выпуклые точки (1 ГВ) были разработаны для сохранения рисунка при низкой твердости.

Для мягкой выпуклой проводящей пасты, содержащей серебро, мы разработали соответствующие фиксированные точки, которые имеют большой опыт в низком напряжении, низком сопротивлении подписи и детализированной асфальтовой печати. До сих пор мы сформировали выпуклые блоки рабочей силы, которые являются поверхностными матричными сварочными дисками: интервал 150 э.; Периферийный сварочный диск: интервал 75 островов. Однако фактические правила предустановки учитывают расстояние между сварными дисками, поэтому расстояние между поверхностными решетками 60° m применимо только к открытым выпуклым блокам.

Соединение без повреждений

Используя технологию мягкого перевёрнутого чипа, NCP используется для распределения мягкого выпуклого блока, образованного технологией керамических выпуклостей, а затем соединяет полупроводниковый чип с перевёрнутым чипом. Во время соединения выпуклая паста и NCP отверждаются одновременно. В результате была успешно достигнута совместная подпись и надежность.

Температура на объекте FCB ниже 200 градусов по Цельсию, что на 40 градусов ниже, чем при обычной технологии склеивания. Давление сцепления составляет менее 0,12 г / дот, что составляет 1 / 20 от обычной технологии сцепления. Благодаря этим низкотемпературным и низковольтным термокомпрессионным соединениям полупроводниковые чипы не подвержены стрессам и внешним силам в процессе отверждения после соединения и соединения. NCP включает добавки, которые обычно обнаруживаются на обеих сторонах чип - диска и выпуклого блока. Тем не менее, часто бывает переворачивать клавиши чипа при низком давлении. Дополнение зарыто в выпуклый блок, поэтому оно не влияет на подпись между диском чипа и выпуклым блоком. Это одно из преимуществ мягкой тряски. После распределения NCP перед обратной сваркой NCP легко пополняется между выпуклой точкой и узким зазором, и при использовании клавиш с низкой нагрузкой не происходит выравнивания между чипом и фундаментом. Поэтому эта технология соединения подходит для узкого расстояния между сварными дисками.

Общая проблема с технологией сцепления заключается в том, что в случае перевёрнутого чипа с сварным выпуклым блоком выпуклость полупроводникового чипа и Al - сварочный диск подвергаются очень большому напряжению отжима (около 200 - 500 мПа / выпуклый блок) во время плавления флюса до отверждения. Технология соединения при низком напряжении была успешной, так как для низкоэластичного модуля неплавленного выпуклого материала требовалось очень небольшое напряжение отдачи (менее 10 МПа / выпуклая форма).

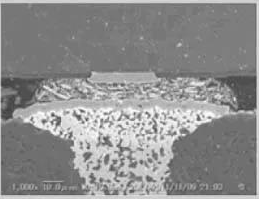

Именно благодаря развитию этих базовых технологий успех обратной сварки не пострадал. На рисунке 4 показаны ключевые точки перевернутого чипа и профиль подписи.

Рисунок - 4 Внешний вид и профиль

Надежность упаковки

ТК проверил контуры задней выпуклой точки, но не проверил и не измерил трещины и удаление накипи, которые могут быть вызваны разрывной связью.

APIC (Прикладное оборудование IC)

Сегодняшняя обработка APIC движется в направлении точной обработки с использованием материалов с низким содержанием K, что требует высоких температурных допусков и высоких скоростей. Monsterpac TypeC имеет следующие преимущества для удовлетворения этих требований.

• Соединение без повреждений

Высокое тепловое излучение

Когда высокая скорость

Некоторые клиенты APIC оценивают масштаб производства MonsterPAC Typec

Тип PAC C

В результате фактической оценки между органическими FCBGA и Monsterpac TypeC при одинаковых условиях (одинаковые юбки, одинаковые чипы и одинаковое расстояние между сварочными дисками) температура Monsterpac Tj на 10 градусов ниже, чем в органическом корпусе. После очень точного сопоставления Tj разница составит около 20°C.

Радиочастотная плата (радиочастотная плата):

В настоящее время для высокоскоростной связи LSI упаковка панелей постоянно совершенствуется. Эти компоненты требуют следующих особых характеристик:

Подходит для высокоскоростных и высокочастотных

Малый размер

Для высокоскоростных и высокочастотных приложений, как описано выше, использование керамической подложки может увеличить потери при вставке и может быть использовано для 10 ГГц.

Кроме того, несколько чипов и большое количество компонентов SMD могут использоваться в небольших упаковках, так как они могут быть соединены с помощью перевернутых чипов с небольшим расстоянием между деталями.

В сотрудничестве с заказчиками разрабатываются образцы радиочастотных панелей, производительность которых признана заказчиком и готовится к крупномасштабному производству

Радиочастотный модуль

Для оболочек этих пластин влажность фундамента очень плотная. MSL Monsterpac Typec имеет уровень 1, поэтому не существует влажной асфиксии.

Можно видеть, что MonsterPAC TypeC лучше всего подходит для плоской упаковки, а традиционные органические SMD и перевернутые чипы требуют многократной обратной сварки.

Судьи

Для следующего поколения 20 - нм процессов требуется упаковка, чтобы соответствовать более высокому тепловому излучению и более высокой скорости. Тем не менее, здравый смысл технологии упаковки трудно удовлетворить этим требованиям. Поэтому необходимо разработать новую технологию упаковки для 20 - нм процесса.

Наш Monsterpac TypeC подходит для предстоящего 20 - нм процесса и максимизирует производительность LSI. Его высокая производительность похожа на удивительный странный продукт. Разработанный нами MonsterPAC сделал C4 устаревшим и стал основной технологией для следующего поколения полупроводников.

Разработка технологий для следующего поколения

Исследования и разработки новых керамических фундаментов

Развитие технологии керамического фундамента всегда было ярким. До сих пор точное и детальное картирование высокой плотности значительно отставало от органической подложки IC.

Чтобы решить эту проблему и добиться прогресса, мы приступили к разработке прецизионной керамической подложки с высокой плотностью без ущерба для стоимости. Наша цель - расстояние между линиями 20 ° м для достижения надлежащей точности и использования более гибких детальных графиков. По умолчанию расстояние между отверстиями также должно быть более точным и подробным, цель 50 ° м.

На сегодняшний день керамическая основа изготовлена с использованием штамповки и печати шаблонов (в зависимости от обстоятельств). Существующие технологии ограничиваются точным и подробным картированием. Мы рассматриваем возможность замены их лазерами и процессами прямой печати. Внедрение этой технологии обеспечит лучшую производительность, чем органическая подложка. До сих пор керамические фундаменты обычно использовались в высококачественных продуктах, но этот новый фундамент будет предназначен для потребительских товаров. Базисы действительно нуждаются в высокопроизводительных потребительских товарах для собственного роста.

Сочетание этой базовой платы с технологией MonsterPAC обеспечит миру оптимальную производительность и высокую надежность печатных плат (PCB).