на печатных плат,анализ шумов для одновременных переключателей ПЛИС, сегодня технология КМОП позволяет одному устройству ПЛИС иметь несколько единиц ввод/вывод - интерфейс. одновременно, В последние годы, низкое энергопотребление стало основной концепцией/О - интерфейс. эффективный способ снижения энергопотребления - снизить напряжение, снижение напряжения приведет к допустимому I минимуму шумов/О - интерфейс. поэтому, это обязательно для ПЛИСпользователи для количественной оценки системы-количество синхронный шум переключения (SSN) в контексте чипов, упаковка, полихлорированные дифенилы. Эта статья систематически описывает, Внимание: буфер вывода ПЛИС вызван. Этот шум обычно называют выходным шумом синхронного переключения (система единого входа) и отличается от из-за буферизации ввода. была представлена информация о причинах, связанных с одноточечным входом в систему, и была предложена иерархическая система с одноточечным входом в систему. В нем также разъясняется, каким образом одноточечная модель входа в систему соотносится с частотными и временными измерениями, и представил несколько печатных плат Уменьшить размер система единого входа.

Механизм формирования система единого входасистемного уровня

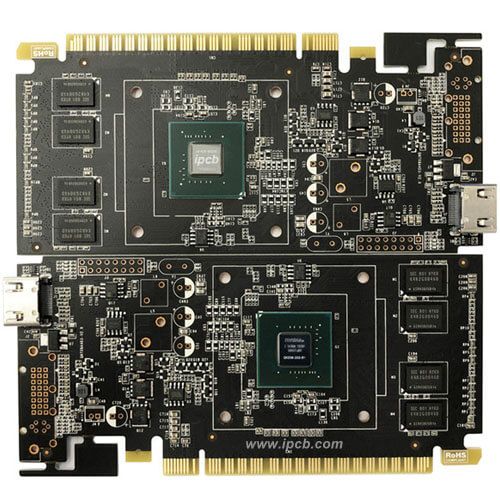

A печатных плат ПЛИС представляет собой сложную систему, состоящую из полупроводниковых частей с активной схемой, герметизированная графитовая носовая летательного аппарата встроенного пассивного прибора с поддержкой сопровождения, а также часть платы, обеспечивающая связь с внешним миром . в таких системах, трудно понять шумовые свойства внутри чипа. поэтому, квантованный одноточечный вход в систему печатных плат, подключенный к ПЛИС. There are two main factors that cause система единого входа: полное сопротивление сети распределения электроэнергии (ПДн)и взаимной индуктивной связи между переключателем I/операционная система. с системной точки зрения, ПДн содержит уровень вафли, класс упаковки, блок панелей с общим питанием для схемы КМОП. При включении нескольких драйверов вывода КМОП, большой ток мгновенно вливает в индуктивный элемент ПДн, приводить к понижению напряжения дельта - паразитная индуктивность, например, шаровой сетчатый массив в корпусе печатных плат. Этот быстро изменяющийся ток также возбуждает радиальные электромагнитные волны между энергиями/стратиграфическая пара, отскакивание от края плоскости печатных плат, звучать между властью/плоскость Земли, вызывать колебание напряжения.

Другой важной причиной система единого входа является взаимная индукционная связь, особенно на краю кристалла/печатных плат. Полупроводниковые чипы БГА герметизированные на олово и на печатных плат. каждый/сварочный шар и его соответствие печатных плат проходное отверстие образует замкнутое кольцо с заземленным шаром и прилегающим к нему заземляющим отверстием.. при нескольких режимах/О - порт одновременно изменён, переходный ввод/вывод ток протекает через эти сигнальные цепи. этот переходный процесс я/ток О, в свою очередь, вызывает магнитное поле, которое изменяется при входе в соседнюю цепь сигналов и индуцированном шуме напряжения.

одноточечная модель входа в систему должна отражать механизм формирования входа в систему. Рисунок 1 показывает иерархическую модель для прогнозирования система единого входа в печатных плат. в вафли, Необходима модель буфера вывода, которая обеспечивает распределение тока по силовым и сигнальным линиям с ограниченной сложностью. в упаковке, Для простоты, использовать инструменты моделирования для получения модели ПДн и модели связи сигналов соответственно, Однако следует тщательно рассмотреть взаимодействие между ПДн и моделями связи сигналов. Эти две модели служат мостом, буферная модель вывода, соединяющая кристалл с закреплённым выступом печатных плат- горизонтальная модель на стороне паяного шара. модель ПДн печатных плат обычно включает питание/плоскость и объём земли/развязывающий конденсатор на нем, модель связи сигнала печатных плат включает в себя тесно связанные между собой переспористые решетки и траектории сигнала свободной связи на различных слоях сигналов . взаимодействие между ними печатных плат- модель уровня происходит печатных плат сквозная матрица, именно отсюда индуктивное последовательное внедрение шумов в модель ПДн, шум delta - I в свою очередь снижает/О - сигнальная масса. Этот метод послойного моделирования разумно сохраняет точность моделирования, а также повышает расчетную эффективность таких сложных систем.

В нижеследующих разделах, относительно печатная плата оснащать, Представление двух базовых методов проектирования, основанных на одноточечных механизмах генерации входа в систему.

1. Метод проектирования для уменьшения индуктивной связи

Результаты моделирования показывают, что индуктивная связь на корпусе микросхемы/интерфейс печатных плат - это главный виновник. размер t‧ d сигнал обратного пути маршрутизатор отверстие и рядом с ним заземленное отверстие. размер контура указывает на интенсивность индукционной связи. Чем больше площадь I/контур с нулевыми помехами, создаваемое магнитное поле более легко проникать в соседние возмущенные контуры. Чем больше возмущенная область I/контур сигналов о, чем легче быть другим/О - контур. поэтому, для уменьшения последовательности и параметров t, Следует обратить внимание на использование разбавителя печатных плат в проекте, ключ ко мне/верхняя операционная система печатных плат извлечение из более мелкого слоя сигнала. одновременно, Проектировщики могут уменьшить помехи, сократив расстояние между i/О - проходное отверстие и заземление. дизайнер специально связался с парой I/О установка паяльного диска на стыковой пласт и плоскость, чтобы уменьшить площадь сигнального шлейфа, соответствующего турбулентным выводам и турбулентным выводам. в банке 1, поводок AF30 помех. в проекте ПЛИС, шесть иголок W24, W29, AC25, AC32, AE31 и AH31 запрограммированы как логическое "0", Они связаны печатных плат проходное отверстие. пять иголок U28, AA24, A26, программирование AE28 и AE30 как логическое "1" и соединение с ними печатных плат. Другие 68 I/порт о при 10MHz, Поэтому они являются поводом для вмешательства. Для сравнения, I/Os W24, W29, AC25, AC32, AE31, AH31, U28, AA24, A26, в блоке цилиндров 2, AE28 и AE30 не запрограммированы как ссылки на землю или, Но они пусты, Другие 68 я/о все еще открыт и закрыт одновременно. экспериментальные испытания показали, что по сравнению с блоком 2 гб30 в блоке 1 по сравнению с блоком 1 по AF30 отскок на земле сократился на 17%, временное падение мощности также снизилось на 13%. Эмуляция также подтвердила это улучшение. расстояние между контуром интерференции и контуром интерференции d, Ожидаемое сокращение система единого входа, Как показано на диаграмме 2. Однако, Не удалось уменьшить площадь сигнального кольца в корпусе кристалла, что ограничило его улучшение.

2. Уменьшите импеданс ПДн за счет разумных проектировать

Импеданс между контактами заземления и контактами на интерфейсе печатной платы является важным критерием для оценки производительности ПЛИС устройства ПЛИС чип. Это входное сопротивление может быть снижено с помощью эффективной стратегии развязки и использования более тонкой мощности/стратиграфическая пара. Однако, эффективный способ сокращения длины перерывов в электроснабжении, соединяющих шары с плоскостью. и, укороченная мощность через отверстие также уменьшает кольцевую цепь, защита контура от помех I/изменение состояния контура о. поэтому, план должен быть расположен ближе к верхнему слою печатных плат.

в данной статье представлен полный анализ моделирования шумов одновременных переключателей печатных плат использование ПЛИС. анализ показал, что последовательные помехи в интерфейсе между печатных плат, а также распределение импедансов чип на упаковке и печатных плат являются двумя важными причинами система единого входа. корреляционная модель печатных плат Дизайнеры сокращают система единого входа и добиваются улучшения печатных плат дизайн. в тексте также представлены несколько способов сокращения система единого входа. среди, разумно настраиваемый сигнальный слой, полное использование программируемого заземления/вывод питания помогает уменьшить индукцию печатных плат уровень, & Настроить печатных плат наложение также может снизить импеданс чип.