Еще одним частным случаем общей системы синхронизации является внутренняя система синхронизации. Многие неопытные инженеры ошибочно принимают внутреннюю систему синхронизации за синхросигнал источника и выполняют управление равной длиной в соответствии с синхросигналом источника, что приводит к ошибкам при проектировании синхронизации.

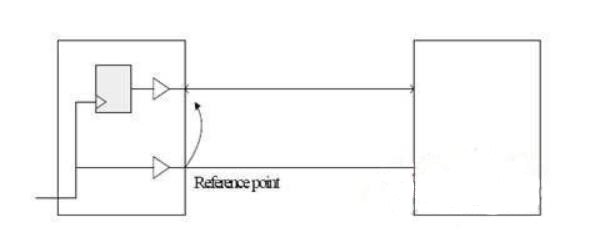

Прежде всего, рассмотрим, как определить, является ли система общей синхронизацией. В предыдущей статье блога упоминалось, что поиск дерева синхронизации и определение взаимосвязи между тактовыми сигналами является ключом к оценке различных систем синхронизации. Система общей синхронизации обычно имеет внешний кристалл или кристалл, который подключается к ведущему и приемному концам системы через распределитель тактовых сигналов (или ПЛИС может напрямую выдавать различные тактовые сигналы на ведущий и приемный конец), и внешнюю тактовую линию Для управления синхронизацией системы она называется системой общей синхронизации.

Тактовый сигнал внутреннего синхронизатора передается непосредственно с ведущего конца на приемный. В предыдущей статье блога упоминалось, что временной запас системы общего тактового генератора невелик, и одним из ключевых факторов, из-за которого нельзя продолжать увеличивать частоту, является Tco. Из-за таких факторов, как технологический процесс, трудно сделать этот Tco слишком маленьким. Например, Tco max для SDRAM является общим. Он составляет 5,4 нс. Внутренняя система синхронизации заменяет внешний драйвер тактового генератора внутренним буфером, благодаря чему буфер на тактовом сигнале и буфер на сигнале данных могут быть согласованы и отменять друг друга, что позволяет уменьшить диапазон между максимальным и минимальным значениями Tco устройства и увеличить Timing margin, что облегчает соблюдение тайминга.

Внутреннюю систему синхронизации легко спутать с синхронизацией по источнику. На самом деле их легко отличить, поняв принцип. Временная синхронизация источника, как правило, существует в системном тактовом генераторе и стробирующем сигнале группы данных, например, связь между DQ и DQS и CLK. Внутренний синхросигнал имеет только один тактовый сигнал, общий для передающей и принимающей стороны (в Mobile SDRAM этот сигнал называется SDCK).

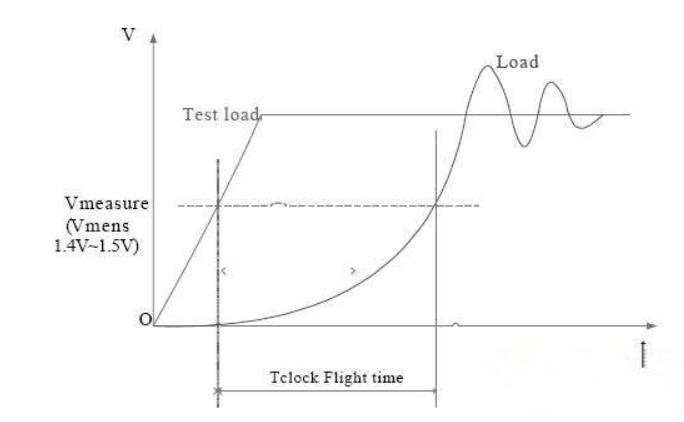

Поэтому расчет тайминга внутренней синхронизации аналогичен расчету общего тактового генератора, за исключением того, что в неравенстве присутствует еще одна переменная - TCLK_FT: время пролета часов. На рис. 2 показан метод измерения TCLK_FT.

Формула расчета временных характеристик внутренних часов синхронизации выглядит следующим образом: (если направление распространения часов и данных совпадает, то это положительное направление)

Tco(max)+Tflight(max)+Tsetup-Tclk_ft+Tjitter+Tmargin

Tco(min)+Tflight(min)-Tclk_ft-Tmargin>Thold

Таким образом, регулируя Tclk_ft, можно добиться оптимального положения часов. Этот метод также может быть использован для настройки синхронизации в режиме внешней синхронизации. Конкретный метод настройки был представлен в предыдущем примере, вы можете обратиться к нему.

Резюме:

С внешней точки зрения внутренняя синхронизация и синхронизация по источнику одинаковы, но внутренняя структура этих двух методов различна. Метод синхронизации источника заключается в добавлении регистра перед буфером тактового сигнала в структуре внутренней синхронизации, а обработка тактового сигнала и обработка данных внутри микросхемы совпадают. Таким образом, тактовый сигнал может изменяться со скоростью данных и всегда находится в середине данных.

Суть внутренних часов синхронизации по-прежнему заключается в общей системе синхронизации. Расчет синхронизации производится так же, как и в случае с системой общих внешних часов, за исключением того, что Tclk_ft прибавляется или вычитается на обоих концах результата расчета. Взаимосвязь временных ограничений также осуществляется по принципу максимальной и минимальной общей длины, а не по принципу равной длины.

Внутренний синхросигнал увеличивает возможности регулировки временного запаса, а поскольку он нивелирует влияние Tco, то временные ограничения легче соблюсти. Однако метод расчета тайминга более сложен и требует понимания от инженера-проектировщика. печатных плат