De acuerdo con las últimas tendencias de diseño de pcb, mejorar la eficiencia se ha convertido en un objetivo clave, y el uso de dispositivos de conmutación lenta para obtener un mejor EMI no vale la pena. En aplicaciones difíciles de manejar con MOSFET plano, el supernudo puede mejorar la eficiencia. En comparación con la tecnología tradicional de MOSFET plano, el MOSFET de superunión puede reducir significativamente la resistencia de conducción y la capacidad parasitaria. Aunque la reducción significativa de la resistencia de conducción y la reducción de los condensadores parasitarios ayudan a mejorar la eficiencia, también genera un cambio rápido de voltaje (dv / dt) y corriente (di / dt), lo que resulta en ruido de alta frecuencia y radiación emi.

Para impulsar el MOSFET de superunión de interruptor rápido, es necesario comprender el impacto del parásito de encapsulamiento y diseño de PCB en el rendimiento del interruptor, así como los ajustes de diseño de PCB para el uso de superunión. Se utiliza principalmente un MOSFET de superunión con un voltaje de ruptura de 500 - 600v. Entre estas calificaciones, los estándares de la industria to - 220, to - 247, to - 3p y to - 263 son los encapsulamientos más utilizados. El impacto del encapsulamiento en el rendimiento es limitado, ya que la longitud de la puerta interna y el cable de Unión de la fuente es fija. Solo se puede cambiar la longitud del cable para reducir la inducción de la fuente encapsulada.

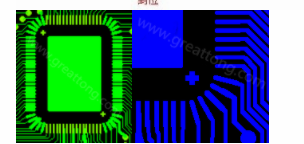

¡Los inductores de alambre típicos de 10nh no parecen grandes, ¡ pero el di / DT de estos MOSFET puede llegar fácilmente a 500a / isla 188s! Suponiendo que di / DT sea 500a / isla 188s, el voltaje en el inductor de alambre de 10nh es vind = 5v; El apagado di / DT del inductor de alambre de 10nh es de 1000a / s, lo que puede producir un voltaje vind = 10v. La mayoría de las aplicaciones y diseños no tienen en cuenta que esta inducción adicional también genera voltaje, pero esto no puede ser ignorado. Los cálculos simples anteriores muestran que los inductores de fuente total encapsulados, es decir, los inductores de unión y pin, deben reducirse a valores aceptables. Otra fuente de ruido es el efecto parasitario del diseño. Hay dos diseños visibles de parásitos: inductores parasitarios y condensadores parasitarios. La inducción de la trayectoria de 1 cm es de 6 - 10nh. Este inductor se puede reducir añadiendo una capa en la parte superior del PCB y una capa gnd en la parte inferior del pcb. Otro tipo son los condensadores parasitarios.

El principio del parásito capacitivo en el diseño. Los condensadores parasitarios son causados entre dos trazas adyacentes o trazas y el plano de tierra del otro lado. Otro tipo de capacitor es el capacitor entre el dispositivo y el plano de tierra. Dos líneas paralelas a ambos lados de la placa de PCB pueden aumentar la capacidad y reducir la inducción del circuito, reduciendo así la radiación de ruido electromagnético. La próxima vez que su diseño necesite un MOSFET súper nudo, considere estas habilidades de diseño.

Componentes parasitarios en encapsulamiento y diseño

Debido a que MOSFET es un dispositivo unipolar, los condensadores parasitarios son el único factor limitante para el Estado transitorio del interruptor. El principio de equilibrio de carga reduce la resistencia de conducción en áreas específicas y el tamaño del chip bajo el mismo RDS (conducción) es menor que la tecnología MOSFET estándar. La figura 1 muestra los condensadores de los MOSFET de superunión y los MOSFET planos estándar. El coss del MOSFET estándar tiene una relación lineal moderada, mientras que la curva coss del MOSFET supernodal muestra una relación altamente no lineal. Debido a la mayor densidad de unidades, el valor inicial del coss del MOSFET de superunión es mayor, pero en el MOSFET de superunión, el coss disminuirá rápidamente cerca del voltaje de fuga - fuente de unos 50v. Estos efectos no lineales pueden causar oscilaciones de voltaje y corriente cuando se utilizan MOSFET de superunión en convertidores PFC o DC / DC. La figura 3 muestra un esquema simplificado del circuito pfc, que incluye elementos parasitarios internos del MOSFET de potencia y circuitos osciladores externos. Los circuitos osciladores externos incluyen condensadores de acoplamiento externo (cgd ext.) traídos por el diseño.

Comparación de los condensadores de salida de MOSFET plano y MOSFET de superunión

En general, hay varios circuitos osciladores que afectan las características del interruptor del mosfet, incluidos los circuitos osciladores internos y externos. En los circuitos pfc, l, Co y dboost son inductores, condensadores de salida y diodos boost, respectivamente. Cgs, CGD Int y CDS son condensadores parasitarios de MOSFET de potencia. Ld1, ls1 y lg1 son los drenajes, las líneas de Unión de la fuente y la puerta y los inductores de pin del MOSFET de potencia. RG Int y RG ext son la resistencia interna de la puerta del MOSFET de potencia y la resistencia externa de conducción de la puerta del circuito. CGD ext es la puerta parasitaria del circuito - condensadores de drenaje. Ld, ls y LG son inductores dispersos de drenajes, fuentes y rastros de puerta de placas de circuito impreso (pcb). Cuando el MOSFET está encendido o apagado, se produce una oscilación parasitaria de la puerta en el circuito de resonancia a través del capacitor de drenaje de puerta CGD y el inductor de alambre de puerta lg1.

En condiciones de resonancia (Íl = 1 / Íc), el voltaje de oscilación generado en las tensiones de puerta y fuente es mucho mayor que el voltaje de conducción. La oscilación de voltaje causada por el cambio de resonancia es proporcional al factor de calidad q (= L / R = 1 / cr). Cuando el MOSFET está apagado, la red de inductores parasitarios de drenaje (ld + ld1), condensadores de drenaje de puerta CGD e inductores de alambre de puerta lg1 causan voltaje oscilante de puerta. Si la resistencia de la puerta (rg - ext + RG int.) es muy pequeña, q se hace más grande. Además, la caída de tensión en ambos extremos de ls y la inducción dispersa de la fuente de ls1 producen oscilaciones en el voltaje de la puerta a la Fuente. Las oscilaciones parasitarias pueden causar rupturas puerta - fuente, EMI malo, grandes pérdidas de conmutación, fallas en el control de la puerta e incluso fallas mosfet.

Es muy importante optimizar el diseño del circuito para maximizar el rendimiento de los MOSFET de superunión sin efectos negativos.