La aparición inicial del paquete a nivel de obleas fue impulsada por la fabricación de componentes de I / o de baja velocidad y Transistor de baja velocidad para teléfonos móviles, como sensores en chip pasivo e IC de transmisión de potencia. En la actualidad, wlap se encuentra en una etapa de desarrollo, impulsada por aplicaciones como bluetooth, GPS y tarjetas de sonido, y la demanda está aumentando gradualmente. A medida que la industria se desarrolla hasta la etapa de producción de teléfonos móviles 3g, se espera que varias nuevas aplicaciones de teléfonos móviles se conviertan en otro motor de crecimiento de wlap, incluidos afinadores de televisión, transmisores de FM y memorias apiladas. A medida que los fabricantes de equipos de almacenamiento implementen gradualmente el wlap, conducirá a una transformación estandarizada de toda la industria.

En la actualidad, la tecnología es ampliamente utilizada en diversos campos, como memoria flash, eeprom, DRAM de alta velocidad, sram, unidades lcd, equipos de radiofrecuencia, equipos lógicos, equipos de gestión de energía / batería y equipos analógicos (reguladores, sensores de temperatura, controladores, amplificadores operativos, amplificadores de potencia). El embalaje a nivel de obleas utiliza principalmente dos tecnologías básicas: la redistribución de películas y la formación de protuberancias. El primero se utiliza para convertir las áreas de unión distribuidas a lo largo de la periferia del CHIP en áreas de Unión de protuberancias distribuidas en forma de matriz plana en la superficie del chip. Este último se utiliza para crear protuberancias en el área de Unión de protuberancias para formar una matriz de protuberancias.

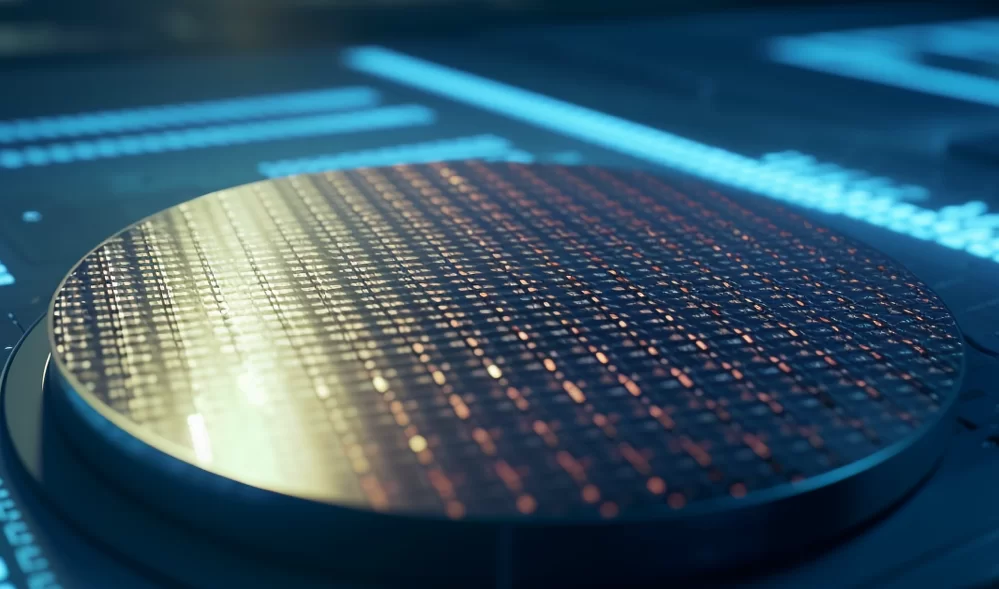

Encapsulamiento a nivel de obleas

En la actualidad, hay tres rutas para el encapsulamiento a nivel de obleas: wlcsp, fowlp y plp:

El wlacsp (encapsulamiento del tamaño del chip a nivel de obleas), también conocido como encapsulamiento en forma de abanico en el wlap, es el método tradicional de encapsulamiento para la División final del chip. Se aplica a circuitos integrados con un menor número de pines. A medida que aumenta el número de señales de salida del ic, el tamaño de la bola de soldadura se vuelve más estricto. El PCB no cumple con los requisitos para ajustar el tamaño del IC encapsulado y la posición del pin de salida de señal.

Fowlp comienza con los chips y luego los redistribuye a nuevas obleas formadas por el hombre. Las ventajas incluyen reducir el espesor del paquete, aumentar la salida del ventilador (más interfaces de E / s), un mejor rendimiento eléctrico y una mejor resistencia al calor. Fiwlp y fowlp tienen diferentes aplicaciones, pero ambos son los principales métodos de embalaje en el futuro. El fiwlp es el más utilizado en chips de señal analógicos y híbridos, seguido de interconexiones inalámbricas, y los sensores de imagen CMOS también están encapsulados con la tecnología fiwlp. Fowlp se utilizará principalmente en chips de procesador en dispositivos móviles.

El PLP (encapsulamiento a nivel de panel) es similar al fowlp, que redistribuye el chip a un panel rectangular más grande que a un chip circular. Un área más grande significa más ahorro de costos y mayor eficiencia de embalaje. Además, cortar el chip en un cuadrado puede causar un encapsulamiento de obleas desperdiciadas, y los paneles rectangulares pueden resolver eficazmente este problema. Sin embargo, esto también plantea mayores requisitos para la litografía y la alineación. La idea básica es completar la fabricación de chips mientras encapsula directamente las pastillas de silicio, encapsulando varias unidades de chips en una estructura de encapsulamiento integral. Esto evita los pasos de encapsular cada chip por separado en un paquete tradicional, lo que aumenta la productividad y reduce los costos.

El proceso de encapsulamiento a nivel de obleas suele incluir los siguientes pasos:

Preparación de obleas: limpieza y preparación de pastillas de silicio para garantizar la fiabilidad y consistencia del proceso de encapsulamiento.

Formación de la estructura de encapsulamiento: recubrimiento de una capa de material de encapsulamiento sobre una pastilla de silicio, generalmente polímero, para formar la base de la estructura de encapsulamiento.

Conexión de circuito: crear un cable metálico (unión de alambre) u otra estructura de conexión de circuito en una pastilla de silicio para conectar el circuito del chip a la estructura de encapsulamiento.

Pruebas y verificación de calidad: realizar pruebas de rendimiento eléctrico, pruebas de integridad de encapsulamiento, etc., para garantizar que el chip de encapsulamiento cumpla con los requisitos de calidad.

Separación de chips: separación de chips encapsulados de pastillas de silicio para obtener chips encapsulados separados.

Basado en la tecnología bga, wlp es una forma mejorada y mejorada de csp, que refleja plenamente las ventajas tecnológicas de bga y csp. Tiene muchas ventajas únicas:

Alta eficiencia de procesamiento de encapsulamiento: fabricación con proceso de producción en masa en forma de obleas.

Hereda las ventajas del encapsulamiento de chips invertidos, es decir, ligeros, delgados, cortos y pequeños.

Bajo costo de las instalaciones de producción: se pueden aprovechar al máximo los equipos de fabricación de chips para evitar la necesidad de invertir en líneas de producción de encapsulamiento separadas.

Consideraciones unificadas de diseño de chips y envases: mejora la eficiencia del diseño y reduce los costos de diseño.

Acorta el ciclo de producción: acorta considerablemente todo el proceso, desde la fabricación de chips, el encapsulamiento hasta la entrega del producto, reduciendo así los costos.

Rentabilidad: el costo de la wlap está estrechamente relacionado con el número de chips en cada obleas. Cuanto más chips hay en el chip, menor es su costo. Este embalaje es el método de embalaje más pequeño y de menor costo.

La ventaja de wlap es que es adecuado para la tecnología de encapsulamiento a nivel de chip (csp) de circuitos integrados más pequeños. Al adoptar la tecnología de encapsulamiento paralelo y pruebas electrónicas a nivel de obleas, wlap reduce significativamente el área del chip al tiempo que aumenta la producción. Además, al conectarse en un chip de conducción paralela a nivel de obleas, el costo de cada I / o se reduce considerablemente. Además, los procedimientos de prueba simplificados a nivel de molde reducen aún más los costos.

El uso de encapsulamiento a nivel de obleas puede realizar encapsulamiento y prueba de chips a nivel de obleas.