A medida que la industria informática avanza hacia convertidores DC - DC capaces de proporcionar hasta 200a a 1v, PCB Board La tecnología de diseño debe satisfacer las necesidades de este nuevo y desafiante convertidor. Comparación de los efectos de los defectos de cableado, Nos preocupa el efecto de la Inductancia parasitaria en el circuito, Especialmente aquellos relacionados con la fuente, Drenaje, Conmutar y puerta de MOSFET. Construimos un PCB Board Convertidor DC - DC para probar la recepción de 12v DC y convertirlo en 1.Salida 3v y hasta 20a. Utilizamos el tablero plug - in para ensamblar y cambiar la Inductancia de cada electrodo MOSFET individual o simultáneamente en cualquier momento. Elegimos utilizar el valor de Inductancia como porcentaje de la Inductancia total de la placa de circuito de 2 pulgadas especialmente diseñada, En lugar de los valores reales, el cableado sólo conoce la longitud de una pista en particular, no necesariamente su Inductancia.

Diseño del ensayo

Utilizamos la eficiencia del convertidor para medir la eficacia de estos inductores parásitos. Esto se debe a que la eficiencia es la medida del rendimiento del convertidor DC - DC. Las pruebas se dividen en las siguientes Partes: ajustar los coeficientes proporcionales de cada Inductancia de drenaje, fuente y puerta de MOSFET, y observar el efecto en el rectificador sincrónico midiendo la eficiencia de conversión. A través de la combinación de cualquiera de los dos, entender la relación entre ellos. La Inductancia de la placa de ensayo de Inductancia es de 43 NH, generalmente 0%, 25%, 50% y 100%. En nuestro experimento, la resistencia parasitaria en el tablero de pruebas de Inductancia tiene poca influencia y puede ser ignorada. Debido a que el efecto perjudicial de la Inductancia parasitaria depende de la frecuencia, realizamos experimentos en tres frecuencias de conmutación predeterminadas: 300 kHz, 600 kHz y 1 MHz. Esto nos permite ver lo importante que será el diseño futuro para pasar de la frecuencia normal de conmutación a una frecuencia más alta. Todos sabemos que la longitud de todas las trazas debe mantenerse corta en el circuito de potencia para evitar el zumbido de tensión y corriente, reducir la interferencia electromagnética global de la placa de circuito y evitar el impacto negativo en los componentes "más estables" en el circuito, especialmente el circuito de control analógico y los componentes relacionados. Además, los materiales de referencia muestran que la Inductancia de la fuente que controla el MOSFET tiene un efecto no lineal en el aumento del tiempo de caída de la corriente de la fuente, lo que resulta en un mayor consumo de energía y una menor eficiencia de conversión. Además de estos fenómenos, la Inductancia de la fuente también puede causar un anillo en el nodo de conmutación.

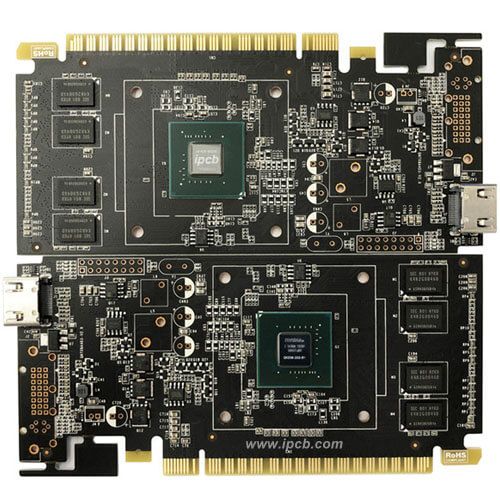

Circuitos y placas de ensayo

El circuito utilizado es una topología de rectificación sincrónica que funciona en un bucle abierto. Esto tiene por objeto eliminar cualquier efecto que el circuito de control pueda tener en el rendimiento del circuito y permitirnos centrarnos en la eficiencia de la conversión de energía, especialmente en el rendimiento de MOSFET. Sabemos que las condiciones de alta Inductancia pueden causar un zumbido severo, especialmente en los nodos de conmutación. Se selecciona un controlador de puerta IC capaz de soportar este tipo de timbre sin ningún efecto adverso. El tablero de cuatro capas está hecho de dos onzas de cobre, con dos capas internas de tierra y energía. Todas las reglas para un buen cableado deben ser observadas en el cableado.

Influencia de la Inductancia de la puerta

A una frecuencia de conmutación de 300 kHz, la Inductancia de la puerta tiene poca influencia en la eficiencia. En la frecuencia de conmutación de 600 kHz, la influencia de la Inductancia de la puerta es más obvia, y la eficiencia cambia un 1,2% a 20a. A 1 MHz, la disminución de la eficiencia casi desaparece por completo. Todavía no hemos investigado esta causa, y podemos especular que la probabilidad de que el factor de resonancia cancele su pérdida es del 50%. La resonancia de la puerta de MOSFET debe estudiarse más a fondo. Observamos que la Inductancia de la puerta tiene poco efecto en la eficiencia del control y la sincronización de MOSFET.

Influencia de la Inductancia de la fuente

La Inductancia de la fuente tiene un efecto más significativo en la eficiencia. En algunos casos, tenemos que detener la prueba antes de que se alcance la corriente, ya que la temperatura del MOSFET es superior a 130℃. La figura 5 muestra los resultados del estudio MOSFET de control. Un examen cuidadoso de estos resultados muestra que el convertidor DC - DC no puede funcionar a plena 20a debido a la temperatura del MOSFET superior a 130 °C a una frecuencia de 300 kHz y una Inductancia del 100%. También se puede encontrar a 50% de Inductancia, 600 kHz y 1 MHz. Se observó que la disminución de la eficiencia debida a la Inductancia de la fuente era más grave que sin la Inductancia de la fuente. Cuando la Inductancia es del 50% y la corriente es de 15 a, la eficiencia se reduce en un 7% incluso a una frecuencia de conmutación de 300 kHz. Cuando la Inductancia es del 100%, la eficiencia disminuye al 11%. En las frecuencias de conmutación de 600 kHz y 1 MHz, en comparación con la ausencia de Inductancia de la fuente, el efecto es más obvio y la eficiencia se reduce más seriamente. Obviamente, incluso la Inductancia de baja fuente puede reducir la eficiencia, especialmente cuando la frecuencia de conmutación es de 600 kHz.

Efecto de la Inductancia de fuga

La detección de fugas puede causar un zumbido severo, que puede ser suficiente para causar que el MOSFET se rompa en condiciones extremas (figura 3). Esto también puede tener un efecto negativo en la eficiencia. La eficiencia es una función de la corriente de carga y la detección de fugas en diferentes frecuencias. Además, se pueden observar los siguientes resultados: cuando la corriente es de 15 a, 300 kHz y 50% de Inductancia, debemos interrumpir la prueba porque la temperatura del MOSFET es superior a 130℃. A la misma frecuencia, 100% Inductancia, no podemos obtener ninguna lectura porque el tono de llamada es demasiado grave. A 300 kHz y 12 a, la eficiencia de la detección de fugas del 50% es inferior al 0% en un 7%. Debido a la alta temperatura del MOSFET, la prueba no puede ser superior a 15a. A 600 kHz y 12,5 a, la eficiencia de detección de fugas del 50% es 8,5% menor que la del 0%. La temperatura del MOSFET es demasiado alta para ser probada por encima de 12.5a. A 1 MHz, debido a la alta temperatura del MOSFET, no se puede probar más de 5a.

Influencia de la Inductancia de la fuente de la puerta

Una mayor Inductancia de la fuente reducirá significativamente la eficiencia. Se ha demostrado la relación básica entre la eficiencia y la Inductancia de la puerta. Cuando se combina con inductores de fuente más pequeños, la situación general se hace muy clara - los inductores de puerta más grandes inevitablemente conducen a una mayor pérdida de potencia. Es necesario seguir estudiando la explicación de este resultado. Ahora podemos demostrar que la Inductancia de fuga y la Inductancia de la fuente deben reducirse en el rango de Inductancia razonable de la placa de circuito para asegurar una alta eficiencia del convertidor. Los resultados de la simulación son los siguientes: la Inductancia de la puerta y la fuente resuena con la Capacitancia de la fuente de la puerta de MOSFET. Cuando el HS - FET cierra la fuente de la puerta, el condensador se descarga a través de estas rutas inductivas. Cuando el MOSFET está apagado, la Inductancia obliga a la corriente de la puerta a seguir fluyendo y recarga la Capacitancia de la fuente de la puerta. La carga se descarga de nuevo de la misma manera y se invierte el voltaje de la fuente de la puerta del HS - FET. Dependiendo del ángulo de inclinación, el HS - FET se puede abrir de nuevo en caso de un gran cortocircuito. Este efecto se vuelve grave con una Inductancia de puerta tan alta. En algunos casos, incluso se puede ver un segundo efecto de cortocircuito. Como parte del Circuito de resonancia, la Inductancia de la fuente también puede funcionar de una segunda manera. Cuando se produce una corriente de cortocircuito, la Inductancia de la fuente limita la di / DT de la corriente de cortocircuito (la tasa de cambio de la corriente con el tiempo), limitando así la pérdida. La Inductancia de la fuente también causa retroalimentación negativa al voltaje de la fuente de la puerta y limita el cortocircuito. Estos efectos ocurren especialmente cuando la Inductancia de la puerta parasitaria es alta. Para mejorar la eficiencia, este efecto debe evitarse mediante el diseño, es decir, la Inductancia de la puerta debe diseñarse cuidadosamente para minimizarla.

Influencia de la Inductancia ls de la fuente HS

Estudiamos el efecto de la posición de Inductancia de la fuente parasitaria en la eficiencia. Por lo tanto, en el mismo número de circuitos de Inductancia de fuente parasitaria, el FET de control tiene una mayor influencia en su eficiencia que el FET sincrónico. Esto se debe a que el FET de control de interruptores lentos causa una pérdida adicional de conmutación, ya que el Vds que controla el FET es mayor que el Vds del FET sincrónico (la caída de tensión hacia adelante del FET sincrónico es pequeña) durante la conversión. Además, la retroalimentación de la Inductancia parasitaria a la tensión de drenaje de la puerta del FET tiene un efecto significativo en la corriente de fuga del HS - FET. Por el contrario, el efecto de la Inductancia de la fuente parasitaria en la corriente de fuga de ls - FET es sólo parcial, ya que puede ser eludida por el diodo de volumen de la FET sincrónica.

Efecto de MOSFET paralelo

Cuando MOSFET está en paralelo, En muchos casos, es poco probable que cada bucle MOSFET individual tenga el mismo parásito. Estudiamos el efecto de la Inductancia adicional en el bucle de fuga MOSFET sobre la eficiencia.. El efecto adverso de la Inductancia parasitaria en la eficiencia de conmutación MOSFET en el convertidor DC - DC se demuestra experimentalmente.. Las conclusiones son las siguientes: la Inductancia en el circuito fuente tiene una influencia grave, En segundo lugar, Inductancia similar en el circuito de drenaje. En nuestro tablero de pruebas, No encontramos ningún efecto serio relacionado con la Inductancia del Circuito de puerta. La disminución de la eficiencia está estrechamente relacionada con la frecuencia de conmutación del convertidor. La disminución de la eficiencia tiene una gran relación con la corriente de carga. En el caso de Inductancia parasitaria en el circuito de fuente y drenaje, Mayor corriente de carga, Mayor disminución de la eficiencia. En la aplicación actual del convertidor DC - DC, Debe prestarse especial atención al cableado de los PCB del sistema de potencia, MOSFET conmutado en particular. Una de las ventajas del uso de placas multicapas es reducir la resistencia parasitaria y la Inductancia inyectando la mayor cantidad de corriente posible en cada capa. Esto reduce la pérdida de resistencia y la pérdida de Inductancia parasitaria. Diseño del convertidor DC - DC de alta frecuencia, Hay muchos problemas de Inductancia parasitaria en los circuitos fuente y drenaje. La primera es la Inductancia encapsulada, Es posible cambiar MOSFET utilizando el paquete de baja Inductancia recientemente introducido. La segunda es la Inductancia parasitaria del motor PCB Board, Debe utilizar varias capas PCB Board Reducir la Inductancia de la trayectoria. Esto permite a los diseñadores utilizar menos condensadores para lograr una respuesta dinámica más rápida y un diseño de alta frecuencia exitoso. El diseño no puede evitar que la inducción parasitaria se mueva al circuito FET sincrónico, ya que el efecto de la Inductancia en el circuito FET sincrónico en la eficiencia global es menor que en el circuito FET de control.. Nota: en un ciclo de trabajo bajo, La resistencia parasitaria en el circuito de FET sincrónico puede reducir significativamente la eficiencia. Complex trade-offs need to be made in the design (trace width, Espesor del cobre, Rango de bucle efectivo, Offset, Etc..). Evitar MOSFET paralelo. La forma de reemplazar MOSFET en paralelo es a ñadir una fase adicional o utilizar un mejor MOSFET. Si no se puede evitar el paralelismo, Para MOSFET paralelo, La simetría eléctrica debe garantizarse en el diseño para obtener la misma distribución de corriente y el mismo tiempo de conmutación. PCB Board.