Otro caso especial de un sistema de reloj universal es el reloj interno Sistema de reloj sincrónico. Muchos ingenieros inexpertos pueden malinterpretar internamente Sistema de reloj sincrónico Sincronización como fuente, Y el control de igual longitud se lleva a cabo de acuerdo con el tiempo de sincronización de la fuente., Causa errores de diseño de tiempo.

En primer lugar, repasemos cómo determinar si el sistema es un reloj público. El blog anterior mencionó que encontrar el árbol del reloj y determinar la relación entre las señales del reloj es la clave para juzgar los sistemas de tiempo. El sistema de reloj común suele tener un cristal o cristal externo, a través del divisor de reloj (o FPGA puede enviar directamente diferentes relojes al conductor y al receptor) conectado al conductor y al receptor del sistema, la línea de reloj externa controla el tiempo del sistema, llamado sistema de reloj común.

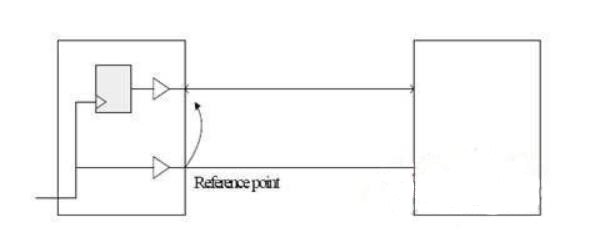

Señal de reloj Reloj sincrónico interno Enviar directamente desde el lado del conductor al lado del receptor. Los blogs anteriores mencionaron que el margen de tiempo para el sistema de reloj universal es pequeño, Uno de los factores clave que no pueden seguir aumentando la frecuencia es el TCO. Debido a factores como la tecnología, Es difícil hacer TCO demasiado pequeño. Por ejemplo:, El valor máximo de TCO de SDRAM es general. Hay 5.4ns. Interior Sistema de reloj sincrónico Reemplazar controladores de reloj externos con buffers internos, Hacer que los buffers en la señal del reloj y los buffers en la señal de datos coincidan para cancelarse entre sí, Por lo tanto, el rango entre el valor máximo y el valor mínimo del dispositivo TCO puede reducirse, y el margen de tiempo adicional hace que el tiempo sea fácil de cumplir..

El sistema de reloj sincrónico interno es fácil de confundir con la sincronización de la fuente. De hecho, es fácil distinguirlo dominar un principio. El tiempo de sincronización de la fuente suele estar presente en el reloj del sistema y en las señales de activación de los grupos de datos, como la relación entre DQ y dqs y CLK. El reloj sincrónico interno sólo tiene una señal de reloj compartida por el conductor y el receptor (en SDRAM móvil, la señal se llama sdck).

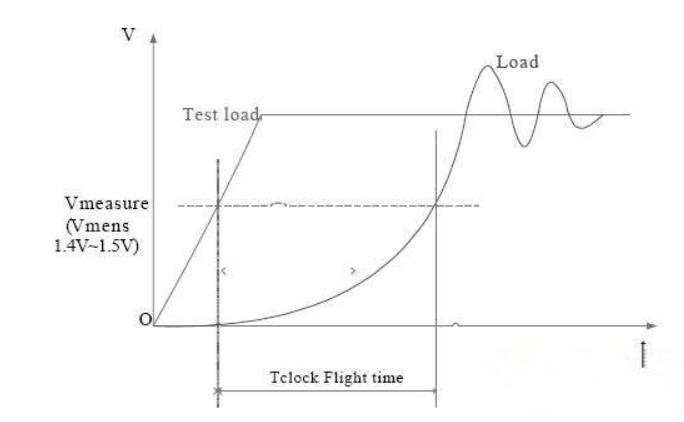

Por lo tanto, el tiempo de sincronización interna es computacionalmente similar a un reloj ordinario. Además de la desigualdad, hay una variable, tclk FT: el tiempo de vuelo del reloj. La figura 2 muestra el método de medición de tclk Ft.

La fórmula de cálculo del tiempo del reloj sincrónico interno es: (cuando el reloj y los datos se propagan en la misma dirección, es la dirección positiva)

TCO (max) + tflight (max) + tsetup - tclk Ft + tjitter + tmargin < tcycle

TCO (min) + tflight (min) - tclk FT - tmargin > thold

De esta manera, ajustando tclk Ft, el reloj puede estar en la posición óptima. El método también se puede utilizar para ajustar el tiempo en el modo de sincronización externa. Los métodos específicos de ajuste se han descrito en casos anteriores y pueden consultarse.

Resumen:

Externamente, la sincronización interna y la sincronización de fuentes son las mismas, pero tienen una estructura interna diferente. El método de sincronización de fuentes consiste en a ñadir un registro antes del Buffer de la señal del reloj en la estructura de sincronización interna, y el procesamiento del reloj dentro del chip es el mismo que el procesamiento de datos. De esta manera, el reloj puede variar con la velocidad de los datos y siempre estar en el Centro de los datos.

La esencia del reloj sincrónico interno sigue siendo el sistema universal de reloj. El cálculo del tiempo es el mismo que el sistema de reloj común del reloj externo, excepto que tclk Ft se añade o resta en ambos extremos del resultado del cálculo. La relación de restricción de tiempo es también la longitud total máxima y mínima, no la longitud igual.

Los relojes sincrónicos internos a ñaden un medio para ajustar el margen de tiempo, ya que compensa el impacto de TCO, por lo que el tiempo es más fácil de cumplir. Sin embargo, el método de cálculo del tiempo es más complejo y necesita ser dominado por los ingenieros de diseño.