¿¿ hay alguna forma en que el parche SMT pueda reducir algunos problemas de falla?

Los parches SMT se refieren a las siglas de una serie de procesos procesados sobre la base de pcb. El PCB (placa de circuito impreso) es una placa de circuito impreso. ¿Entonces, ¿ hay alguna manera en que el parche SMT pueda reducir algunos problemas de falla?

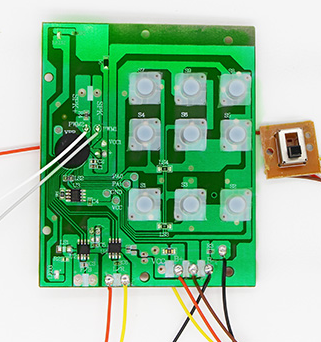

Parches SMT

El proceso de fabricación, la manipulación y las pruebas de componentes de circuitos impresos (pca) pueden hacer que el encapsulamiento esté sometido a una gran tensión mecánica, lo que puede causar fallas. A medida que los paquetes de matriz de red se hacen cada vez más grandes, es cada vez más difícil establecer niveles de Seguridad para estos pasos.

A lo largo de los años, el método de prueba del punto de flexión monótono ha sido una característica típica del embalaje. La prueba se describe en IPC / jedec - 9702 "propiedades de flexión monótonas de las interconexiones a nivel de placa". Este método de prueba describe la resistencia a la rotura de la interconexión horizontal de la placa de circuito impreso bajo carga de flexión.

Sin embargo, este método de prueba no puede determinar la tensión máxima permitida.

Para los procesos de fabricación y montaje, especialmente el PCA sin plomo, uno de los desafíos es que no se puede medir directamente el estrés en las juntas de soldadura. El indicador más utilizado para describir los riesgos de los componentes de interconexión es la tensión de las placas de circuito impreso de PCB adyacentes a los componentes, según se describe en la "guía de prueba de tensión de las placas de circuito impreso" IPC / jedec - 9704.

Hace unos años, Intel se dio cuenta del problema y comenzó a desarrollar una estrategia de prueba diferente para reproducir la peor situación de flexión en la práctica. Otras compañías como HP también se dieron cuenta de los beneficios de otros métodos de prueba y comenzaron a considerar ideas similares a las de intel. A medida que más y más fabricantes de chips y clientes se dan cuenta de que determinar los límites de tensión para minimizar las fallas mecánicas durante la fabricación, el procesamiento y las pruebas es de gran valor, este método ha atraído cada vez más atención. Interés

Con la expansión del uso de equipos sin plomo, los usuarios están cada vez más interesados; Porque muchos usuarios se enfrentan a problemas de calidad.

A medida que aumenta el interés, el IPC considera necesario ayudar a otras compañías a desarrollar diversos métodos de prueba para garantizar que bga no se dañe durante el proceso de fabricación y Prueba. Este trabajo ha sido llevado a cabo conjuntamente por el Grupo de trabajo de métodos de prueba de fiabilidad de accesorios SMT IPC 6 - 10d y el Subcomité de métodos de prueba de fiabilidad de equipos completos jedec JC - 14.1, y el trabajo se ha completado.

Este método de prueba especifica ocho puntos de contacto dispuestos en una matriz circular. El PCA con bga instalado en el Centro de la placa de circuito impreso de PCB se coloca de esta manera: el componente se instala boca abajo en el perno de soporte y la carga se aplica a la parte posterior de bga. Coloque el manómetro cerca de la pieza de acuerdo con el diseño del manómetro recomendado por IPC / jedec - 9704.

El PCA se doblará a los niveles de tensión asociados, y el análisis de falla puede determinar el grado de daño causado por la desviación de estos niveles de tensión. El método iterativo se puede utilizar para determinar el nivel de tensión que no causará daños. Este es el límite de tensión.