En el interiortroducción

Integridad de la señal Calidad de la señal en el sistema de circuitos digitales. Si la señal puede transmitirse de la fuente al receptor en el tiempo requerido sin distorsión, La señal se considera completa. Con el rápido desarrollo de la tecnología de semiconductores y la mejora de la velocidad de salida del interruptor IC, signal integrity issues (including signal overshoot and undershoot, Sonando, Reflejo, Crosstalk, Rebote en tierra, Etc..) have become one of the issues that must be paid attention to in high-speed Diseño de Placa de circuito impreso. . Normalmente, Circuitos lógicos digitales con frecuencias de hasta 50 MHz, Los circuitos que funcionan en esta frecuencia ocupan más de 1/3 de todo el sistema, Se puede llamar circuito de alta velocidad. De hecho,, En comparación con la frecuencia de la propia señal, Alta frecuencia armónica en el borde de la señal, and the rapid changes (rising and falling edges) of the signal cause unexpected effects of signal transmission. Esta es también la fuente del problema de integridad de la señal. Por consiguiente,, Cómo considerar plenamente el factor de integridad de la señal en la red de alta velocidad Diseño de Placa de circuito impreso Es necesario considerar el proceso y adoptar medidas de control eficaces para mejorar la calidad del diseño del circuito..

Con la ayuda de un poderoso software de simulación Cadence speetraquest, el análisis de simulación de la integridad de la señal de alta velocidad basado en el modelo Ibis es un método de análisis eficiente y factible, que puede encontrar el problema de la integridad de la señal, y realizar el problema relacionado de la integridad de la señal de acuerdo con los resultados de la simulación y optimizar el diseño. Con el fin de mejorar la calidad del diseño y acortar el ciclo de diseño.

1 ejemplo de diseño de aplicaciones

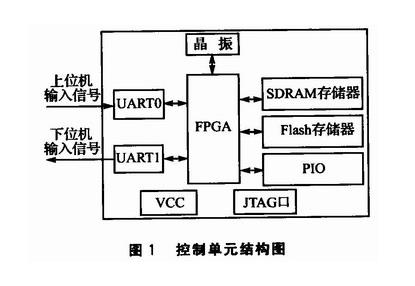

La función de la unidad de control diseñada en este documento es enviar la señal codificada recibida por el receptor terrestre al Centro de procesamiento de datos de la estación principal. El proceso de trabajo específico es almacenar los datos del host en primer lugar, luego a través de la prueba y el cálculo de la tasa de error de bits, elegir la ruta con la tasa de error de bits más baja como la ruta de transmisión de datos, y finalmente transferir los datos almacenados del host al Centro de procesamiento de datos de la estación principal a través de la ruta para el procesamiento. Después de una consideración integral, el chip central es el Cyclone II - 2c8 de alterações, as í como SDRAM, memoria flash, varios circuitos de entrada / salida y chip de interfaz max232, que se extienden externamente, y se implementan en combinación con el paquete de desarrollo del procesador de núcleo blando nios II. La estructura de la unidad de control se muestra en la figura 1.

La frecuencia de reloj del ciclone II - 2c8 es de hasta 150 MHz o más. Debido a que el área de almacenamiento de datos dentro de la FPGA es relativamente pequeña, SDRAM se utiliza para ampliar el espacio de almacenamiento de datos externos. SDRAM utiliza hy57v651610 / so de Hy Nix Company, y la frecuencia del reloj es superior a 75 MHz. Por lo tanto, es necesario considerar la integridad de la señal causada por la alta frecuencia de la señal. Elegí el potente software de diseño CAD ence, que integra el diseño esquemático, el diseño de Placa de circuito impreso y el análisis de simulación de alta velocidad. Puede resolver los problemas relacionados con el rendimiento eléctrico en todos los aspectos del diseño y mejorar en gran medida el diseño. Tasa de éxito.

2. Topología y simulación de señales clave

La parte de alta frecuencia del sistema es FPGA y SDRAM. La frecuencia de reloj de FPGA puede alcanzar más de 150 MHz, La frecuencia de reloj de SDRAM puede alcanzar más de 75 MHz. Debido a que la alta frecuencia interna de FPGA no afecta a otros dispositivos, La conexión entre FPGA y SDRAM es perfecta, La integridad de la señal afecta directamente la capacidad de lectura y escritura de SDRAM en FPGA. In Diseño de Placa de circuito impreso, Herramienta de simulación de alta velocidad spectraquest con software Cadence, La integridad de la señal se analiza utilizando el modelo Ibis del equipo., Se optimizan el emparejamiento de impedancia y la topología para asegurar el funcionamiento normal del sistema.. En este trabajo, sólo la reflexión de la señal y la conversación cruzada se explican en detalle., Otras simulaciones son similares.

2.1 reflexión

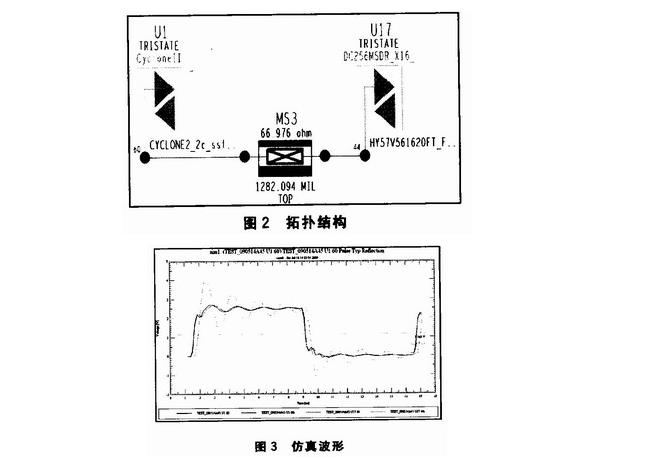

El transmisor es de 44 Pines hy57v561620, el receptor es de 60 Pines Cyclone II, y la excitación es de 66 MHz Onda cuadrada. La figura 2 muestra la topología y la figura 3 muestra la forma de onda analógica.

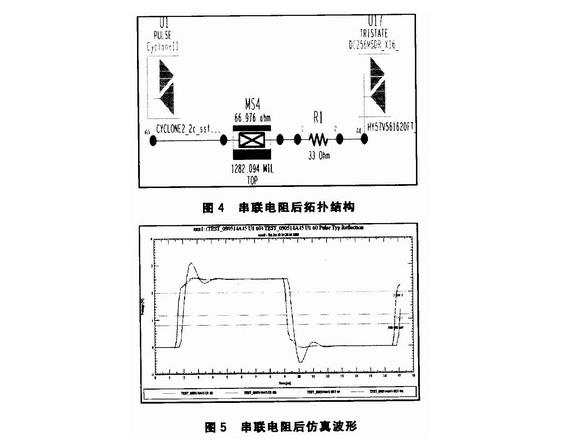

De la forma de onda simulada se puede ver que la distorsión de la forma de onda es causada por la reflexión de la señal, lo que resulta en un fenómeno obvio de zumbido. La existencia del fenómeno de la campana hace que la señal supere el umbral lógico del nivel muchas veces, lo que resulta en el trastorno de la función lógica. El método eficaz para reducir el ruido de timbre es conectar una pequeña resistencia en serie con el circuito, que proporciona amortiguación para el circuito, puede reducir significativamente la amplitud de timbre y acortar el tiempo de oscilación de timbre, mientras que la velocidad del circuito casi no se ve afectada. En aplicaciones de ingeniería, la resistencia es generalmente 33 ω. Las figuras 4 y 5 muestran la topología y la forma de onda analógica después de la resistencia en serie.

El fenómeno del anillo después de la resistencia en serie se resuelve bien. De hecho, esta solución se llama emparejamiento de impedancia. La impedancia es muy importante para la integridad de la señal.

2.2 comentarios cruzados

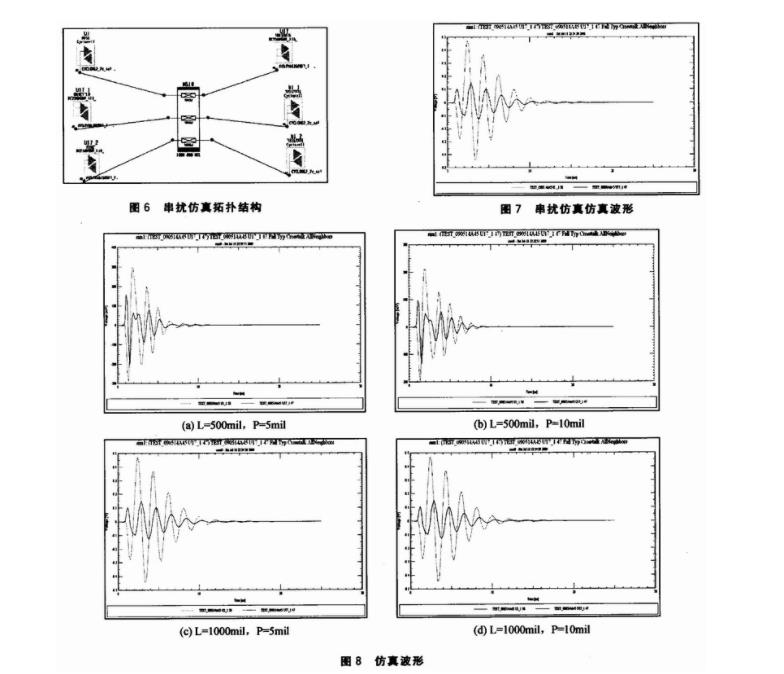

Se extrajeron las tres redes SD dqlo (59 Pines conectados a cyclone II y 45 Pines conectados a hy57v561620), SD dqll (58 Pines conectados a cyclone II y 47 Pines conectados a hy57v56620), SD DQ - L2 (57 Pines conectados a cyclone II y 48 Pines conectados a hy57v56620) para la simulación de conversación cruzada entre ellas. SD dqll es la red de ataque, SD dqlo y SD D - ql2 son la red de ataque. Sus topologías y formas de onda analógicas se muestran en las figuras 6 y 7 (la longitud de acoplamiento paralela de la línea de transmisión es l = 1000 mils, y el espaciamiento es p = 5 mils).

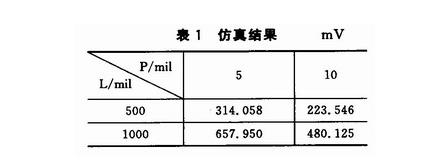

La forma de onda de simulación se muestra en la figura 8. Como se puede ver en la figura 7, crosstalk tiene una gran influencia en la red atacada. El valor crosstalk = 657,95 MV está relacionado con la longitud de acoplamiento paralelo L y el espaciamiento P de la línea de transmisión. Cuanto más corta es la longitud del acoplamiento, mayor es el espaciamiento. Cuanto más pequeña sea la conversación cruzada. Los resultados de la simulación se muestran en la Tabla 1.

Por consiguiente,, Hacer Placa de circuito impreso, Cuando sea posible, debe reducirse al mínimo la longitud paralela entre las líneas de señal de diferentes características., La distancia entre ellos debe ampliarse, Y el ancho de línea y la altura de algunas líneas deben cambiar. Por supuesto., Hay muchos factores que influyen en la conversación cruzada, Como la dirección actual y el tiempo de aumento de frecuencia de la señal de interferencia, Esto debe considerarse de manera integral.

Observaciones finales

A esta velocidad Diseño de Placa de circuito impreso Unidad de control, Potente software Cadence para obtener buenos resultados de la generación de diagramas esquemáticos, Placa de circuito impreso Análisis de simulación de diseño a alta velocidad. Topología y diseño razonables basados en el análisis de simulación de la cola de velocidad, La placa de circuito puede funcionar normalmente. Este método de diseño reduce en gran medida el tiempo de depuración del hardware, Mejorar la eficiencia del trabajo, Y ahorrar costos de diseño.