Este artículo explica cómo los cambios en el proceso conducen a cambios en la resistencia real y cómo usar solucionadores de campo precisos para predecir este fenómeno. Incluso si no hay cambios en el proceso, otros factores pueden hacer que la resistencia real sea muy diferente. Al diseñar placas de circuito de alta velocidad, las herramientas de diseño automatizado a veces no pueden encontrar este problema poco obvio pero muy importante. Sin embargo, este problema se puede evitar siempre que se tomen algunas medidas en las primeras etapas del diseño. Esta tecnología se llama "diseño defensivo".

Número de pilas

Una buena estructura apilada es la mejor precaución para resolver la mayoría de los problemas de integridad de la señal y los problemas de emc, y también es el problema más malinterpretado. Aquí funcionan varios factores, y una buena manera de resolver un problema puede empeorar otros. Muchos proveedores de diseño de sistemas recomiendan que haya al menos un plano continuo en la placa de circuito para controlar la resistencia característica y la calidad de la señal. Esta es una buena sugerencia siempre que el costo sea asequible. Los consultores de EMC a menudo recomiendan colocar un relleno de suelo o una formación de tierra en la capa exterior para controlar la radiación electromagnética y la sensibilidad a las interferencias electromagnéticas. También es una buena propuesta bajo ciertas condiciones.

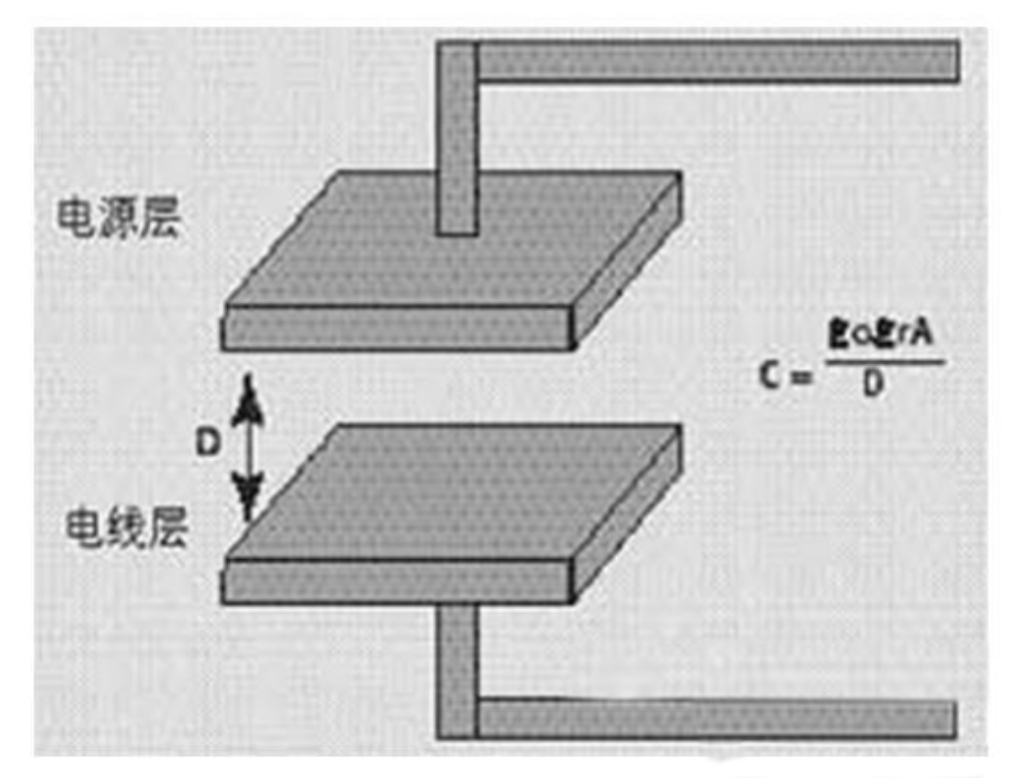

Figura 1: análisis de problemas de señal en estructuras apiladas con modelos de condensadores

Sin embargo, debido a las corrientes transitorias, este método puede ser engorroso en algunos diseños comunes. En primer lugar, echemos un vistazo a una situación simple de un par de planos de alimentación / planos de tierra: puede considerarse un capacitor. Se puede considerar que la capa de potencia y la formación de tierra son las dos placas polares del capacitor. Para obtener un mayor valor capacitivo, es necesario mover las dos placas más cercanas (a distancia d) y aumentar la constante dieléctrica (lambda ¼ ràn). Cuanto mayor sea el capacitor, menor será la resistencia, y eso es exactamente lo que queremos, porque puede suprimir el ruido. Independientemente de la disposición de las otras capas, la capa principal de alimentación y la capa de puesta a tierra deben ser adyacentes y ubicadas en el Centro de la pila. Si la distancia entre la capa de alimentación y la formación de tierra es grande, causará un circuito de corriente más grande y traerá mucho ruido. Para las placas de 8 capas, colocar la capa de alimentación en un lado y la formación de puesta a tierra en el otro lado causará los siguientes problemas:

1. máxima conversación cruzada. Debido al aumento de la capacidad mutua, la conversación cruzada entre las capas de señal es mayor que la conversación cruzada entre las propias capas.

2. mayor circulación. La corriente fluye alrededor de cada plano de alimentación y es paralela a la señal, y una gran cantidad de corriente entra en el plano de alimentación principal y regresa a través del plano de tierra. Debido al aumento de la corriente circulante, las características de EMC se deteriorarán.

3. perder el control de la resistencia. Cuanto más lejos esté la señal de la capa de control, menor será la precisión del control de resistencia debido a otros conductores a su alrededor.

4. debido a la facilidad de causar cortocircuitos en la soldadura, puede aumentar el costo del producto.

¿Tenemos que hacer una elección de compensación entre rendimiento y costo, entonces, ¿ cómo organizar las placas de circuito digitales para obtener las mejores características si y emc?

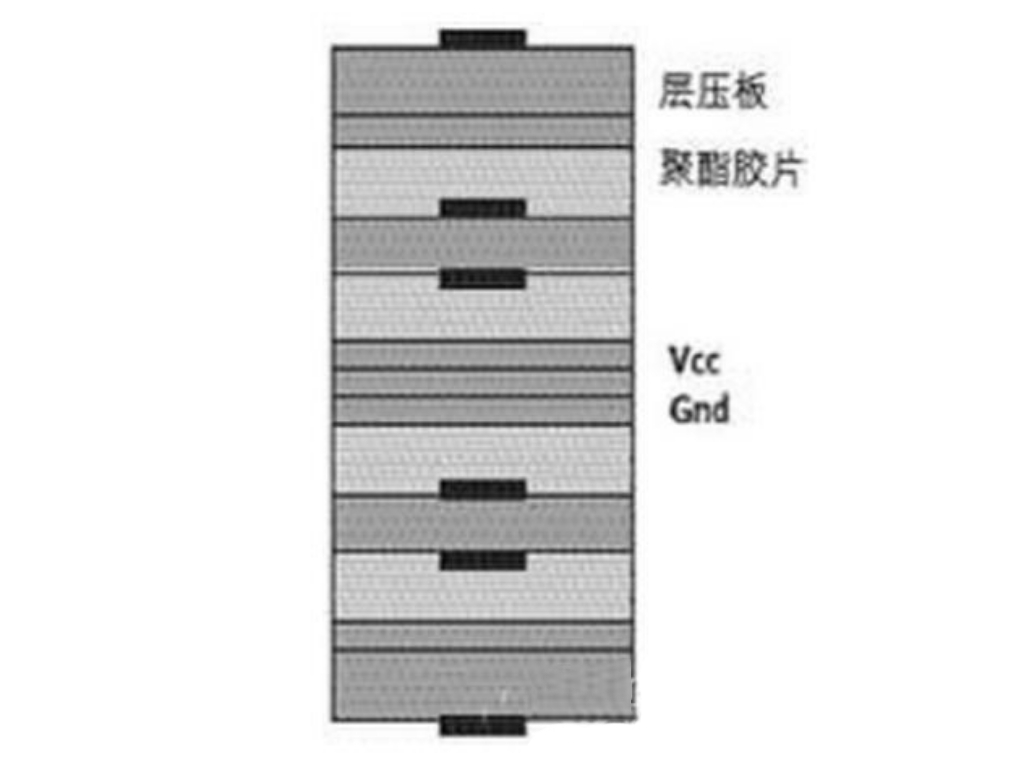

La distribución de cada capa del PCB suele ser simétrica. No se deben colocar más de dos capas de señal adyacentes entre sí; De lo contrario, el control del si se perderá en gran medida. Es mejor colocar las capas de señal interna simétricamente en parejas. A menos que ciertas señales necesiten ser cableadas a dispositivos smt, debemos minimizar el cableado de señales en la capa exterior.

Figura 2: el primer paso para una buena solución de diseño es diseñar correctamente la estructura laminada

Para las placas de circuito con más capas, podemos repetir este método de colocación muchas veces. También se pueden agregar capas de potencia adicionales y formaciones de tierra; Basta con asegurarse de que no haya un par de capas de señal entre las dos capas de potencia.

El cableado de la señal de alta velocidad debe colocarse en el mismo par de capas de señal; A menos que tenga que violar este principio debido a la conexión de dispositivos smt. Todos los rastros de la señal deben tener una ruta de retorno común (es decir, el plano de tierra). Para juzgar qué dos capas pueden considerarse como una pareja con dos ideas y métodos:

1. asegúrese de que la señal de retorno a la misma distancia sea exactamente la misma. Esto significa que la señal debe colocarse simétricamente a ambos lados del plano de tierra Interior. La ventaja de esto es que es fácil controlar la resistencia y la corriente circular; La desventaja es que hay muchos agujeros en la formación de contacto y algunas capas inútiles.

2. dos capas de señal de cableado adyacente. la ventaja es que los agujeros en la formación de conexión se pueden controlar al mínimo (utilizando agujeros enterrados); La desventaja es que para algunas señales clave, la efectividad de este método se reduce.

En el segundo método, la conexión a tierra para conducir y recibir la señal debe conectarse preferentemente directamente a la capa adyacente a la capa de cableado de la señal. Como simple principio de cableado, el ancho de cableado superficial en pulgadas debe ser inferior a un tercio del tiempo de subida de la conducción en nanosegundos (por ejemplo, el ancho de cableado del ttl de alta velocidad es de 1 pulgada).

Si se alimenta de varias fuentes de alimentación, se deben colocar estratos de conexión entre las líneas de alimentación para separarlas. No se pueden formar condensadores para evitar el acoplamiento de CA entre fuentes de alimentación.

Las medidas anteriores están diseñadas para reducir el ciclo y las conversaciones cruzadas y mejorar la capacidad de control de resistencia. El plano de tierra también formará una "caja blindada" efectiva de emc. Bajo la premisa de considerar el impacto en la resistencia característica, la superficie no utilizada se puede convertir en una formación de contacto.

Resistencia característica

Una buena estructura apilada puede controlar eficazmente la resistencia, y su cableado puede formar una estructura de línea de transmisión fácil de entender y predecible. Las herramientas de solución in situ pueden manejar bien este tipo de problemas, siempre y cuando el número de variables se controle al mínimo, se pueden obtener resultados bastante precisos.

Sin embargo, cuando tres o más señales se superponen, la situación no es necesariamente así, por razones delicadas. El valor de resistencia objetivo depende de la tecnología del proceso del equipo. La tecnología CMOS de alta velocidad suele alcanzar unos 70 angstroms; Los equipos ttl de alta velocidad suelen llegar a unas 80 a 100 islas. Debido a que los valores de resistencia suelen tener un gran impacto en la tolerancia al ruido y el cambio de señal, se debe tener mucho cuidado al seleccionar la resistencia; El manual del producto debe proporcionar orientación al respecto.

Los resultados preliminares de las herramientas de resolución in situ pueden encontrar dos problemas. El primero es el problema de la visión limitada. La herramienta de solución de campo solo analiza el impacto de los rastros cercanos, sin tener en cuenta los rastros no paralelos que afectan la resistencia en otras capas. Las herramientas de resolución de campo no pueden conocer los detalles antes de cableado, es decir, al asignar el ancho del rastro, pero el método de disposición emparejada anterior puede minimizar este problema.

Cabe mencionar la influencia del plano de potencia local. Después del cableado, las placas de circuito externas a menudo están llenas de cables de cobre de tierra, lo que favorece la inhibición del EMI y la galvanoplastia equilibrada. Si solo se toman tales medidas para la capa exterior, el impacto de la estructura apilada recomendada en este artículo en la resistencia característica será muy pequeño.

El efecto del uso de un gran número de capas de señal adyacentes es muy significativo. Algunas herramientas de solución de campo no pueden detectar la presencia de láminas de cobre, ya que solo puede comprobar la línea impresa y toda la capa, por lo que los resultados del análisis de resistencia no son correctos. Cuando hay metal en las capas adyacentes, es como una formación de conexión menos confiable. Si la resistencia es demasiado baja, la corriente instantánea será grande, lo que es un problema práctico y sensible del emi.

Otra de las razones del fracaso de la herramienta de análisis de Resistencia son los condensadores distribuidos. Estas herramientas de análisis generalmente no reflejan los efectos de los pines y los agujeros (este efecto se analiza generalmente con un simulador). Este efecto puede ser muy significativo, especialmente en la placa posterior. La razón es simple: la resistencia característica generalmente se puede calcular a través de la siguiente fórmula: àl / C

Entre ellos, L y c son inductores y condensadores por unidad de longitud, respectivamente.

Si los pines están bien dispuestos, los condensadores adicionales afectarán enormemente los resultados del cálculo. La fórmula se cambiará a: ¿ L / (c + c ')

C es un capacitor de pin por unidad de longitud.

Si el conector está conectado en línea recta al igual que el tablero trasero, se pueden utilizar condensadores de línea total y condensadores de pin total (excepto el primer y último pin). De esta manera, la resistencia efectiva se reducirá e incluso puede bajar de 80 a 8 islas. Para encontrar un valor válido, es necesario dividir el valor de resistencia original por: à (1 + c '/ c)

Este cálculo es muy importante para la selección de componentes.

Retraso

Al simular, se deben considerar los componentes y los condensadores encapsulados (a veces también se deben incluir inductores). Hay que tener en cuenta dos problemas: primero, el simulador puede no ser capaz de simular correctamente los condensadores distribuidos; En segundo lugar, se debe prestar atención al impacto de las diferentes condiciones de producción en capas incompletas y trazas no paralelas. Muchas herramientas de solución de campo no pueden analizar la distribución de la pila sin plena potencia o formación. Sin embargo, si hay una formación de tierra adyacente a la capa de señal, el retraso calculado será bastante malo, como los condensadores, habrá un retraso máximo; Si las dos capas de la placa de doble cara tienen muchos cables de tierra y láminas de cobre vcc, esta situación será más grave. Si este proceso no está automatizado, será muy caótico configurar estas cosas en el sistema cad.

EMC

Hay muchos factores que afectan a emc, muchos de los cuales generalmente no se analizan. Incluso si se analizan, a menudo es demasiado tarde después de que se complete el diseño. Estos son algunos de los factores que afectan a emc:

1. las grietas en el plano de potencia constituyen una antena de una cuarta longitud de onda. En los casos en que sea necesario instalar ranuras en contenedores metálicos, se debe utilizar el método de perforación.

2. elementos inductores. Una vez conocí a un diseñador que siguió todas las reglas de diseño y realizó simulaciones, pero su placa de circuito todavía tiene muchas señales de radiación. La razón es que hay dos inductores colocados en paralelo entre sí en la planta superior para formar un transformador.

3. debido a la influencia del plano de tierra incompleto, la baja resistencia de la capa interior conduce a una gran corriente instantánea en la capa exterior.

La mayoría de estos problemas se pueden evitar mediante la adopción de diseños defensivos. En primer lugar, se deben desarrollar las estructuras de apilamiento correctas y las estrategias de cableado para tener un buen comienzo.

Aquí no se abordan algunos problemas básicos, como la topología de la red, la causa de la distorsión de la señal y el método de cálculo de comentarios cruzados; Solo se analizan algunos temas delicados para ayudar a los lectores a aplicar los resultados obtenidos del sistema eda. Cualquier análisis depende del modelo utilizado y los factores no analizados también influyen en los resultados. Demasiado complicado es como demasiado impreciso. Evitar cambios excesivos en los parámetros (como imprimir el ancho de línea, etc.) ayudará a un diseño limpio y consistente.