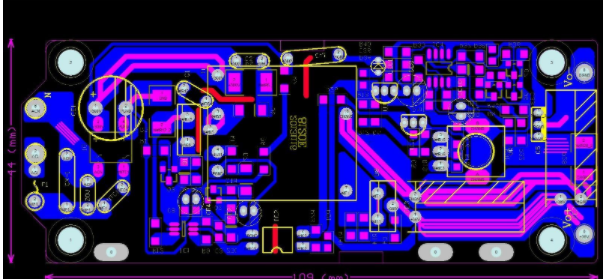

Artikel ini fokus pada perancang PCB yang menggunakan IP, dan lebih lanjut menggunakan perancangan topologi dan alat penghalaan untuk menyokong IP untuk menyempurnakan keseluruhan rekaan PCB dengan cepat. Seperti yang boleh dilihat dari Figure 1, jurutera desain mempunyai tanggungjawab untuk mendapatkan IP dengan mengatur sejumlah kecil komponen yang diperlukan dan merancang laluan penyelesaian kritik antara komponen ini.

Apabila IP diterima, maklumat IP boleh disediakan kepada perancang PCB, dan perancang PCB akan menyelesaikan reka yang tersisa. Penjana PCB lebih lanjut menggunakan perancangan topologi dan alat penghalaan untuk menyokong IP untuk menyempurnakan keseluruhan rekaan PCB dengan cepat. Sekarang tidak perlu mendapatkan niat desain yang betul melalui interaksi dan proses iteratif antara jurutera desain dan perancang PCB. jurutera rancangan telah mendapat maklumat ini dan hasilnya cukup tepat, yang sangat membantu untuk perancang PCB. Dalam ramai rancangan, jurutera rancangan dan perancang PCB mesti melakukan bentangan interaktif dan penghalaan, yang mungkin menghabiskan banyak masa yang berharga untuk kedua-dua pihak. Dari pengalaman masa lalu, operasi interaktif diperlukan, tetapi memakan masa dan tidak berkesan.

Rancangan awal yang disediakan oleh jurutera desain hanya boleh menjadi lukisan manual, tanpa skala komponen yang betul, lebar bas atau maklumat output pin.

Sebagai perancang PCB berpartisipasi dalam rancangan, jurutera yang menggunakan teknologi perancangan topologi boleh mendapatkan bentangan dan sambungan komponen tertentu. Rancangan ini juga memerlukan bentangan komponen lain, koleksi IO dan struktur bas lain, dan selesai semua sambungan.

Penjana PCB perlu mengadopsi perancangan topologi dan berinteraksi dengan komponen bentangan PCB di bawah bentangan untuk mencapai bentangan terbaik dan perancangan interaktif, dengan itu meningkatkan efisiensi desain PCB. Dengan selesai bentangan kawasan-kawasan kunci dan kawasan-kawasan densiti tinggi dan memperoleh rancangan topologi, bentangan mungkin terdahulu rancangan topologi akhir. Oleh itu, beberapa laluan topologi mungkin perlu menggunakan bentangan yang wujud. Walaupun mereka mempunyai keutamaan yang lebih rendah, mereka masih perlu disambung. Oleh itu, sebahagian dari rancangan berputar sekitar bentangan komponen yang dihasilkan.

Selain itu, aras perancangan ini mungkin memerlukan perincian lebih lanjut untuk menyediakan keutamaan yang diperlukan untuk isyarat lain. Beberapa halangan sebelum laluan automatik bas tertentu boleh menyediakan algoritma dengan pilihan untuk lapisan laluan lain. Oleh kerana bas diatur ke baris ketat pada lapisan pertama, perancang mula merancang bahagian pertukaran sebagai lapisan ketiga, dengan perincian "3", dan pertimbangkan jarak bas melewati PCB. Perhatikan bahawa laluan topologi ini pada lapisan 3 lebih luas daripada lapisan atas kerana ia memerlukan ruang tambahan untuk mengakomodasi impedance. Selain itu, rancangan juga menentukan lokasi tepat penerbangan lapisan (17 lubang). Apabila laluan topologi bergerak ke bawah dari bahagian kanan Figur 3 ke perincian "4", banyak titik sambungan bentuk-T satu-bit perlu dilukis dari sambungan laluan topologi dan setiap pin komponen. Penjana PCB memilih untuk menyimpan sebahagian besar sambungan pada lapisan 3 dan menembus lapisan lain untuk menyambung pin komponen.

Oleh itu, mereka melukis kawasan topologi untuk menunjukkan sambungan dari perlengkapan utama ke lapisan keempat (merah jambu), dan menyambung unit T-contact ke lapisan kedua, dan kemudian menggunakan vial lain untuk menyambung ke pins peranti. Laluan topologi terus pada lapisan 3 ke maklumat terperinci "5" untuk menyambung peranti aktif. Sambungan ini kemudian disambung dari pins aktif ke resisten tarik-turun di bawah peranti aktif.

Penjana menggunakan spesifikasi kawasan topologi lain untuk menyambung dari lapisan 3 ke lapisan 1, di mana pins komponen adalah peranti aktif dan resisten tarik-turun. Aras rancangan terperinci ini boleh selesai dalam kira-kira 30 saat. Selepas mendapat rancangan ini, penjana PCB mungkin ingin melalui segera atau mencipta rancangan topologi lanjut, dan kemudian menyelesaikan semua rancangan topologi melalui laluan automatik. Ia mengambil kurang dari 10 saat dari selesai rancangan hingga hasil kabel automatik. Malah, kelajuan ini tidak penting. Sebenarnya, jika anda mengabaikan niat desainer, kualiti laluan automatik sangat lemah, yang merupakan sia-sia masa. Ia mengambil kira-kira 10 saat untuk melakukan kabel automatik kualiti tinggi. Dengan meningkatkan aras abstraksi ke rancangan topologi, seluruh masa sambungan diperkirakan. Sebelum sambungan bermula, desainer mempunyai pemahaman yang benar-benar jelas tentang ketepatan dan potensi untuk menyelesaikan desain. Contohnya, mengapa menjaga garis pada titik ini dalam desain? Mengapa tidak terus merancang dan menambah baris di belakang? Bila topologi lengkap dirancang?

Jika anda mempertimbangkan contoh di atas, abstraksi rancangan boleh digunakan dengan rancangan lain selain dari 17 rangkaian independen dengan banyak segmen dan banyak lubang di setiap rangkaian. Konsep ini sangat penting bila mempertimbangkan arahan perubahan teknik (ekologi, projek).

Perintah Perubahan Keenjasan (ECO) Dalam contoh berikut, output pin FPGA belum selesai. Injurutera rancangan telah memberitahu perancang PCB tentang realiti ini, tetapi untuk alasan kemajuan, mereka perlu maju rancangan sebanyak mungkin sebelum output pin FPGA selesai. Dalam kes output pin yang diketahui, perancang PCB mula merancang ruang FPGA, dan perancang menyelesaikan perancangan pada masa yang sama, sementara juga mempertimbangkan memimpin dari peranti lain ke FPGA. IO asalnya direncanakan untuk berada di sebelah kanan FPGA, tetapi sekarang di sebelah kiri FPGA, menyebabkan output pin sama sekali berbeza dari rancangan asal.

Penjana PCB boleh menggunakan alat perancangan topologi pada permulaan desain, atau mereka boleh menggunakannya selepas jurutera merancang mendapatkan IP, bergantung kepada siapa yang menggunakan alat fleksibel ini untuk menyesuaikan dengan baik kepada persekitaran merancang mereka. Kawalan topologi hanya mengikut rancangan atau niat desainer untuk menyediakan keputusan kabel PCB berkualiti tinggi. Apabila menghadapi ECO, rancangan topologi jauh lebih cepat daripada operasi sambungan terpisah, jadi peralatan kabel topologi boleh mengadopsi ECO lebih cepat, dengan itu menyediakan keputusan yang cepat dan tepat.