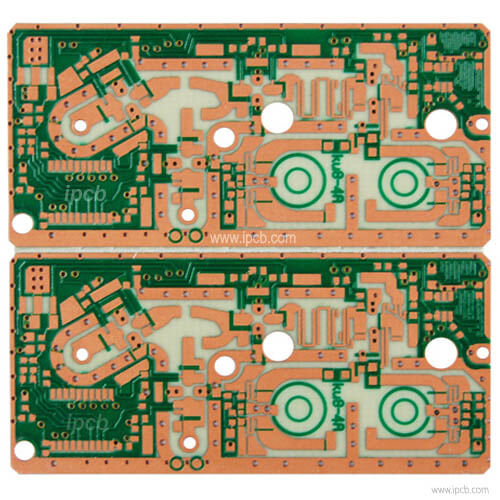

Dengan pembangunan cepat teknologi elektronik dan aplikasi luas teknologi komunikasi tanpa wayar dalam berbagai bidang, frekuensi tinggi, kelajuan tinggi, dan ketepatan tinggi secara perlahan-lahan menjadi salah satu perkembangan yang signifikan produk elektronik modern. Rangkaian PCB Frekuensi Tinggi kekuatan penghantaran isyarat PCB ke lubang mikro dan lubang terkubur/buta, konduktor halus, lapisan tengah seragam tipis, frekuensi tinggi, teknologi reka PCB berbilang lapisan tinggi telah menjadi medan kajian penting. Berdasarkan bertahun-tahun pengalaman dalam rancangan perkakasan, penulis mengungkapkan beberapa keterampilan rancangan dan perkara yang memerlukan perhatian sirkuit frekuensi tinggi untuk rujukan anda.

25. Bagaimana untuk mencapai keperluan EMC sebanyak mungkin tanpa menyebabkan tekanan biaya terlalu banyak?

Kebanyakan peningkatan kos EMC pada papan PCB biasanya disebabkan peningkatan bilangan lapisan untuk meningkatkan kesan perisai dan peningkatan Ferrite Bead, Choke, dan peranti penghalang harmonik frekuensi tinggi lainnya. Selain itu, biasanya diperlukan untuk menggabungkan struktur perisai pada mekanisme lain untuk membuat seluruh sistem melewati keperluan EMC. Berikut hanya beberapa tip desain untuk papan PCB untuk mengurangi kesan radiasi elektromagnetik yang dihasilkan oleh sirkuit.

Peranti dengan kadar isyarat perlahan dipilih sejauh mungkin untuk mengurangi komponen frekuensi tinggi yang dihasilkan oleh isyarat.

Perhatikan lokasi peranti frekuensi tinggi. Jangan letakkan mereka terlalu dekat dengan sambungan luaran.

Perhatikan padanan impedance isyarat kelajuan tinggi, lapisan kabel, dan laluan semasa kembali untuk mengurangi refleksi frekuensi tinggi dan radiasi.

Letakkan kapasitor penyahpautan yang cukup dan sesuai pada pins kuasa setiap peranti untuk mengurangkan bunyi pada lapisan kuasa dan formasi. Perhatikan khas sama ada tindak balas frekuensi dan karakteristik suhu kondensator memenuhi keperluan desain.

26. apabila papan PCB mempunyai lebih dari satu nombor/modul blok fungsi, praktek konvensional adalah untuk memisahkan nombor/modul, mengapa?

Alasan bagi pemisahan tanah digital/mod adalah bahawa litar digital menghasilkan bunyi dalam kuasa dan tanah apabila menukar antara potensi tinggi dan rendah. Saiz bunyi bergantung pada kelajuan isyarat dan saiz semasa. Jika pesawat tanah tidak dibahagi dan bunyi yang dijana oleh sirkuit kawasan digital adalah besar sementara sirkuit kawasan analog sangat dekat, isyarat analog masih akan diganggu oleh bunyi tanah walaupun isyarat digital dan analog tidak menyeberangi. Maksudnya, mod digital dan analog tidak terpisah hanya boleh digunakan apabila kawasan sirkuit analog jauh dari kawasan sirkuit digital yang menghasilkan bunyi besar.

27. Cara lain ialah memastikan bentangan berbeza nombor/modul dan garis isyarat nombor/modul tidak saling saling saling, seluruh papan PCB tidak dibahagi, nombor/modul disambung ke pesawat tanah. Mengapa?

Keperluan bahawa isyarat analog tidak boleh menyeberangi wayar adalah bahawa laluan semasa kembali isyarat digital yang lebih cepat akan cuba mengalir kembali ke sumber isyarat digital sepanjang tanah dekat bawah kabel. Jika isyarat analog menyeberangi wayar, bunyi yang dijana oleh arus balik akan muncul di kawasan sirkuit analog.

28. Bagaimana untuk mempertimbangkan masalah sepadan impedance apabila merancang diagram skematik desain PCB kelajuan tinggi?

Perpadanan kemudahan adalah salah satu unsur kunci dalam merancang sirkuit PCB kelajuan tinggi. Nilai impedance berkaitan dengan mod laluan. Contohnya, jarak antara lapisan permukaan (microstrip) atau lapisan dalaman (garis garis/garis garis ganda), lapisan rujukan (lapisan kuasa atau stratum), lebar kabel, dan bahan PCB semua akan mempengaruhi nilai keterangan pengendalian laluan. Itu untuk menentukan nilai impedance selepas kabel. Perisian simulasi umum akan disebabkan oleh model garis atau keterangan algoritma matematik yang digunakan untuk mempertimbangkan beberapa situasi pengendalian kabel berhenti, pada masa ini dalam diagram skematik hanya boleh simpan beberapa penghenti, seperti perlawanan siri, untuk mengurangkan kesan pengendalian kabel berhenti. Solusi dasar sebenar untuk masalah atau kabel sejauh mungkin adalah untuk menghindari kejadian penghalangan yang tidak berhenti.

Di mana saya boleh memberikan asas model IBIS yang lebih tepat?

Ketepatan model IBIS mempengaruhi secara langsung keputusan simulasi. IBIS boleh dianggap sebagai data karakteristik elektrik sirkuit yang sama dengan penimbal I/O cip sebenar, yang boleh diubah oleh model SPICE (atau diukur, tetapi terdapat lebih banyak keterangan). Namun, data SPICE berkaitan dengan penghasilan cip, jadi peranti yang sama disediakan oleh penghasil cip yang berbeza. Data SPICE berbeza, dan data dalam model IBIS yang diubah akan berbeza. Maksudnya, jika peranti pembuat A digunakan, hanya mereka boleh menyediakan data model yang tepat untuk peranti mereka kerana tiada siapa yang lebih tahu daripada mereka apa proses peranti mereka dibuat oleh. Jika IBIS yang disediakan oleh penjual tidak tepat, satu-satunya penyelesaian dasar adalah untuk terus-menerus meminta penjual untuk memperbaikinya.

30. Dalam rancangan PCB kelajuan tinggi, aspek mana yang perancang patut mempertimbangkan peraturan EMC dan EMI?

Secara umum, rancangan EMI atau EMC perlu mempertimbangkan kedua-dua aspek radiasi dan dilakukan. Yang pertama adalah bahagian frekuensi yang lebih tinggi (> 30MHz) yang terakhir adalah bahagian frekuensi yang lebih rendah (< 30 MHZ). Jadi anda tidak boleh fokus pada frekuensi tinggi dan abaikan frekuensi rendah. Rancangan EMI/EMC yang baik mesti dianggap pada permulaan bentangan kedudukan peranti, pengaturan laminasi PCB, laluan dalam talian yang penting, pemilihan peranti, dll., jika ia tidak mempunyai pengaturan yang lebih baik secara lanjut, penyelesaian akan kurang berkesan, meningkatkan kos. Contohnya, kedudukan generator jam seharusnya tidak dekat dengan sambungan luaran sebanyak yang mungkin, isyarat kelajuan tinggi seharusnya pergi ke lapisan dalaman sebanyak yang mungkin dan memperhatikan kesimpulan persamaan impedance karakteristik dan lapisan rujukan untuk mengurangi refleksi, - cerun isyarat dipandu oleh peranti seharusnya sebanyak yang mungkin untuk mengurangi komponen frekuensi tinggi, Bila memilih kondensator penyahpautan/bypass, perhatikan sama ada tindak balas frekuensi memenuhi keperluan untuk mengurangi bunyi lapisan kuasa. Selain itu, perhatikan laluan aliran belakang isyarat frekuensi tinggi untuk mengurangi kawasan loop (iaitu impedance loop) untuk mengurangi radiasi. Julat bunyi frekuensi tinggi juga boleh dikawal dengan membahagi formasi. Akhirnya, tanah chassis antara PCB dan chassis dipilih dengan betul.

31. Bagaimana untuk memilih alat EDA?

Dalam perisian desain PCB semasa, analisis panas bukan titik yang kuat, jadi ia tidak disarankan untuk menggunakannya. Seperti untuk fungsi lain, 1.3.4 PADS atau Cadence boleh dipilih, kedua-dua prestasi dan kos adalah baik. Pemula rancangan PLD boleh guna persekitaran terintegrasi yang disediakan oleh pembuat cip PLD, dalam rancangan lebih dari satu juta pintu boleh memilih alat titik tunggal.

32. Sila cadangkan perisian EDA yang sesuai untuk pemprosesan dan penghantaran isyarat kelajuan tinggi.

Untuk rancangan sirkuit umum, INNOVEDA PADS sangat baik, dan ia kompatibel dengan perisian simulasi, yang sering mengandungi 70% aplikasi. Untuk desain sirkuit kelajuan tinggi, sirkuit hibrid analog dan digital, menggunakan penyelesaian Cadence adalah perisian terbaik untuk prestasi dan harga, tentu saja, prestasi Mentor sangat baik, terutama pengurusan proses desain seharusnya adalah yang terbaik. (Datang Telecom ahli teknik Wang Sheng)

33. Penjelasan makna setiap lapisan papan PCB?

Topoverlay- Nama komponen lapisan atas, juga dipanggil Top Silkscreen atau Top Component Legend, seperti R1, C5, IC10. Di bawah -- perkara yang sama dengan pelbagai lapisan -- jika and a merancang papan 4 lapisan dan anda letakkan pad bebas atau melalui, takrifkannya sebagai darab maka papannya secara automatik muncul pada semua 4 lapisan, jika anda hanya takrifkannya sebagai lapisan atas, maka papannya hanya muncul pada lapisan atas.

34. Apa yang patut diberikan perhatian dalam desain, penghalaan, dan pencetakan PCB frekuensi tinggi di atas 2G?

Di atas 2G PCB frekuensi tinggi milik desain sirkuit rf, bukan dalam skop desain sirkuit digital kelajuan tinggi. Bentangan dan penghalaan litar RF patut dianggap bersama dengan skema kerana bentangan dan penghalaan akan menyebabkan kesan distribusi. Selain itu, rancangan sirkuit rf beberapa peranti pasif diselesaikan dengan parameterisasi takrifan foil tembaga bentuk istimewa, jadi alat EDA diperlukan untuk menyediakan peranti parametrik yang boleh edit foil tembaga bentuk istimewa. Mentor BoardStation telah dedikasi modul reka RF untuk memenuhi keperluan ini. Selain itu, rancangan RF umum memerlukan alat analisis sirkuit RF khusus, yang paling terkenal adalah Agilent's Eesoft, yang mempunyai antaramuka yang baik dengan alat Mentor.

35. Untuk semua isyarat digital PCB, papan mempunyai sumber jam 80MHz. Selain mata wayar (grounding), apa jenis perlindungan sirkuit patut digunakan untuk memastikan kapasitas memandu yang cukup?

Pastikan kemampuan pemacu jam, tidak sepatutnya dicapai melalui perlindungan, biasanya menggunakan cip pemacu jam. Kebimbangan umum tentang kemampuan pemacu jam adalah kerana muatan jam berbilang. Ambil cip pemacu jam, tukar satu isyarat jam ke beberapa, jadikan sambungan titik ke titik. Pilih cip pemacu, selain memastikan padanan asas dengan muatan, isyarat bersama dengan keperluan (biasanya jam bersama isyarat yang berkesan), dalam pengiraan masa sistem, untuk mengira jam dalam lambat cip pemacu.