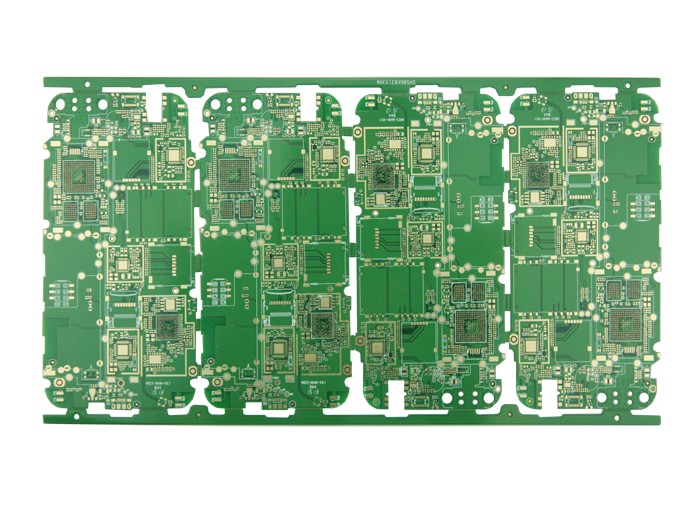

Fenomen 1: Keperlukan rancangan PCB papan PCB ini tidak tinggi, jadi gunakan wayar yang lebih tipis dan mengatur secara automatik. Komen: Kawalan automatik tidak dapat dihindari mengambil kawasan PCB yang lebih besar, dan pada masa yang sama, ia akan menghasilkan banyak kali lebih banyak vias daripada wayar manual. Dalam batch Dalam produk yang besar, selain faktor perniagaan, faktor yang penghasil PCB mempertimbangkan untuk pengurangan harga ialah lebar garis dan bilangan vial, yang secara berdasarkan itu mempengaruhi hasil PCB dan bilangan bit pengeboran yang dikonsumsi, yang menyimpan kos penyedia dan juga memberikan pengurangan harga ditemui sebab.

Sinyal bas ini semua ditarik oleh pemberontak, jadi saya rasa lega.

Komen: Ada banyak sebab kenapa isyarat perlu ditarik ke atas dan ke bawah, tetapi tidak semua perlu ditarik. Penolak tarik-naik dan tarik-turun menarik isyarat input sederhana, dan semasa kurang dari puluhan mikroamper, tetapi apabila isyarat dipandu ditarik, semasa akan mencapai aras miliamp. Sistem semasa sering mempunyai 32 bit data alamat masing-masing, dan mungkin jika bas tersingkir 244/245 dan isyarat lain ditarik, beberapa watt penggunaan kuasa akan dikonsumsi pada resisten ini.

Fenomen 3: Bagaimana untuk menangani port I/O yang tidak digunakan ini CPU dan FPGA? Biarkan ia kosong dahulu, dan bercakap tentang ia kemudian.

Komen: Jika port I/O yang tidak digunakan ditinggalkan mengapung, ia mungkin menjadi isyarat input yang berulang-ulang berubah dengan sedikit gangguan dari dunia luar, dan penggunaan kuasa peranti MOS pada dasarnya bergantung pada bilangan pusingan sirkuit gerbang. Jika ia ditarik ke atas, setiap pin juga akan mempunyai arus mikroampere, jadi cara terbaik adalah untuk menetapkannya ke output (tentu saja, tiada isyarat lain dengan memandu boleh disambungkan ke luar) Fenomen 4: FPGA ini mempunyai banyak yang tersisa Anda tidak boleh lari keluar pintu, jadi mari kita mainkannya keluar. Komen: Penggunaan kuasa FGPA adalah proporsional dengan bilangan flip-flops yang digunakan dan bilangan flips, jadi penggunaan kuasa jenis FPGA yang sama dalam sirkuit berbeza dan masa berbeza mungkin 100 kali berbeza. Mengurangkan bilangan flip-flops untuk flip kelajuan tinggi adalah cara asas untuk mengurangkan konsumsi kuasa FPGA.

Fenomen 5: Penggunaan kuasa cip kecil ini sangat rendah, tidak perlu mempertimbangkan komen: sukar untuk menentukan penggunaan kuasa cip yang tidak rumit dalam, ia ditentukan oleh semasa pada pin, ABT16244, penggunaan kuasa tanpa muatan mungkin kurang dari 1 mA, Tetapi penunjuknya adalah bahawa setiap pin boleh memandu muatan 60 mA (seperti sepadan dengan perlawanan puluhan ohms), iaitu, konsum kuasa maksimum muatan penuh boleh mencapai 60*16=960mA, tentu saja ia hanya bekalan kuasa Dengan arus yang besar, semua panas jatuh pada muatan.

Fenomen 6: Ingatan mempunyai banyak isyarat kawalan. Papan PCB saya hanya perlu menggunakan isyarat OE dan WE. Pilihan cip patut didasarkan, supaya data keluar lebih cepat semasa operasi baca.

Komen: Penggunaan kuasa kebanyakan ingatan bila pemilihan cip adalah sah (tidak kira OE dan WE) akan lebih daripada 100 kali lebih besar daripada bila pemilihan cip tidak sah. Oleh itu, CS sepatutnya digunakan untuk mengawal cip sebanyak mungkin, dan selagi keperluan lain dipenuhi. Ia mungkin untuk pendek lebar tekanan pemilihan cip.

Fenomen 7: Mengapa isyarat ini melebihi? Selagi persamaan adalah baik, komen boleh dibuang: Kecuali beberapa isyarat khusus (seperti 100BASE-T, CML), terdapat overshoot, selama ia tidak terlalu besar, ia tidak perlu disesuaikan, walaupun ia disesuaikan, ia tidak perlu disesuaikan. Terbaik. Contohnya, impedance output TTL kurang dari 50 ohms, dan sekitar 20 ohms. Jika perlawanan yang sepadan besar seperti ini digunakan, semasa akan sangat besar, penggunaan kuasa akan tidak diterima, dan amplitud isyarat akan terlalu kecil untuk digunakan. Selain itu, impedance output isyarat umum apabila mengeluarkan tahap tinggi dan mengeluarkan tahap rendah tidak sama, dan tidak ada cara untuk mencapai padanan lengkap. Oleh itu, persamaan TTL, LVDS, 422 dan isyarat lain boleh diterima selagi overshoot dicapai.

Fenomen 8: Pengurangan konsumsi kuasa adalah masalah karyawan perkakasan, dan tidak ada hubungannya dengan perisian