Design isyarat LVDS pada papan PCB bukan sahaja isyarat berbeza, tetapi juga isyarat digital kelajuan tinggi. Oleh itu, tidak kira-kira media transmisi LVDS menggunakan wayar papan PCB atau kabel, tindakan mesti diambil untuk mencegah isyarat tersembunyi di terminal media, dan gangguan elektromagnetik mesti dikurangkan untuk memastikan integriti isyarat. Selama kita mempertimbangkan elemen ini apabila kabel, merancang papan sirkuit berbeza kelajuan tinggi tidak terlalu sukar. Berikut secara singkat memperkenalkan titik desain isyarat LVDS pada papan PCB: 2.1 Bentangan ke papan lapisan berbilang Circuit papan dengan isyarat LVDS biasanya ditetapkan sebagai papan berbilang lapisan. Kerana isyarat LVDS adalah isyarat kelajuan tinggi, lapisan sebelah patut menjadi lapisan tanah untuk melindungi isyarat LVDS untuk mencegah gangguan. Untuk papan dengan densiti rendah, jika keadaan ruang fizikal membenarkan, letakkan isyarat LVDS dan isyarat lain pada lapisan yang berbeza. Contohnya, dalam papan empat lapisan, lapisan biasanya boleh ditetapkan sebagai berikut: lapisan isyarat LVDS, lapisan tanah, lapisan kuasa, dan lapisan isyarat lain. 2.2 Pengiraan dan kawalan impedance isyarat LVDS. Perubahan tegangan isyarat LVDS hanya 350mV, yang sesuai untuk operasi isyarat berbeza dipandu semasa. Untuk memastikan isyarat tidak dipengaruhi oleh isyarat terrefleks apabila ia merebak dalam garis transmisi, isyarat LVDS memerlukan impedance garis transmisi untuk dikawal, dan impedance perbezaan biasanya 100 +/- 10Ω. Kualiti kawalan pengendalian secara langsung mempengaruhi integriti isyarat dan lambat.

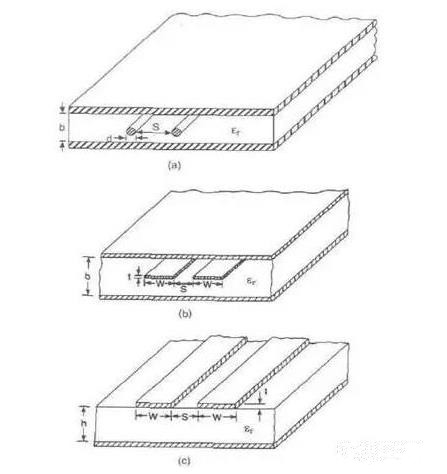

1. Bagaimana untuk mengawal penghalang papan PCB? 1.1 Tentukan mod kabel, parameter dan pengiraan impedance. LVDS dibahagi ke mod perbezaan garis garis garis garis garis microstrip lapisan luar dan mod perbezaan garis garis garis garis lapisan dalaman. Impedasi boleh dihitung dengan menetapkan parameter secara rasional dan menggunakan perisian berkaitan. Melalui pengiraan, nilai penghalang adalah secara langsung proporsional dengan tebal lapisan penghalang, dan secara terbaliknya proporsional dengan konstan dielektrik, tebal dan lebar wayar.1.2 Ikut prinsip garis ekvivalen paralel dan sambungan ketat. Selepas menentukan lebar dan jarak baris, mengikut lebar dan jarak baris yang dihitung secara ketat semasa menjalin, dan jarak antara kedua-dua baris mesti sentiasa tetap, iaitu, ia mesti selari (anda boleh letak gambar). Pada masa yang sama, prinsip sambungan ketat diperhatikan bila menghitung lebar garis dan jarak, iaitu, jarak garis pasangan perbezaan adalah kurang atau sama dengan lebar garis. Apabila dua garis isyarat berbeza sangat dekat, arah transmisi semasa adalah bertentangan, medan magnetik membatalkan satu sama lain, medan elektrik disambung satu sama lain, dan radiasi elektromagnetik jauh lebih kecil. Juga, dua wayar mesti berada di lapisan yang sama untuk menghindari wayar lapisan. Kerana dalam proses sebenar papan PCB, darjah laminasi diantara tumpukan jauh lebih rendah daripada ketepatan pencetakan lapisan yang sama, dan kerugian dielektrik semasa proses laminasi tidak dapat menjamin bahawa jarak diantara garis perbezaan sama dengan tebal dielektrik antara lapisan, Yang akan menyebabkan perubahan impedance perbezaan pasangan perbezaan antara lapisan.

1.3 Pergi singkat dan lurus. Untuk memastikan kualiti isyarat, jejak pasangan perbezaan LVDS sepatutnya pendek dan lurus yang mungkin, mengurangkan bilangan vial dalam kawat, dan menghindari kawat pasangan perbezaan terlalu panjang dan terlalu banyak pusingan. Cuba guna 45° atau lengkung di sudut. Menghindari pusingan 90°. Tiada keterangan pada pemilihan kaedah laluan pasangan LVDS antara pasangan baris berbeza. Garis garis garis mikro dan garis garis boleh digunakan, tetapi mesti dicatat bahawa terdapat pesawat rujukan yang baik. Penjarakan antara garis perbezaan berbeza tidak sepatutnya terlalu kecil, dan sepatutnya sekurang-kurangnya 3-5 kali ruang antara garis perbezaan. Jika diperlukan, tambah pengasingan lubang tanah antara pasangan garis berbeza berbeza untuk mencegah salib bercakap. Jauhkan isyarat LVDS dari isyarat lain sebanyak mungkin. Isyarat perbezaan LVDS tidak boleh dibahagi melalui pesawat. Walaupun dua isyarat perbezaan adalah laluan kembalian satu sama lain, segmen salib tidak akan memotong kembalian isyarat, tetapi garis pemindahan seluruh segmen akan menyebabkan penghentian dalam impedance disebabkan kekurangan pesawat rujukan (seperti yang dipaparkan dalam figur, di mana GND1 dan GND2 disebelah dengan pesawat tanah LVDS). Jarak diantara perlawanan yang sepadan bagi hujung penerima dan pin penerima sepatutnya hampir mungkin. Pada masa yang sama, ketepatan perlawanan yang sepadan mesti dikawal. Untuk topologi titik ke titik, pengendalian jejak biasanya dikawal pada 100Ω, tetapi perlawanan yang sepadan boleh disesuaikan mengikut situasi sebenar. Darjah lawan adalah 1%-2%. Kerana menurut pengalaman, 10% ketidaksepadan impedance akan menghasilkan refleksi 5%.

2. Analisis simulasi isyarat LVDS siriThe above analyzes the matters that must be paid attention to when designing LVDS signals. Walaupun peraturan di atas biasanya diikuti semasa rancangan PCB, untuk meningkatkan ketepatan dan ketepatan rancangan, simulasi isyarat lengkap PCB mesti dilakukan melalui simulasi. Mendapatkan percakapan salib isyarat, lambat, refleksi dan bentuk gelombang corak mata, untuk mencapai tujuan desain yang betul. Proses simulasi masalah integriti isyarat adalah untuk pertama-tama menetapkan model simulasi komponen, dan kemudian melakukan prasimulasi untuk menentukan parameter dan kekangan proses kabel. Tahap penyelesaian fizikal dirancang mengikut keterangan, dan post-simulasi dilakukan untuk mengesahkan sama ada rancangan memenuhi keperluan rancangan. Sifat model dalam seluruh proses mempengaruhi secara langsung keputusan simulasi, dan kaedah analisis simulasi yang digunakan dalam tahap pra-simulasi dan pos-simulasi juga kritikal untuk keputusan simulasi, dan darjah lebih tinggi model rempah digunakan dalam desain ini. Berikut adalah kombinasi projek-projek sebenar untuk memperlihatkan proses implementasi simulasi dalam desain ini.2.1 tetapan tumpukan papan PCB Dari analisis di atas, diketahui bahawa tetapan tumpukan papan PCB berkaitan dengan sambungan isyarat dan pengiraan impedance. Oleh itu, rancangan stacking mesti dilakukan sebelum rancangan papan PCB, dan kemudian pengiraan impedance bagi isyarat.2.2 Tetapkan nilai tegangan DC Langkah ini adalah terutama untuk nyatakan nilai tegangan DC bagi rangkaian tertentu (biasanya tanah kuasa, dll.), menentukan tegangan DC yang akan dilaksanakan pada rangkaian, - dan melakukan simulasi EMI memerlukan menentukan satu atau lebih pin sumber tenaga. Nilai tekanan ini termasuk maklumat tekanan rujukan yang digunakan oleh model dalam proses simulasi diterangkan.2.3 Tetapan peranti Semasa simulasi allegro, allegro membahagi peranti ke tiga kategori: IC, konektor dan peranti diskret (kondensator perlahan, dll.), allegro akan memberikan atribut simulasi kepada pins peranti mengikut jenis peranti, Atribut adalah UPSPEC, dan atribut pin IC boleh IN, OUT, BI, dll. Model peranti biasanya disediakan oleh pembuat peranti. Dalam isyarat seri kelajuan tinggi, apa yang kita jadikan adalah model SPICE dengan ketepatan yang lebih tinggi untuk melanjutkan analisis simulasi. Model garis trasmis dibentuk melalui model perisian simulasi. Apabila isyarat sedang dihantar, garis penghantaran akan membuat masalah integriti isyarat terkenal, jadi kemampuan perisian simulasi untuk modelkan garis penghantaran secara langsung mempengaruhi hasil simulasi.2.5 inspeksi SIThe SI Audit function is used to check whether a particular network or a group of networks can be extracted for analysis. Secara umum, ia adalah untuk menetapkan rangkaian kelajuan tinggi yang kita perlu perhatikan. Ralat ini terutama fokus pada isyarat berantai LVDS.2.6 Ekstrak topologi rangkaian Ekstrak struktur topologi isyarat minat dari papan PCB, umumnya termasuk hujung pemandu dan hujung penerima, serta garis pemindahan dan resisten dan kondensator yang berkaitan. Ia boleh dilihat dari topologi bahawa rangkaian melalui laluan tersebut, yang akan menyebabkan pengaruh transmisi isyarat. Artikel ini hanya mengambil diagram topologi rangkaian bagi salah satu isyarat sebagai contoh: seperti yang dipaparkan dalam Gambar 4:2.7 Papar bentuk gelombang Selepas langkah berkaitan di atas ditetapkan, simulasi boleh dilakukan. Allegro boleh melakukan simulasi refleksi isyarat dan simulasi percakapan salib, dan garis perbezaan juga perlu melakukan analisis diagram mata. Sudah tentu, simulasi juga dibahagi menjadi pre-simulasi dan post-simulasi. Apabila menggunakan allegro untuk merancang papan PCB, perlu mengubah rancangan dalam masa sebenar dengan hasil simulasi untuk memenuhi keperluan. Kerana proses simulasi adalah rumit dan langkah-langkah adalah rumit, saya tidak akan menggambarkannya satu demi satu. Ada dua titik untuk memperhatikan dalam kabel pasangan perbezaan. Pertama ialah panjang kedua-dua garis sepatutnya sebanyak mungkin, dan panjang sama adalah untuk memastikan kedua-dua isyarat perbezaan tetap bertentangan setiap masa. Polariti untuk mengurangi komponen mod umum. Yang lain ialah jarak antara dua garis (jarak ini ditentukan oleh impedance perbezaan) mesti sentiasa kekal konstan, iaitu, ia mesti kekal selari. Ada dua cara selari, satu adalah bahawa dua wayar berjalan di sebelah-sebelah, dan yang lain adalah bahawa dua wayar berjalan di dua lapisan bersebelahan di atas dan di bawah (atas-bawah). Secara umum, yang pertama mempunyai lebih banyak implementasi sebelah-sebelah. Keutamaan keseimbangan adalah untuk memastikan pengendalian perbezaan yang sama antara kedua-dua dan mengurangkan refleksi. Kaedah kabel pasangan perbezaan sepatutnya dekat dan selari dengan sesuai. Kedekatan yang dipanggil sesuai adalah kerana jarak ini akan mempengaruhi nilai impedance perbezaan, yang merupakan parameter penting untuk merancang pasangan perbezaan. Keperluan untuk paralelisme adalah juga untuk menjaga konsistensi impedance perbezaan. Jika kedua garis tiba-tiba jauh dan dekat, pengendalian perbezaan akan tidak konsisten, yang akan mempengaruhi integriti isyarat dan lambat masa. Dari graf S-parameter simulasi, impedance perbezaan pasangan perbezaan dan integriti isyarat boleh dianalisis. Bentuk gelombang simulasi isyarat kunci dalam rancangan ini diberi di bawah untuk penjelasan. Ia boleh dilihat dari legenda simulasi Figur 5 bahawa indeks degradasi S11 dalam domain frekuensi 0-3.0GHz adalah: di bawah