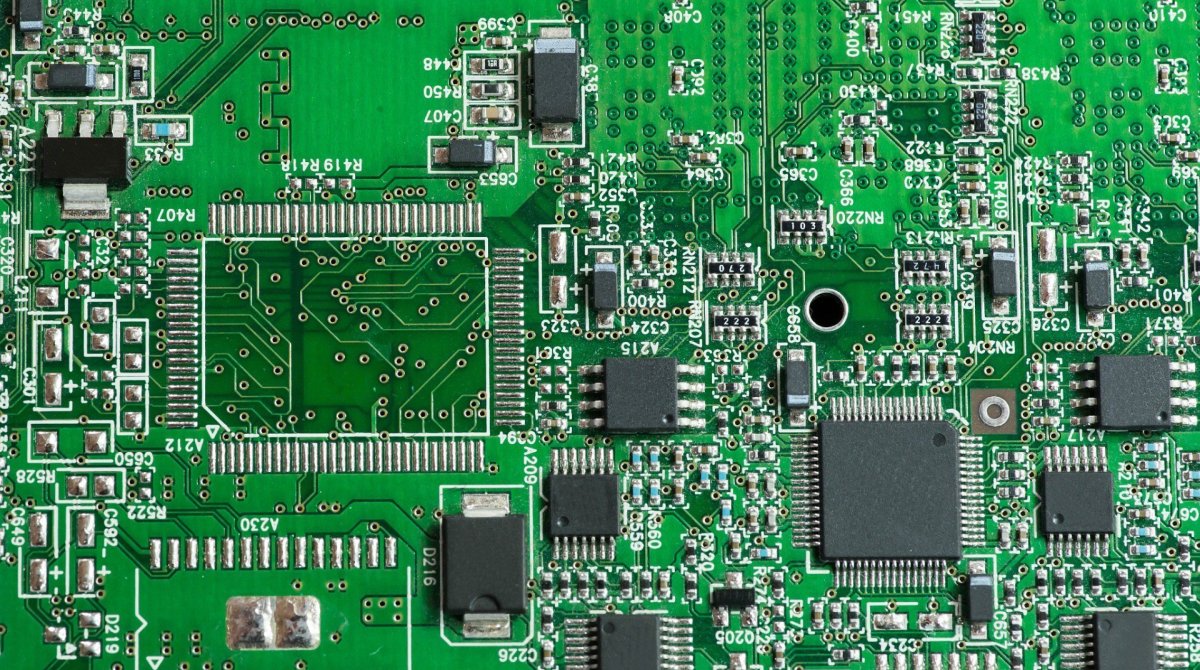

Ini beberapa faktor yang Papan PCB designers must consider and will influence their decisions:

1. Product functions

1) Basic functions of the basic requirements of the cage cover, termasuk:

a. Interaksi antara diagram skematik dan bentangan PCB

b. Fungsi wayar seperti wayar penggemar-keluar automatik, push-pull dan fungsi kabel lain, as well as wiring capabilities based on design rule constraints

c. Pengesahan DRC

2) Kemampuan untuk maju ciri-ciri produk semasa syarikat terlibat dalam rancangan yang lebih kompleks

a. HdI (High density Interconnection) interface

b. Flexible design

c. Embed passive components

d. Radio frequency (RF) design

e. Automatic scripting is natural

f. Topology layout and cabling

g. Manufacturability (DFF), testability (DFT), producability (DFM), etc

3) Additional products can perform analog simulation, simulasi digital, simulasi isyarat campuran analog, simulasi isyarat kelajuan tinggi dan simulasi RF

4) Memiliki perpustakaan komponen pusat yang mudah dicipta dan menguasai

2. Kawan baik yang secara teknikal dalam kepemimpinan industri dan telah menuangkan lebih banyak usaha daripada penghasil lain boleh membantu and a merancang produk yang efektif dan teknikal dalam masa singkat.

3. Harga patut menjadi pertimbangan sekunder diantara faktor di atas, dan lebih perhatian patut diberikan kepada ROI.

Perkiraan PCB perlu mempertimbangkan banyak faktor. Jenis perancang alat pembangunan mencari bergantung pada kompleksiti kerja desain yang mereka lakukan. Because systems are becoming increasingly complex, the control of physical wiring and electrical component placement has evolved to such an extent that constraints must be set for hub paths in the design process. Namun, terlalu banyak keterangan rancangan menghalang fleksibiliti rancangan. Para desainer mesti mempunyai pengetahuan yang baik tentang rancangan dan peraturan mereka supaya mereka tahu bila untuk menggunakannya. Ia menunjukkan rancangan sistem terintegrasi biasa dari bahagian depan hingga bahagian belakang. Ia bermula dengan definisi rancangan (input skematik) yang terintegrasi dengan kuat dengan pengekodan ketat. Dalam pengekodan ketat, perancang boleh takrifkan ketat fizikal dan elektrik. Hadangan elektrik akan melakukan analisis layout pre - dan post - untuk emulator pemacu pengesahihan rangkaian. Melihat dengan teliti definisi desain, ia juga terhubung dengan integrasi FPGA/PCB. Tujuan integrasi FPGA/PCB adalah menyediakan integrasi dua arah, pemerintahan data, dan kemampuan untuk melakukan reka-reka antara FPGas dan PCB. Peraturan keterangan yang sama untuk pelaksanaan fizik dimasukkan semasa fasa bentangan seperti semasa definisi rancangan. Ini mengurangkan peluang membuat kesilapan dari fail ke bentangan. Penukaran pin, penukaran pintu logik, dan bahkan kumpulan antaramuka input/output (IO_Bank) menukar semua perlu kembali ke tahap definisi desain untuk kemaskini, jadi desain setiap langkah disegerakan.

Mari kita lihat beberapa trends yang memaksa desainer untuk memeriksa semula ciri-ciri alat pembangunan mereka yang wujud dan mula memesan yang baru:

1. HDI

Kekompleksiti Semikoduktor dan peningkatan bilangan pintu logik telah memerlukan sirkuit terintegrasi untuk mempunyai lebih banyak pin dan ruang pin yang lebih baik. Sekarang biasa untuk merancang lebih dari 2000 pin pada peranti BGA dengan jarak pin 1 mm, walaupun 296 pin pada peranti dengan jarak pin 0.65 mm. Masa naik lebih cepat dan keperluan integriti isyarat (SI) memerlukan lebih banyak bekalan tenaga destinasi dan pins tanah, memerlukan lebih banyak lapisan dalam papan pelbagai lapisan, sehingga memandu keperluan teknologi sambungan densiti tinggi (HDI) dengan mikroperforasi. HDI adalah teknologi sambungan yang sedang dikembangkan sebagai balas kepada keperluan ini. Karakteristik utama teknologi HDI ialah lubang mikro dan dielektrik ultra-tipis, wayar lebih baik dan jarak garis lebih kecil.

2. Ralat RF

Untuk reka-reka RF, Sirkuit RF patut direka secara langsung ke dalam skema sistem dan bentangan papan sistem, daripada persekitaran terpisah untuk pertukaran berikutnya. Semua simulasi, penyesuaian, dan kemampuan optimasi persekitaran emulasi RF masih diperlukan, tetapi persekitaran emulasi boleh menerima lebih banyak data mentah daripada rancangan "nyata". Sebagai hasil, perbezaan antara model data dan perubahan desain yang berasal akan hilang. Pertama, desainer boleh berinteraksi secara langsung antara desain sistem dan simulasi RF. Kedua, jika desainer bekerja pada desain RF skala besar atau proporsional kompleks, mereka mungkin mahu membahagikan tugas simulasi sirkuit antara platforma komputer berbilang berjalan secara selari, atau mereka mungkin mahu pendek masa simulasi dengan menghantar setiap sirkuit dalam desain multi-modul ke emulator sendiri.

3. Perbaiki pakej terdahulu

Kekompleksiti fungsi yang meningkat bagi produk modern memerlukan peningkatan yang sama dalam bilangan peranti pasif, kebanyakan dalam bilangan kondensator penyahpautan dan resisten yang sepadan terminal untuk aplikasi kuasa rendah dan frekuensi tinggi. Walaupun pakej peranti lekap permukaan pasif telah berkurang dalam bertahun-tahun, hasilnya masih sama bila cuba mendapatkan ketepatan pembatasan. Printed component technology enabled the transition from multi-chip components (MCM) and hybrid components to today's SiP and PCBS that are directly available as embedded passive components. Teknik pemasangan yang digunakan dalam proses pengubahan. Contohnya, the inclusion of an impedance material layer in a layered structure and the use of series terminal resistors directly under the microsphere grid array (uBGA) package have greatly improved the performance of the circuit. Komponen pasif termasuk boleh dirancang dengan ketepatan tinggi, menghapuskan langkah proses tambahan penyelamatan laser. Komponen tanpa wayar juga bergerak ke arah memperbaiki integrasi langsung dalam substrat.

4. PCB fleksibel ketat

Untuk merancang PCB yang ketat dan fleksibel, semua faktor yang mempengaruhi proses pemasangan mesti dianggap. Penjana tidak boleh merencanakan PCB fleksibel yang ketat seolah-olah PCB fleksibel yang ketat adalah PCB yang ketat lain. Mereka mesti merawat kawasan bengkok rancangan untuk memastikan titik rancangan tidak akan membawa kepada kerosakan konduktor dan pelepasan disebabkan tekanan di permukaan bengkok. Masih ada banyak faktor mekanik untuk dipertimbangkan, seperti radius bengkok, tebal dielektrik dan jenis, berat logam lembaran, plat tembaga, tebal sirkuit keseluruhan, bilangan lapisan dan bilangan seksyen bengkok. Memahami rancangan fleksibel yang ketat dan memutuskan jika produk and a membolehkan anda mencipta rancangan fleksibel yang ketat.

5. Rencanaan integriti isyarat

Dalam tahun-tahun terakhir, teknologi baru berkaitan dengan arkitektur bas selari dan arkitektur pasangan berbeza untuk pengubahan berantai atau sambungan berantai telah diperbaiki. Hadangan rancangan bas selari terletak dalam variasi masa sistem, seperti peluruan jam dan lambat pembebasan. Rancangan untuk keterangan masa masih sukar kerana jam melewati seluruh lebar bas. Meningkatkan kadar jam hanya membuat masalah lebih teruk. Di sisi lain, arkitektur pasangan berbeza menggunakan sambungan titik ke titik yang boleh ditukar untuk menyadari komunikasi berantai pada aras perkakasan. Biasanya, ia memindahkan data melalui "saluran" berantai satu-arah yang boleh dikumpulkan dalam konfigurasi lebar 1-, 2-, 4-, 8-, 16-, dan 32. Setiap saluran membawa satu bait data, jadi bas boleh mengendalikan lebar data dari 8 bait ke 256 bait, dan integriti data boleh dikekalkan dengan menggunakan beberapa bentuk teknik pengesan ralat. Namun, kadar data yang tinggi menyebabkan masalah reka lain. Pemulihan jam pada frekuensi tinggi menjadi beban bagi sistem, kerana jam dengan cepat mengunci dalam aliran data input dan minimumkan semua siklus ke penggelisahan siklus untuk meningkatkan prestasi anti-gelisah sirkuit. Bunyi kuasa juga mengakibatkan masalah tambahan untuk desainer. Jenis bunyi ini meningkatkan kemungkinan kegelisahan yang berat, yang membuat membuka mata lebih sukar. Another challenge is to reduce common-mode noise and solve problems caused by lossy effects from IC packages, PCBS, cables and connectors.

6. Penggunaan set desain

Design kits such as USB, DDR/DDR2, PCI-X, PCI-Express dan RocketIO pasti akan membantu desainer bergerak ke teknologi baru. Suit desain memberikan paparan ringkasan teknologi, arahan terperinci, dan desainer cabaran akan menghadapi, diikuti oleh simulasi dan bagaimana untuk mencipta keterangan kabel. Ia menyediakan dokumentasi deklaratif bersama dengan program, yang memberi desainer permulaan utama pada teknologi baru yang berkembang pada yang lebih tua. Nampaknya mudah untuk mendapatkan Papan PCB alat yang boleh mengendalikan bentangan; Tetapi penting untuk mendapatkan alat yang tidak hanya memenuhi keperluan anda tetapi juga memenuhi keperluan anda segera.