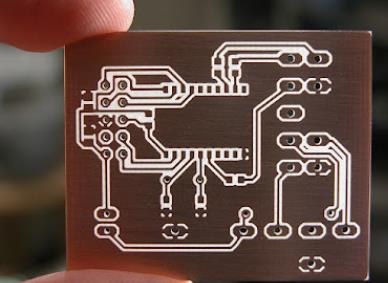

Kelajuan Tinggi Papan PCB Teknologi rancangan disambungkan termasuk ujian, simulasi, dan berbagai-bagai standar berkaitan, di mana ujian adalah kaedah dan cara untuk mengesahkan keputusan pelbagai analisis simulasi. Kaedah ujian yang paling penting adalah syarat yang diperlukan untuk memastikan analisis desain sambungan. Untuk ujian bentuk gelombang isyarat tradisional, kebimbangan utama ialah panjang sonda yang menyebabkan mengelakkan bunyi yang tidak diperlukan diperkenalkan oleh Pigtail. Kertas ini terutama membincangkan aplikasi baru dan pembangunan teknologi ujian saling sambung. Dalam tahun-tahun terakhir, with the continuous improvement of the signal rate, objek ujian telah mengalami perubahan yang signifikan. Ia tidak lagi terbatas kepada penggunaan tradisional osciloskop untuk menguji bentuk gelombang isyarat. Bunyi tanah bekalan kuasa, synchronous switching noise (SSN), and jitter (Jitter) have gradually become The focus of interconnect design engineers, beberapa alat dalam medan RF telah dilaksanakan untuk desain saling sambung. Instrumen ujian yang biasanya digunakan dalam desain saling sambung termasuk analisis spektrum, penganalisis rangkaian, osciloskop, dan pelbagai sond dan peralatan yang digunakan oleh alat-alat ini, yang telah berubah secara signifikan untuk mengakomodasi kadar isyarat yang semakin meningkat. Menggunakan alat ujian ini sebagai alat, kertas ini terutama memperkenalkan pembangunan teknologi ujian rancangan antara sambungan dalam tahun-tahun terakhir dari aspek berikut:

1) Kaedah kalibrasi ujian

2) Kaedah pemodelan peranti pasif

3) Ujian Integriti Kuasa

4) Kaedah ujian penggerak isyarat jam

Antara tiga alat ujian yang biasa digunakan, kaedah kalibrasi penganalisis rangkaian adalah ketat, diikuti oleh penganalisis spektrum, dan kaedah kalibrasi oscilloscope adalah mudah. Oleh itu, kita terutama membincangkan kaedah kalibrasi penganalisis rangkaian di sini. Terdapat tiga kaedah kalibrasi yang biasa digunakan untuk analisis rangkaian, Thru, TRL, dan SOLT. Intian Thru adalah normalisasi. Semasa kalibrasi, penganalisis rangkaian merakam hasil ujian pemasangan (S21_C). Dalam ujian sebenar, bahagikan terus keputusan ujian (S21_M) dan S21_C untuk mendapatkan keputusan ujian DUT (S21_A). . Pengkalibrasi Thru mengabaikan refleksi disebabkan oleh ketidaksepadan dalam pemasangan ujian serta pasangan elektromagnetik dalam ruang, oleh itu, akurasi kalibrasinya. Kaedah kalibrasi ini boleh digunakan bila hanya S21 diuji dan akurasi ujian tidak diperlukan. Dalam struktur bukan-Koaksial seperti papan PCB, kadang-kadang perlu menguji ciri-ciri jejak, unit synonyms for matching user input, konektor, dll. Dalam kes ini, penyedia alat ujian tidak menyediakan bahagian kalibrasi piawai, dan sukar bagi penguji untuk membuat sirkuit terbuka, sirkuit pendek, muatan yang sepadan, dan bahagian kalibrasi lain di port kalibrasi ujian, Jadi kalibrasi SOLT tradisional tidak boleh dilakukan. Keuntungan pengkalibrasi dengan TRL adalah bahawa potongan pengkalibrasi piawai tidak diperlukan dan port pengkalibrasi ujian boleh diperoleh ke lokasi yang diinginkan. Pada masa ini, kalibrasi TRL telah digunakan secara luas dalam ujian struktur papan PCB. SOLT biasanya dianggap sebagai kaedah kalibrasi piawai. Terdapat keseluruhan 12 parameter ralat kalibrasi dalam model kalibrasi, dan pelbagai ralat dikalibrasi dan dikira dengan menggunakan sirkuit pendek, sirkuit terbuka, muatan, dan melalui. Kerana penyedia alat ujian biasanya hanya menyediakan bahagian kalibrasi Coaxial, kaedah kalibrasi SOLT tidak boleh digunakan dalam struktur bukan-Coaxial. Kaedah kalibrasi di atas tiga boleh dianalisis secara terperinci dengan menggunakan graf aliran isyarat, di mana setiap parameter ralat mempunyai parameter yang sepadan dalam graf aliran isyarat. Melalui diagram aliran isyarat, sensitiviti ralat bagi pelbagai kaedah kalibrasi boleh dipahami dengan jelas, supaya memahami julat ralat ujian sebenar. Titik yang perlu dibuat di sini ialah bahawa walaupun kaedah kalibrasi SOLT piawai mengabaikan lima parameter ralat dalam model kalibrasi. Biasanya, lima parameter ralat ini tidak mempengaruhi ketepatan kalibrasi. Namun, jika anda tidak memperhatikan rancangan pemasangan kalibrasi semasa digunakan, akan ada fenomena yang tidak dapat dikalibrasi. Penganalisis spektrum menyediakan sumber piawai untuk kalibrasi. Semasa kalibrasi, anda hanya perlu sambung sumber piawai dalaman ke port input melalui pemasangan ujian. Kalibrasi mengambil kira-kira 10 minit. Kalibrasi oscilloscope lebih mudah. Sambungkan sonde ke sumber piawai dalaman dan sahkan ia. Kalibrasi mengambil kira-kira 1 minit.

Ujian dan Modelan Peranti Pasif

Dengan peningkatan terus menerus kadar isyarat, peran peranti pasif dalam rantai isyarat semakin penting. Ketepatan analisis simulasi prestasi sistem sering bergantung pada ketepatan model peranti pasif. Sebagai hasilnya, ujian dan pemodelan komponen pasif secara perlahan-lahan menjadi bahagian penting rancangan saling berhubungan dari pelbagai penyedia peralatan. Peranti pasif biasa digunakan adalah seperti berikut:

1) Connector

2) Papan PCB jejak dan vias

3) Capacitor

4) Induktensi (kacang magnetik)

In high-speed signal integrity designs, the impact of sambungan on the signal link. Untuk sambungan kelajuan tinggi yang sering digunakan, latihan biasa adalah untuk membuat pemasangan kalibrasi menurut kaedah kalibrasi TRL, dan menguji dan model sambungan untuk analisis simulasi. Kaedah pemodelan ujian jejak dan butang PCB adalah sama dengan kaedah sambungan. Kalibrasi TRL juga digunakan untuk memindahkan port ujian ke posisi yang diinginkan, dan kemudian pemodelan ujian dilakukan.

Jadual karakteristik impedance bekalan kuasa bagi papan tunggal

Model kemampuan mempunyai aplikasi dalam analisis integriti isyarat, dan yang lebih penting dalam analisis integriti kuasa. Instrumen pemodelan kapasitas yang biasa digunakan dalam industri adalah analisis impedance dan analisis rangkaian, yang sesuai untuk band frekuensi yang berbeza. Penganalisis kemampuan sesuai untuk band frekuensi rendah, dan penganalisis rangkaian sesuai untuk band frekuensi tinggi. Jika analisis rangkaian digunakan untuk ujian integriti kuasa dalam ujian sebenar, ia dicadangkan untuk menggunakan analisis rangkaian dalam seluruh band frekuensi pemodelan kapasitas untuk memastikan konsistensi pemodelan dan aplikasi. Kerana kekurangan pengendalian kondensator, selari sering digunakan bila memmodelkan dengan analisis rangkaian. Masalah yang belum diselesaikan dalam pemodelan kapasitas dalam industri pada masa ini adalah bagaimana untuk menghapuskan sambungan antara pemasangan dan kapasitas, supaya mengurangkan pengaruh pemasangan pada keputusan pemodelan. Dalam rancangan bekalan kuasa tradisional, induktor (kacang magnetik) sering digunakan untuk mengisolasi bekalan kuasa untuk mengurangi gangguan bunyi. Dalam rancangan sebenar, induktan izolasi (kacang magnetik) sering dibuang, dan bunyi bekalan kuasa dikurangi sebagai gantinya. Ini disebabkan resonansi induktor (bead magnetik) dengan komponen penapis lain. Untuk menghindari ini, perlu memmodelkan dan simulasikan induktan (kacang magnetik) untuk menghindari resonansi. Kaedah pemodelan induktansi yang biasa digunakan dalam industri juga menggunakan analisis rangkaian. Kaedah khusus adalah sama dengan model kapasitasi. Perbezaan ialah kaedah pemodelan induktansi (kacang magnetik) berada dalam mod siri, dan kaedah pemodelan kapasitasi berada dalam mod selari. Modelan peranti pasif diatas terutamanya digunakan dalam integriti isyarat dan integriti kuasa. Dalam tahun-tahun terakhir, analisis simulasi EMI sedang berkembang secara perlahan-lahan, dan model ujian peranti pasif EMI telah secara perlahan-lahan menjadi fokus desain antara sambungan. . Figure 1 menunjukkan lengkung impedance kondensator.

Ujian Integriti Kuasa

With the continuous increase of chip power and the continuous reduction of operating voltage, the noise of the power supply has gradually become the object of concern in interconnection design. Dari perspektif objek ujian, ujian integriti kuasa boleh dibahagi menjadi dua langkah, ujian karakteristik sistem kuasa dan ujian bunyi tanah kuasa. Yang pertama ialah ujian prestasi bahagian bekalan kuasa sistem (ujian pasif), yang kedua ialah ujian langsung bunyi tanah bekalan kuasa (ujian aktif) bila sistem berfungsi, dan bunyi penyukaran sinkronik juga boleh diklasifikasikan sebagai bunyi tanah bekalan kuasa. Apabila menguji prestasi sistem kuasa, penganalisis rangkaian biasanya digunakan, dan objek ujian adalah Impedance-Self dan Transfer-Impedance sistem kuasa. Dalam keadaan biasa, impedance sistem kuasa jauh lebih kecil daripada impedance sistem penganalisa rangkaian (50 ohms), jadi hanya perlu untuk melakukan kalibrasi lewat semasa ujian, dan impedance sistem kuasa boleh diperoleh dengan menggunakan formula S21=Z/25. Analisa spektrum dan oscilloscope boleh digunakan untuk menguji bunyi tanah bekalan kuasa. Port input penganalisis spektrum tidak dapat disambung ke komponen DC. Oleh itu, apabila menguji bunyi tanah bekalan kuasa, Penghalangan DC mesti disambung dalam siri dalam pemasangan ujian. Impedansi input bagi penganalisis spektrum adalah 50 ohms, dan impedance rangkaian kuasa-tanah secara umum pada aras miliohm, jadi pembentuk ujian tidak akan mempengaruhi sistem yang sedang diuji. Kaedah yang diterangkan di atas adalah untuk menguji bunyi tanah bekalan kuasa pada papan tunggal, dan bunyi tanah bekalan kuasa dalam cip adalah apa yang benar-benar mempengaruhi operasi cip. Pada masa ini, perlu menggunakan ujian bunyi penyukaran sinkronik untuk menentukan bunyi tanah bekalan kuasa dalam cip. Anggap cip mempunyai port N IO, salah satu daripada mereka disimpan statik, dan N-1 yang lain dipindahkan pada masa yang sama, dan bentuk gelombang isyarat pada rangkaian statik diuji, iaitu, bunyi penukaran sinkronik. Bunyi penyukaran sinkronik termasuk kedua-dua bunyi bekalan kuasa tanah dan percakapan salib antara isyarat berbeza dalam pakej. Tidak ada cara untuk membezakan kedua-dua.

perubahan impedance masukan Oscilloscope dengan tetapan

Dalam beberapa produk berakhir tinggi, kegelisahan telah secara perlahan-lahan menjadi indikator penting yang mempengaruhi prestasi produk. Di sini kita hanya memperkenalkan secara singkat bagaimana untuk menggunakan penganalisis spektrum untuk menguji isyarat jam kecemasan dan masalah penyelesaian masalah. Ujian gelisah isyarat data tidak ditutup untuk masa ini. Dalam kebanyakan sistem, jam dijana oleh oscilator kristal atau loop terkunci fasa. Ujian gelisah isyarat jam adalah relatif mudah dan tidak memerlukan alat ujian akhir tinggi. Masalahnya boleh ditemui dengan menggunakan penganalisis spektrum umum. Spektrum isyarat jam ideal adalah spektrum diskret bersih dengan komponen hanya pada darab frekuensi jam. Jika ada gelisah dalam isyarat jam, lob sisi akan muncul di sekitar pembilang ini, dan saiz gelisah adalah proporsional dengan kuasa lob sisi ini. Kaedah khusus untuk menggunakan penganalisis spektrum untuk menguji gelisah jam adalah untuk mencari mana-mana titik boleh diuji pada rantai isyarat jam, sambung isyarat pada titik ini ke penganalisis spektrum melalui Pengblokan DC, dan mengamati hasil ujian. Kerana pemasangan ujian adalah sistem linear, tidak perlu bimbang tentang menghasilkan komponen spektral baru. Seperti yang disebutkan di atas, jam semua dijana oleh oscilator kristal atau loop terkunci fasa. Dalam kes ini, sebab penting untuk memperkenalkan kegelisahan jam adalah bunyi bekalan kuasa bagi oscilator kristal atau loop terkunci fasa. Dengan menggunakan kaedah yang diterangkan di atas untuk menguji bunyi bekalan kuasa bagi oscilator kristal atau loop terkunci fasa yang dicapai, dan membandingkannya dengan lob sisi dalam spektrum jam, penyebab gelisah jam pada dasarnya boleh ditentukan. Penyelesaian untuk masalah adalah untuk mendesain semula sirkuit penapis bagi oscilator kristal loop terkunci fasa mengikut lob sisi spektrum jam. Secara umum, masalah ini boleh diselesaikan dengan memilih kondensator penapis secara rasional.

Kertas ini memperkenalkan objek ujian semasa dan kaedah ujian dalam medan desain sambungan. Bila kadar isyarat terus meningkat, kandungan ujian baru muncul, termasuk bunyi kuasa-ke-tanah, pemodelan peranti pasif, jitter, dan lebih. Penulis mencadangkan kaedah ujian untuk kandungan ujian baru ini berdasarkan pengalaman kerjanya sendiri. Dalam ujian bentuk gelombang isyarat tradisional, pertimbangan utama patut ialah mengurangi panjang wayar tanah untuk menghindari sambungan babi ke bunyi dan mengurangi ketepatan ujian. Dalam rancangan sambungan masa depan, kerana meningkat frekuensi operasi isyarat, fokus kerja akan bergerak ke pakej cip, and related testing and modeling techniques will become the focus of work on Papan PCB.