Semasa industri komputer bergerak ke penukar DC-DC yang mampu menyediakan hingga 200A pada 1V, Papan PCB teknik bentangan perlu memenuhi keperluan penukar yang menantang ini. Untuk membandingkan kesan pelbagai cacat kawat, kita fokus pada kesan induksi parasit dalam sirkuit, terutama yang berkaitan dengan sumber, drain, dan pintu menukar MOSFET. Kami bina Papan PCB untuk menguji penyukar DC-DC yang mengambil 12V DC dan menukarnya ke 1.3V dan output hingga 20A. Kami menggunakan papan pemalam untuk pemasangan dan boleh mengubah induktan pada setiap elektrod MOSFET secara individu atau secara bersamaan pada bila-bila masa. Kami memilih untuk menggunakan nilai induktan sebagai peratus dari induktan keseluruhan papan yang direka khusus 2 inci, daripada nilai sebenar kerana orang kabel hanya tahu panjang jejak tertentu dan tidak perlu nilai induktannya.

Cipta ujian

Kami menggunakan efisiensi penukar untuk mengukur efisiensi induksi parasit ini. Ini kerana efisiensi adalah ukuran piawai prestasi penyukar DC-DC. Ujian dibahagi ke bahagian berikut: Laras koeficien proporsional bagi setiap nilai induktan pembuangan MOSFET, sumber, dan gerbang, dan perhatikan kesan pada penyesuaian sinkroni dengan mengukur efisiensi konversi. Melalui kombinasi kedua-duanya di atas, untuk memahami hubungan antara mereka. Papan ujian induktansi mempunyai induktansi 43nH dan biasanya ditetapkan kepada 0%, 25%, 50%, dan 100%. Dalam eksperimen kami, resistensi parasit pada papan ujian induktan mempunyai sedikit kesan dan boleh diabaikan. Oleh kerana kesan memadamkan induksi parasit bergantung pada frekuensi, kami eksperimen pada tiga frekuensi penukaran preset: 300kHz, 600kHz, dan 1MHz. Ini membolehkan kita melihat betapa pentingnya rancangan untuk bergerak dari frekuensi menukar biasa ke frekuensi yang lebih tinggi di masa depan. Kita semua tahu bahawa dalam sirkuit kuasa, panjang semua jejak mesti disimpan singkat untuk menghindari tekanan dan bunyi semasa, mengurangi EMI keseluruhan papan, dan menghindari mempengaruhi negatif komponen "lebih stabil" dalam sirkuit (terutama untuk sirkuit kawalan analog dan komponen berkaitan). Selain itu, bahan rujukan menunjukkan bahawa induktan sumber kawalan MOSFET mempunyai kesan bukan-linear pada peningkatan masa jatuh sumber semasa, yang mengakibatkan penyebaran kuasa yang lebih tinggi dan lebih rendah efisiensi konversi. Selain fenomena di atas, induksi sumber juga boleh menyebabkan bunyi pada nod tukar.

Sirkuit ujian dan papan sirkuit

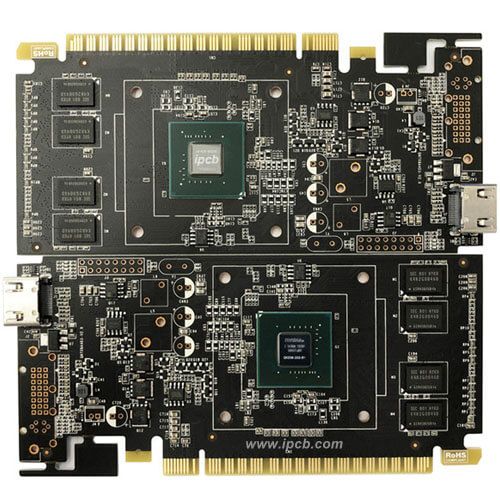

Sirkuit yang digunakan adalah topologi penyesuaian sinkronik yang berfungsi dalam loop terbuka. Ini untuk mengeluarkan mana-mana kesan gelung kawalan mungkin mempunyai pada prestasi sirkuit dan membolehkan kita fokus pada efisiensi penukaran kuasa, terutama prestasi MOSFET. Kami tahu bahawa keadaan induksi tinggi boleh menyebabkan bunyi yang berat, terutama pada nod tukar. Pilih ICs pemacu pintu yang boleh tolak bunyi ini tanpa kesan negatif. Papan sirkuit empat lapisan ini menggunakan dua ons bahan tembaga, dan dua lapisan dalam adalah pesawat tanah dan kuasa. Semua peraturan kabel yang baik perlu diperhatikan apabila kabel.

Kesan induksi gerbang

Induktan gerbang mempunyai sedikit kesan pada efisiensi pada frekuensi tukar 300kHz. Pada frekuensi perubahan 600kHz, kesan induksi gerbang jauh lebih kuat, dengan perubahan 1.2% dalam efisiensi pada 20A. Pada 1MHz, kerosakan efisiensi hampir sepenuhnya hilang. Kita belum menyelidiki sebab ini dan boleh menebak bahawa terdapat 50% kemungkinan faktor resonansi akan offset kehilangan. Fenomen resonansi pemacu gerbang MOSFET patut diselesaikan lebih lanjut. Kami memperhatikan bahawa induksi gerbang mempunyai sedikit kesan pada efisiensi kawalan dan MOSFET sinkronis.

Kesan induksi sumber

Induktan sumber mempunyai kesan yang lebih kuat pada efisiensi. Dalam beberapa kes, kita perlu batalkan ujian sebelum mencapai semasa kerana suhu MOSFET lebih besar dari 130°C. Gambar 5 menunjukkan hasil kajian MOSFET kawalan. Pemeriksaan lebih dekat keputusan ini menunjukkan bahawa pada frekuensi 300kHz dan inductans 100%, penyukar DC-DC tidak boleh beroperasi di 20A penuh kerana suhu MOSFET melebihi 130°C. Hal yang sama boleh ditemui pada 50% induktan, 600kHz, dan 1MHz. Penghancuran efisiensi disebabkan induksi sumber diperhatikan lebih berat daripada tanpa induksi sumber. Apabila induktan adalah 50% dan semasa adalah 15A, efisiensi dikurangi dengan 7% walaupun pada frekuensi tukar 300 kHz. Apabila induktan adalah 100%, efisiensi bertambah kepada 11%. Pada pertukaran frekuensi 600kHz dan 1MHz, kesan lebih kuat dan penghancuran efisiensi lebih berat daripada tanpa induksi sumber. Jelas, walaupun induksi sumber rendah mengurangkan efisiensi, terutama untuk menukar frekuensi ⥠600kHz.

Kesan Penginduksi Lukisan

Induktansi drain boleh menyebabkan bunyi yang berat yang mungkin cukup untuk menyebabkan MOSFET pecah dalam keadaan ekstrim (Figure 3). Ia juga mempengaruhi keefektivitas. Efisiensi adalah fungsi bagi induksi semasa muatan dan pembuangan pada frekuensi yang berbeza. Selain itu, keputusan berikut boleh dilihat: apabila semasa adalah 15A, pada 300kHz dan 50% inductans, kita perlu batalkan ujian kerana suhu MOSFET melebihi 130' Pada frekuensi yang sama, 100% induktan, kita tidak dapat mendapat apa-apa bacaan kerana cincin terlalu berat. At 300kHz, 12A, 50% of the drain inductance is 7% less efficient than 0%. Kerana suhu MOSFET tinggi, ujian tidak boleh dilakukan di atas 15A. Pada 600kHz, 12.5A, 50% indunsi pembuangan adalah 8.5% kurang efisien daripada 0%. Kerana suhu MOSFET terlalu tinggi, ujian tidak boleh dilakukan di atas 12.5A. Pada 1MHz, ujian tidak boleh dilakukan di atas 5A kerana suhu tinggi MOSFET.

Kesan induksi sumber-gerbang

Induktan sumber yang lebih besar akan mengurangi efisiensi secara signifikan. Tergantung dasar efisiensi pada induktan gerbang telah dipaparkan. Apabila digabungkan dengan induksi sumber kecil, gambar keseluruhan menjadi cukup jelas - induksi gerbang yang lebih besar mesti mengakibatkan kehilangan kuasa yang lebih besar. Penjelasan hasil ini memerlukan kajian lanjut. Sekarang kita boleh menyatakan bahawa, dalam nilai induksi yang masuk akal untuk papan, induksi saluran dan sumber mesti dikurangkan untuk memastikan efisiensi penukar tinggi. Simulasi memberikan keputusan berikut: Pintu dan sumber induktan resonan dengan kapasitasi sumber-gerbang MOSFET. Apabila HS-FET mematikan sumber gerbang, kondensator melepaskan melalui laluan induktif ini. Selepas MOSFET dimatikan, induktan akan memaksa arus gerbang untuk terus mengalir dan memuat balik kapasitasi sumber gerbang. Muatan ini akan melepaskan semula dengan cara yang sama dan membalikkan tekanan sumber-gerbang HS-FET. Bergantung pada dip, HS-FET boleh menyala lagi dengan sirkuit pendek besar. Kesan menjadi berat pada induksi gerbang yang tinggi. Dalam beberapa kes, walaupun kesan sirkuit pendek kedua boleh dilihat. As part of this resonant circuit, the source inductance can also act in a second way. Apabila semasa sirkuit pendek berlaku, inductans sumber mengatasi di/dt (kadar perubahan semasa melalui masa) semasa sirkuit pendek, dengan itu mengatasi kehilangan. Induktan sumber juga menyebabkan balas balik negatif kepada tekanan sumber-gerbang dan hadapi sirkuit pendek. Kesan ini terutama berlaku di mana induksi gerbang parasit tinggi. Untuk efisiensi tinggi, kesan ini patut dihindari oleh rancangan, iaitu, induksi pintu mesti direka dengan hati-hati untuk mengurangkannya.

Kesan Sumber HS - Sumber LS inductance

We investigated the effect of the location of the parasitic source inductance on the efficiency. Sebagai hasilnya, FET kawalan akan mempunyai kesan yang lebih besar pada efisiensinya daripada FET sinkronis dalam jumlah yang sama gelung induksi sumber parasit. Sebab fenomena ini ialah FET kawalan penukaran perlahan menyebabkan kerugian penukaran tambahan kerana VDS kawalan FET lebih tinggi daripada FET sinkronis (jatuh tegangan maju FET sinkronis adalah kecil) semasa proses penukaran. Selain itu, balas balik dari induksi parasitik kepada tekanan pembuangan gerbang FET mempunyai kesan yang signifikan pada semasa kebocoran HS-FET. Dengan perbandingan, kesan induksi sumber parasitik pada arus kebocoran LS-FET hanya sebahagian, kerana ia boleh dilewati oleh diod badan FET sinkronis.

Kesan MOSFET Paralel

Apabila MOSFET disambung secara selari, tidak mungkin setiap gelung MOSFET individu akan mempunyai parasit yang sama dalam banyak kes. Kami telah menyelidiki kesan induksi tambahan dalam gelung pembuangan MOSFET pada efisiensi. Kami secara eksperimen menunjukkan kesan kerosakan dari induksi parasit pada efisiensi menukar MOSFET dalam penyukar DC-DC. Kesimpulan adalah seperti ini: kesan induktan dalam sirkuit sumber adalah berat, diikuti oleh induktan yang sama dalam sirkuit pembuangan. Dalam papan roti kami, kami tidak jumpa kesan serius berkaitan dengan induksi sirkuit gerbang. Pengurangan efisiensi berkaitan dengan frekuensi penukaran penukar. Pengurangan efisiensi mempunyai banyak kaitan dengan semasa muatan. Dalam kehadiran induksi parasit dalam sumber dan sirkuit pembuangan, semakin besar muatan semasa, semakin besar penurunan efisiensi. Dalam aplikasi penukar DC-DC hari ini, perlindungan istimewa mesti diambil bila menjalankan sistem kuasa PCB, terutama sekitar menukar MOSFET. Salah satu keuntungan menggunakan papan berbilang lapisan adalah untuk mengurangi resistensi parasitik dan induktan dengan tenggelam sebanyak mungkin semasa dalam lapisan. Ini mengurangkan kerugian dan kerugian resisten disebabkan induksi parasit. Bila merancang penyukar DC-DC frekuensi tinggi, terdapat banyak masalah induksi parasit yang berkaitan dengan sumber dan sirkuit pembuangan. Pertama adalah induksi pakej, dan ia boleh digunakan pakej induktan rendah yang diperkenalkan baru-baru ini untuk menukar MOSFET. Item kedua adalah induktan parasit Papan PCB, yang mesti dikawal dengan menggunakan lapisan berbilang Papan PCB dan mengurangi induksi jejak. Ini membenarkan perancang menggunakan kurang kondensator untuk balas dinamik yang lebih cepat dan rancangan frekuensi tinggi yang berjaya. Induktansi parasitik yang tidak dapat dihindari oleh rancangan patut dipindahkan ke dalam loop FET sinkronik kerana induktan dalam FET sinkronik mempunyai sedikit kesan pada efisiensi umum daripada induktan dalam loop FET kawalan. Perhatian: Pada siklus tugas rendah, resistensi parasitik dalam gelung FET sinkronik boleh mengurangi efisiensi secara signifikan. Complex trade-offs need to be made in the design (trace width, tebal tembaga, julat loop efektif, biasing, dll.). Lupakan MOSFET selari. Cara untuk menggantikan MOSFET secara selari adalah menambah tahap tambahan atau menggunakan MOSFET yang lebih baik. If paralleling is unavoidable, untuk MOSFET selari, simetri elektrik mesti dijamin dalam rancangan untuk mendapatkan distribusi semasa yang sama dan masa penukaran yang sama pada Papan PCB.