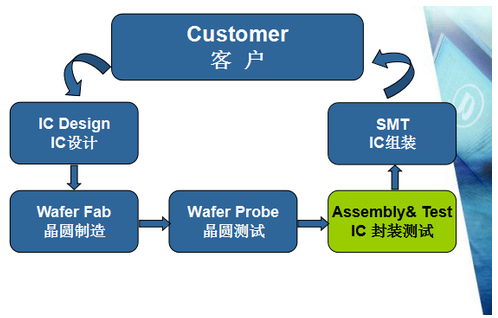

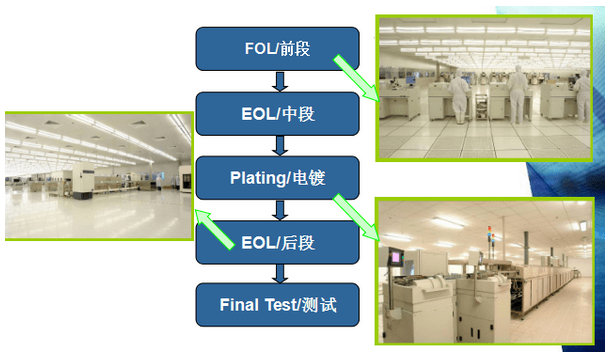

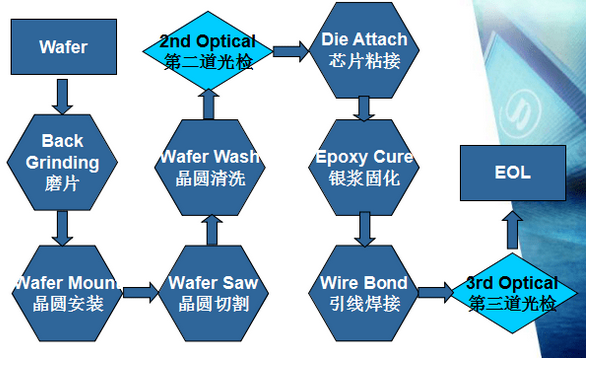

IC çip paketleme ve testi süreci:

İşlemComment

IC Paketi Paketi Paket vücudunun farklı şekilleri ile oluşturduğu çep (öl) ve farklı çerçeve (L/F) ve plastik mühürleme maddeleri (EMC) tarafından anlatır.

Bir sürü tür IC Paketi var, bu şekilde klasifik edilebilir:

Paketleme materyallerine göre, bölünebilir:

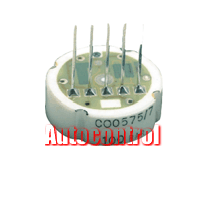

Metal paketi, keramik paketi, plastik paketi

Metal paketleme genellikle askeri veya aerospace teknolojisinde kullanılır, ticari ürünler yok;

Keramik paketleme metal paketlemesinden daha iyi, askeri ürünlerde kullanılan, küçük bir miktar ticari pazarı;

Kullanıcı elektronikleri için plastik paketleme, düşük maliyeti, basit süreç, yüksek güvenilir ve pazar payısının büyük çoğunu alır;

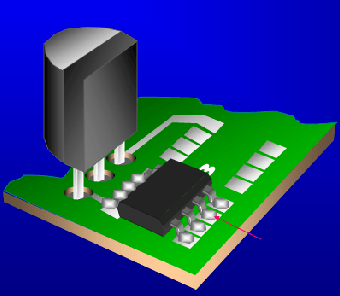

PCB tahtasıyla bağlantı moduna göre, bölünebilir:

PTH paketi ve SMT paketi

PTH-Pin Through Hole;

SMT-Yüzey Dağ Teknolojisi.Şu anda bazardaki çoğu IC SMT türü için kabul edilir.

Paket görünüşüne göre, bölünebilir:

SOT, SOIC, TSSOP, QFN, QFP, BGA, CSP, etc.

İki anahtar faktörü kapsülleme şeklini belirliyor:

Etkilendirme etkinliği. 1:1'e yakın olduğu kadar Chip alanı/paket alanı;

Pin numarası. Daha fazla pinler, daha gelişmiş, ama sürecin zorlukları da bu şekilde artıyor;

Aralarında, CSP, Flip Chip teknolojisi ve sade Chip paketi kullanılmasına neden, Chip alanı/paket alanı =1:1, şu anda en gelişmiş teknolojidir.

QFN -- Quad Flat No-lead Paket QFN -- Quad Flat No-lead Paket

SOIC - Küçük Dışarı Çizgi IC Paketi

TSSOP - Küçük Küçük Dışarı Paketi

QFP - Quad Flat Paket

BGA - Ball Grid Array Paketi

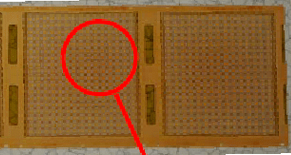

CSP - Chip Scale Paket Chip Scale Paketi

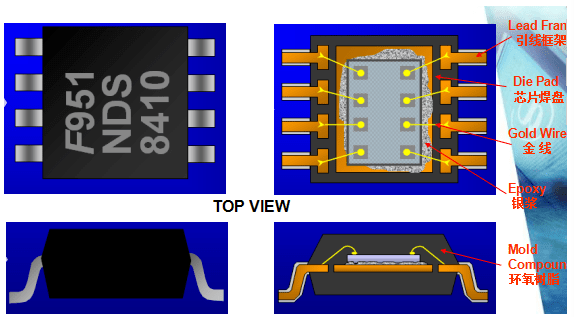

IC Paket Yapısı

Görüntülerindeki Zehirli Materiyal

Çerçeve

devre bağlantısını sağlar ve ölüm ayarlamasını sağlar;

Ana materyal gümüş ve NiPdAu'yla takılacak bakar.

L/F süreci Etch ve Stamp içeriyor;

Oksidik yapmak kolay, nitrogen kabinetinde saklanmış, yoğunluğu %40'den az;

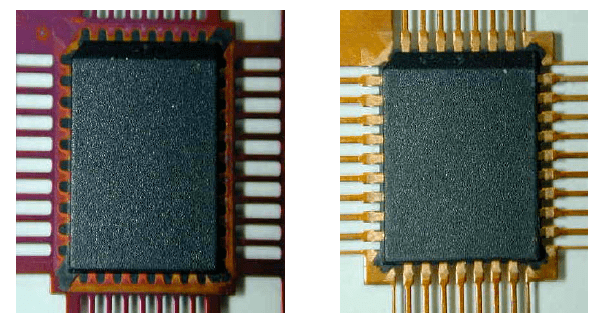

BGA ve CSP hariç, diğer paketler "Lead Frame" kullanacak, BGA "Substrate" kullanacak.

Çeviri:

Çip ve dış ön çerçevesi arasındaki elektrik ve fizik bağlantısını fark etmek için;

Altın ipleri %99.99 yüksek temizlik altındır;

Aynı zamanda, maliyetli düşünceler yüzünden bakra kablo ve aluminium kablo süreçleri şu anda kullanılır. Önemli olan maliyetin azaltılması ve süreç zorlukları arttırılması ve yiyecek azaltılması.

Elektrik diametri yönetici akışını belirliyor; 0.8mil, 1.0mil, 1.3mil, 1.5mil ve 2.0mil;

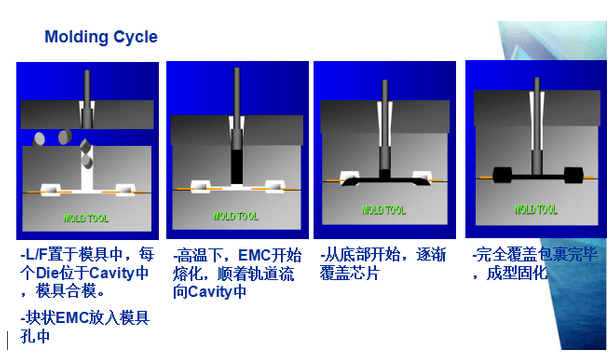

Mold Birleşik/epoksi resin'in en önemli komponentleri: epoksi resin ve çeşitli bağımlıklar (kurma ajanı, değiştirici, Mold striptişim ajanı, ölüm ajanı, yangın retardant ı ajanı, etc.);

Ana fonksiyonlar şu şekilde: Ölüm ve Yönetim Çerçevesi fiziksel ve elektrik korumasını sağlamak ve dış araştırmalarını engellemek için erimiş durumda sıkıştırılır;

depo koşulları: 0° altında, normal sıcaklığın altında 24 saat;

Çeviri:

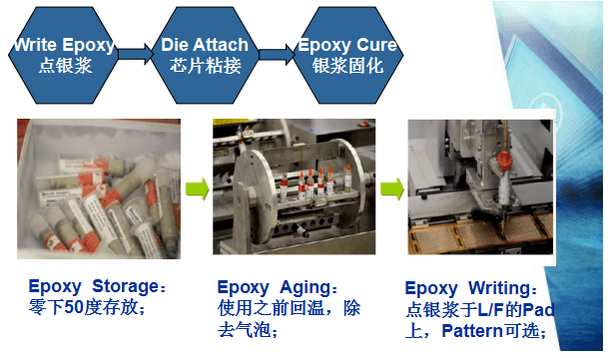

Epoxy resin dolu metal pulu (Ag); Üç fonksiyonu var: Ölüm Pad üzerinde ölümü ayarlamak; Sıcak patlama, yönetici etkisi;

-50° depo altında, 24 saat önce geri sıcaklığı kullanmadan önce;

FOL- Sınır önü

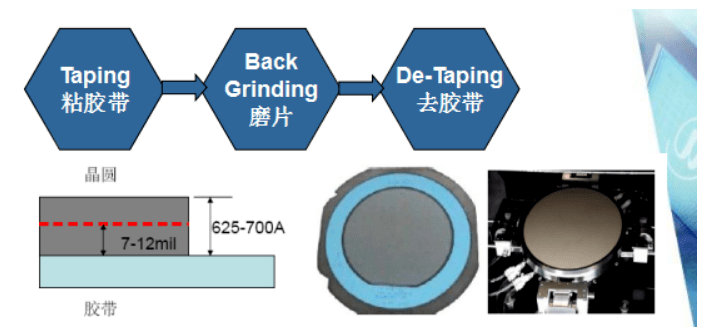

FOL- Geri Grinding

Wafer fabrikasındaki Wafer'ın yığını, paketlemek için gereken Wafer kalıntısını azaltmak için arka tarafta yerleştirir.

Sıçarken, devri korumak ve arkayı aynı anda sarmak için aktif bölgeye kaset koymak gerekiyor. Kaydıktan sonra kaseti çıkarın ve kalınlığı ölçün.

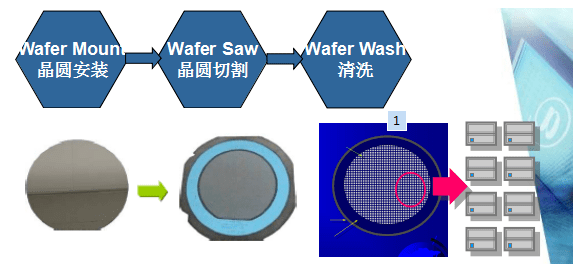

FOL â147; Wafer Saw

Mavi bir film üzerine dağdırılır ki, a çıldıktan sonra bile ayrılmaz.

Bütün Wafer'ı Saw Blade'dan bağımsız Dice'e kesin. Ölüm Attach ve diğer süreci arkasında kolaylaştırmak için.

Saw tarafından yapılan toz temizleyip Wafer'i temizleyin.

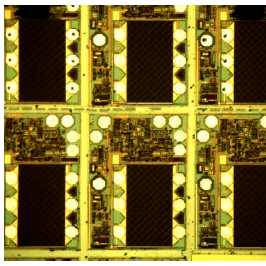

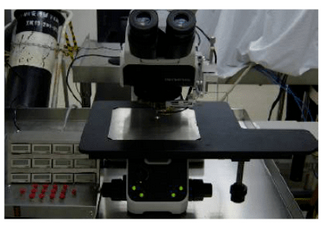

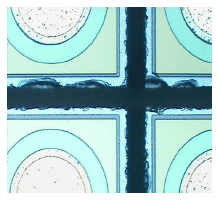

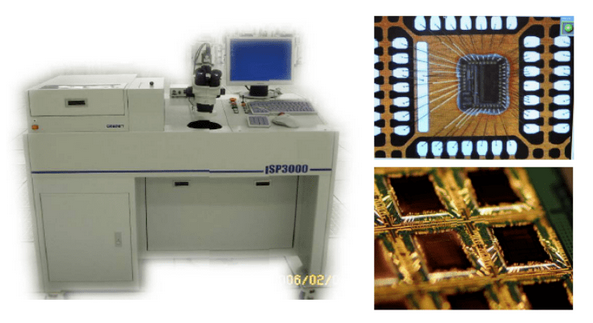

FOL -- 2. Optik Denetim

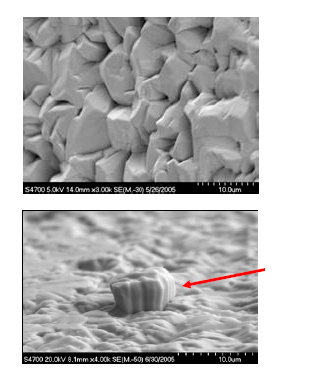

Ana amaç Wafer Saw'ın mikroskop altında görünüşünü kontrol etmek, bir kaybın olup olmadığını görmek için.

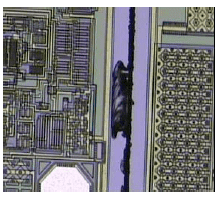

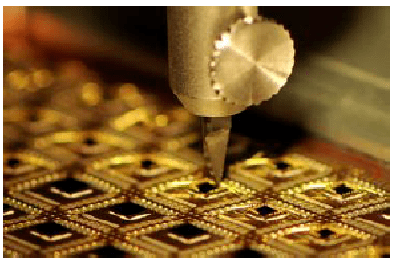

FOL â147; Öl Attach

Chip seçim süreci:

1. Müfettiş Pin, Mylar'dan çip çantasını dağıtıp mavi filmden uzaklaştırmak kolaylaştırdı;

2.Chip, Wafer'dan L/F'ye kadar taşıma sürecini tamamlamak için yukarıdan alınıyor;

3. L/F Pad'deki çip bağını gümüş pastasıyla bir güç ile toplayın ve özel pozisyon kontrol edilebilir;

4, Bond Head Resolution: x-0.2um; . Y - 0.5. Z - 1.25 um;

5. Bond Head Speed: 1.3m/s;

FOL â147; Epoxy Cure

175ÂC, 1 saat; Oksidasyonu engellemek için N2 ortamı:

Öl Attach kalitesi kontrolü:

Ölün

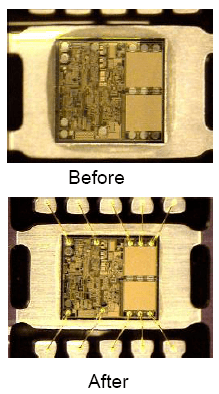

FOL â147; Kablo Bağlantısı

Yüksek temizlik altın (Au), bakar (Cu) ya da aluminium (Al) kabloları, Pad ve Lead'i araştırmak için kullanılır. Pad, çip üzerindeki devre dışındaki bağlantı noktasıdır, ve Lead, Lead Frame üzerindeki bağlantı noktasıdır.

W/B paketleme sürecinin en kritik sürecidir.

FOL â147; 3. Optik Denetim

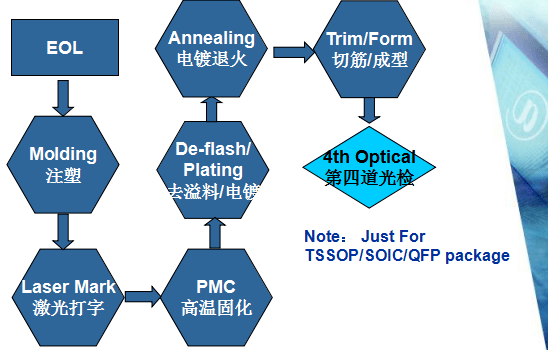

EOL â147; Hat Sonu

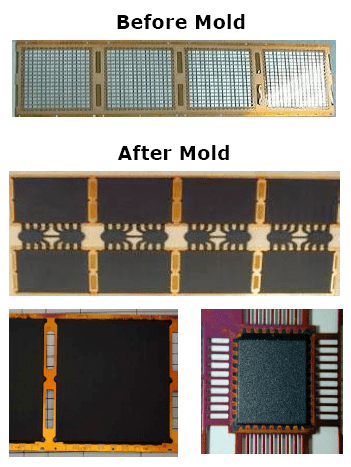

EOL â147; Molding

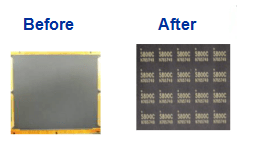

EOL â147; Laser Markamount in units (real)

Laser önde ya da Paket arkasına yazıyor. İçindeki içerikler: üretim adı, üretim tarihi, üretim toplamı, benzer.

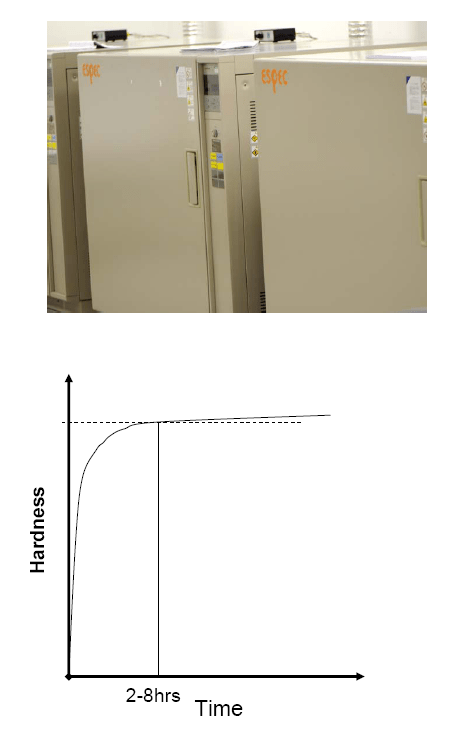

EOL â147; Mold Cure Post

Molding'in içi yapısını korumak ve iç stresimi yok etmek için plastikleri korumak için kullanılır. Cure Temp: 175 + / - 5 ° C; Cure Time: 8 HRS

EOL â147; Çeviri

Mevzu: de-Flash'ın amacı, Molding'tan sonra tüp vücudunun etrafındaki ipleri arasında fazla molding kaldırmak. Yöntemler: Zayıf asit ile soğuk ve yüksek basınç suyla yıkamak.

EOL â147; Plating

Metalim ve kimyasal metodları kullanarak, dış çevrenin etkilerini (ısı ve ısı) engellemek için Leadframe yüzeyine bir kaput uygulanır. Ve PCB kurulundaki komponentleri güzelleştirmek ve elektrik hareketi geliştirmek kolaylaştırmak.

Genelde iki tür elektro plating var:

Pb özgür: soğuk elektroplatın kullanılması, > yüksek temizlik Tin (Tin) yüzde 99,95'dir, şimdiki geniş kullanılan teknoloji için, RoHS ihtiyaçlarına uygun;

Bu bir kalın s a ğlığı. Küçük %85 hesaplar ve Yönetim %15 hesaplar. Çünkü RoHS'e uymuyor, basit olarak şu anda yok ediliyor.

EOL â147; Annealing Bake'den sonra

Görev: Bir süre boyunca önümüzdeki elektroplatıcıdan sonra ürünü yüksek sıcaklıkta pişirmeye izin verin, elektroplatıcının potansiyel Whisker büyüme problemini yok etmek için; Şartı: 150 + / - 5 - c; 2Hrs;

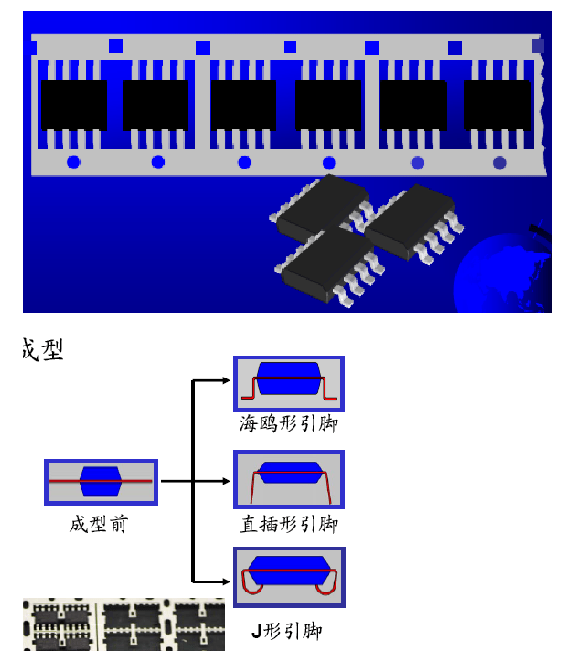

Bir parçanın ön çerçevesini birer birimlere (IC) kesmesi süreci; Form: Trim'den sonra IC ürünü biçimleyin, süreç için gereken şekilde ulaşın ve Tübe ya da Tray'e koyun;

EOL â147; Son Görsel Müfettiş

Ürünün görünüşünü düşük güçlü bir camın altında inceleyin.

5. EOL sürecinden oluşan potansiyel kaybı ürünlerine dikkat edin, Molding defekleri, platlama defekleri, Trim/Form defekleri gibi.