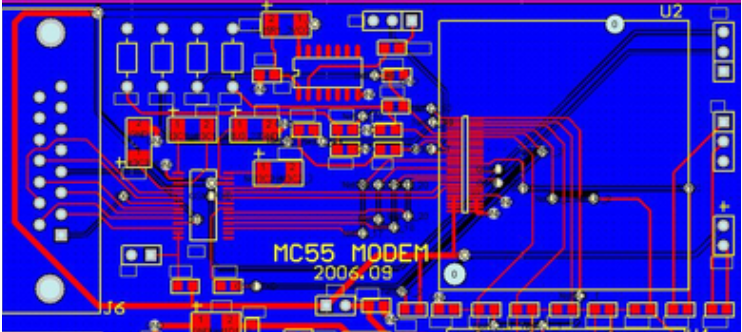

Los principios básicos del cableado de PCB del Circuito de reloj y los requisitos generales del cableado del Circuito de reloj son los siguientes.

1. debido a que la línea de reloj es uno de los factores que más afecta a emc, el paso por la línea de reloj debe ser menor; Trate de evitar correr en paralelo con otras líneas de señal y mantenerse alejado de las líneas de señal generales para evitar interferir con las líneas de señal.

2. evite la fuente de alimentación en el tablero de PCB para evitar que la fuente de alimentación y el reloj interfieran entre sí.

3. cuando se utilizan varios relojes de diferentes frecuencias en una placa de circuito, dos líneas de reloj de diferentes frecuencias no pueden funcionar lado a lado. La estructura del Circuito de la red de distribución [9] se muestra en la figura 8 - 6. El circuito utiliza una sola fuente de reloj de tiempo y distribuye la señal del reloj a n destinos remotos a través de un amortiguador de accionamiento.

La red de distribución de relojes en forma de araña siempre se puede distribuir. Una red de distribución de relojes en forma de araña debe prestar atención a los siguientes puntos.

1. la carga total del circuito amortiguador de conducción es R / N. Por ejemplo, cuando se utilizan líneas de transmisión de 50 islas, es decir, redes de arañas de dos patas, la carga total en el extremo de la unidad es de 25 islas. No hay muchos dispositivos de amortiguación de accionamiento capaces de conducir una carga tan baja.

2. para impulsar más "patas de araña", se necesita una unidad de reloj más potente. Una forma sencilla es conectar las salidas de dos o más unidades en paralelo para formar una unidad de alta potencia.

3. la Potencia total de conducción necesaria para la señal de reloj del circuito ttl es 25 veces mayor que la del circuito ecl.

La red de distribución de relojes con estructura de rama tiene una estructura de circuito de la red de distribución de relojes con estructura de rama [9]. El circuito utiliza una sola fuente de reloj de tiempo y asigna la señal del reloj a n entradas en forma de rama a través de un amortiguador de accionamiento y una línea de distribución de reloj de baja resistencia. En ese momento, cuando la señal del reloj pasa por cada entrada, su tiempo de subida se estira y también se generan pequeños pulsos reflejados para propagarse de vuelta a la fuente a lo largo de la línea. El pulso reflejado es la derivada de la señal de entrada, que interfiere con la recepción. Para reducir la amplitud del pulso reflejado, se pueden utilizar los siguientes métodos.

1. reducir la velocidad de ascenso del conductor, lo que puede reducir la amplitud del pulso reflejado. La velocidad del conductor utilizado puede cumplir con los requisitos de desviación del reloj.

2. reducir la capacidad de cada rama. En un bus multirama, el capacitor de rama está relacionado con el capacitor de entrada del receptor del reloj, el capacitor parasitario del conector y el capacitor que conecta el rastro de PCB del receptor del reloj.

3. reducir la resistencia característica (zo) de la línea de distribución del reloj. La resistencia característica de la línea de distribución del reloj está relacionada con su geometría. La sensibilidad de la línea de reloj de 50 islas es 2,5 veces mayor que la del capacitor de la rama de reloj de 20 islas. Reducir la resistencia de distribución ayuda a evitar que la deriva del reloj se vea afectada por cambios de carga.

La estructura de terminación de fuente que utiliza múltiples líneas de reloj es un circuito que utiliza un solo conductor de reloj para conducir dos terminaciones de fuente [9. La resistencia del Circuito de terminación de la fuente es el doble de la resistencia del Circuito de terminación y la corriente de conducción necesaria cae a cero después de 2t (t es el retraso de propagación), lo que reduce el consumo promedio de energía. Una es utilizar una sola unidad de reloj para conducir dos fuentes y usar varias líneas de reloj. La estructura de conexión del extremo de la fuente requiere que la longitud de la línea sea igual para garantizar que el pulso reflejado llegue al mismo tiempo; La carga en cada extremo debe ser igual para garantizar que el pulso reflejado tenga la misma forma de onda. La resistencia del terminal del extremo de la fuente está relacionada con la resistencia de salida del conductor. La resistencia del extremo de la fuente es rs, es decir, la resistencia del extremo de la fuente (isla); Zo es la resistencia de la línea a conducir (isla); Conducir es la resistencia de salida efectiva (isla) del conductor; N es el número de líneas impulsadas. Hay que tener en cuenta que en la ingeniería real, la simetría completa es difícil de lograr. Si hay asimetrías en la línea, los reflejos y comentarios de cada línea no se pueden compensar completamente, lo que provocará que el sistema suene. Protección Especial de conversación cruzada de la línea del reloj.