Tecnología de interconexión de chips de encapsulamiento de circuitos integrados de alto rendimiento y alta fiabilidad

Dirección de desarrollo del mercado de componentes electrónicos (para componentes de placas de circuito impreso pcba)

Para las tecnologías maduras de LSI con mayor integración y velocidad, es necesario desarrollar tecnologías de aislamiento que utilicen materiales de baja k según corresponda. Pero para satisfacer el alto rendimiento de estas unidades, debido a la estructura poroso y multicapa, la capa de aislamiento se ha vuelto cada vez más delgada. Como resultado, el LSI se volvió frágil. Por otro lado, para cumplir con los requisitos de alta velocidad, la corriente del LSI está aumentando. Además del tamaño del chip de grande a pequeño, la densidad térmica y el consumo de energía también están aumentando. Por lo tanto, para los futuros sustratos de encapsulamiento de semiconductores (encapsulamiento de sustratos ic), es necesario resolver estos problemas, a saber, la fragilidad, el Alto calor, la alta velocidad y el bajo costo de los medios intercalares. El futuro preestablecido del proceso de semiconductores será de 20 nm o menos, lo que será mucho más débil.

Tecnología de encapsulamiento necesaria para la generación de 20 nm

Las especificaciones necesarias para la próxima generación de 20 nm son:

Bajo estrés en la capa k baja frágil

Radiación térmica alta 5w adecuada para LSI de alto rendimiento

Alta velocidad de 10 GHz para lograr altas funciones

Dirección de desarrollo de los envases de semiconductores

Para adaptarse al crecimiento funcional y la reducción de costos de los dispositivos eléctricos, incluidos los dispositivos móviles, las reglas de preestablecimiento de obleas se están desarrollando hacia reglas de preestablecimiento más grandes y finas. Para ello, para reducir costos, la tecnología de encapsulamiento de semiconductores está cambiando rápidamente de la tecnología de Unión de alambre de oro más estándar a la Unión de alambre de cobre, lo que reduce el uso de oro. Además, el uso de la tecnología de Unión de chips invertidos satisface en gran medida la mayor integración y rendimiento del lsi. En 2010, la Unión de chips invertidos representó el 15% de la tecnología global de encapsulamiento de semiconductores y la Unión de cables representó el 85%. Para 2015, se espera que la participación de la Unión de chips invertidos alcance el 25%, y se espera que la proporción de la Unión de cables alcance el 75%. Especialmente para LSI de alta integración y alto rendimiento que requieren alta radiación térmica y alta velocidad de señal, la tecnología de Unión de chips invertidos se está considerando activamente como adecuada.

Tecnología de chips invertidos de sentido común

Adecuado para k bajo

Tecnología común de chips invertidos:

. soldadura de lados adyacentes, la estructura principal es C4 (diseño colaborativo de chip de asentamiento controlable)

. para cribados de au y tipo ACF

Unión ultrasónica de firmas au - au

La Unión a presión y la Unión ultrasónica aplican alta presión y oscilaciones mecánicas al lsi, por lo que estos métodos no se pueden utilizar en el LSI de bajo K. De esta forma, en el citado método se puede utilizar adecuadamente el C4 y, debido a la comparación de los tres métodos, la combinación es consistente con el hecho de que el C4 es el menos dañino para el chip.

La tecnología C4 nació a principios de la década de 1940 para computadoras universales y se ha utilizado. A medida que aumenta el número de chips de baja k, el C4 se utiliza para baja k reemplazando la estructura, el material y las mejoras del ubm.

Las protuberancias de columna de cobre desarrolladas recientemente (aproximadamente similares a los avances de c4) se aplican a almohadillas en línea o superpuestas y no a chips de baja K. Según los informes, debido al alto módulo de elasticidad de cobre (130gpa), el encapsulamiento de la estructura de la columna de cobre puede dañar la capa k baja. El desajuste del coeficiente de expansión térmica (cte) es el factor de aceleración.

Además, se consideró adecuado el alto módulo de elasticidad (50 gpa) de la Unión de metal fundido y el flujo después del uso inicial del flujo por la tecnología c4, por lo que durante la Unión e instalación de la placa madre, debido a las diferencias en la expansión térmica, se agregó al LSI la cantidad de tensión. Por lo tanto, la tecnología C4 no se puede utilizar en el futuro lsi, que es mucho más débil.

Radiación térmica

Hasta ahora, los sustratos orgánicos se han utilizado para encapsular chips invertidos. La conductividad térmica del sustrato orgánico es pequeña, 0,5w / mk, y es difícil de aplicar a un LSI con alto consumo de energía. Si se añade un sistema de enfriamiento o enfriamiento para mejorar la radiación térmica, aumentará el costo del encapsulamiento, el tamaño y la altura del plano o la superficie.

De hecho, debido a la baja radiación térmica, un punto del LSI limita su potencial y, por lo tanto, no genera mucho calor. Además, debido a la mala radiación térmica, la temperatura de unión aumenta y la corriente de fuga aumenta, lo que aumenta aún más el consumo de energía, y el aumento del consumo de energía aumenta la temperatura. Este es un círculo vicioso peligroso. Por lo tanto, mejorar la radiación térmica es un problema estrechamente relacionado.

Alta velocidad de la señal

La capa central del sustrato orgánico tiene una alta pérdida de daño dieléctrico (0,02) y una alta resistencia (t / h) del agujero a través de la capa central. Como resultado, la pérdida de lesiones por inserción en el rango de alta frecuencia es alta. Sin embargo, el uso de sustratos sin núcleo con el mismo material que los sustratos orgánicos tradicionales no es la solución fundamental. Además, los materiales de capa compuesta pueden ser diversos, por lo que es más difícil para los usuarios elegir el mejor material, y todo el requisito preestablecido debe considerar el rendimiento de alta velocidad.

Debido a que el sustrato es muy delgado, es necesario reemplazar una serie de instalaciones. Esto se convierte en un obstáculo para la producción. Debido a este problema, el traslado a un sustrato sin núcleo es de alto riesgo y solo se aplica a productos localizados.

La tecnología tradicional es difícil de satisfacer las necesidades de la próxima generación de 20 nm. Por lo tanto, es necesario desarrollar nuevos envases de semiconductores con nuevas tecnologías básicas.

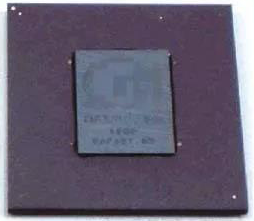

Tipo de monsterpac y puntos clave del proceso

El monsterpac tipec se ha desarrollado para satisfacer el proceso de 20 nm al que la tecnología de encapsulamiento tradicional es difícil de adaptar. Esto es completamente diferente del proceso y la estructura de embalaje tradicionales.

Estructura de encapsulamiento

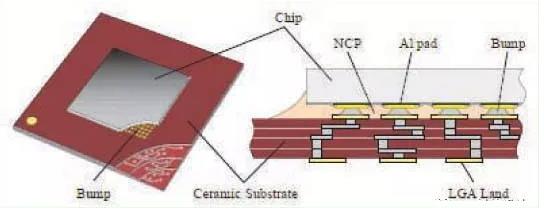

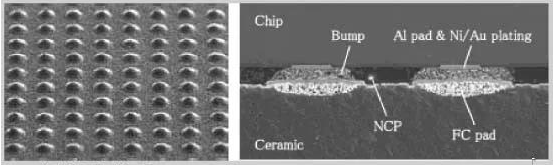

Nuestra estructura de encapsulamiento, el sustrato es cerámica, el Chip Semiconductor con inversión de protuberancias, el chip y el sustrato complementan NCP (pasta no conductora). No está moldeado con gas Epóxido o resina natural. Así que la parte posterior del chip está expuesta. La soldadura de retorno tiene una menor deformación a alta temperatura, inferior a 30 - 50 micras, por lo que está encapsulada como lga sin bola de soldadura (encapsulamiento de matriz de contacto) en lugar de bga (encapsulamiento de matriz de red). La pasta conductora de plata se utiliza para protuberancias, que se imprimen en el sustrato, por lo que ya no se fabrican módulos en la almohadilla. Solo en la almohadilla al del chip no hay níquel ni oro, y no hay proceso de protuberancia de obleas (figura 1 - 3).

Estructura del embalaje FIC - 1

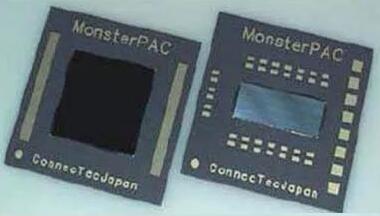

Imagen del embalaje FIC - 2

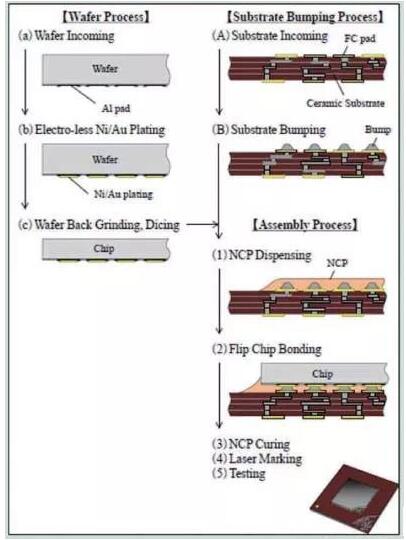

Proceso FIC - 3

Aproximadamente similar a lo anterior, nuestro paquete está compuesto por solo cuatro materiales (chips, protuberancias, cerámica y ncp). Esta estructura simple hace que el embalaje sea pequeño, delgado y ligero.

Hay dos tipos principales de materiales de base cerámicos disponibles: htcc (cerámica Co - quemada a alta temperatura) y ltcc (cerámica Co - quemada a baja temperatura). Las propiedades especiales de la cerámica (como propiedades eléctricas, conductividad térmica, etc y deformación) y la Unión de chips invertidos permiten que nuestros envases cumplan con las mejores soluciones para una variedad de requisitos, desde productos eléctricos hasta chips semiconductores.

La estructura de tipo monsterpac es única

Estos lugares únicos se describen de la siguiente manera:

. adherencia sin daños

. radiación de alto calor

. Baja pérdida de inserción

. alta fiabilidad

Combinando estas principales ventajas, monsterpac tipec ha logrado proporcionar el mejor rendimiento posible para la generación de LSI de 20 nm.

Adhesión sin daños

La tecnología central de nuestro embalaje es la tecnología de Unión de chips invertidos sin daños, que ha logrado una unión sin daños y altamente confiable de chips semiconductores fabricados con mecanizado de precisión de vanguardia.

Los chips semiconductores sin daños se refieren a:

Unión a baja presión

Podemos lograr una presión de Unión de 0.12g / bump, que es 1 / 20 de la presión normal de 2.4G / bump de c4. Al reducir la carga de unión a este límite, se puede evitar el daño del medio intercalar causado por la unión.

Bajo esfuerzo de contracción durante el proceso de solidificación de la superficie convexa

El esfuerzo de contracción durante la solidificación del punto convexo es inferior a 10 Mpa / punto convexo, que es muy pequeño. Al reducir la temperatura, la carga y el esfuerzo de retracción aplicado a la capa intermedia del medio frágil (como almohadillas y líneas de bajo K y al, etc.), se logró con éxito una soldadura invertida de alto rendimiento y confiabilidad, evitando la rotura y grietas de la línea.

A partir de estas ventajas se puede ver que es el único encapsulamiento con una estructura que evita daños en capas k débiles y bajas.

Radiación de alto calor

Consciente de que el calor del Chip Semiconductor es irradiado por el sustrato de encapsulamiento, elegimos el sustrato cerámico en lugar del sustrato orgánico ordinario (la conductividad térmica es de 0,5w / mk), ya que su conductividad térmica es 14 W / MK más alta que la del sustrato orgánico. cuando el tamaño del encapsulamiento es de 21 * 21 mm y se utiliza El sustrato cerámico, el consumo de energía alcanza los 6 w, Es 1,7 veces más potente que un sustrato orgánico con un consumo de energía de 3,6 W.

Una inserción baja te lastimará

Los dispositivos electrónicos requieren un alto nivel de rendimiento en el rango de alta frecuencia. La pérdida de inserción del sustrato cerámico es de 0,42 decibelios (@ 20ghz, L = 5 mm), mientras que la pérdida de inserción del sustrato orgánico es de 0,62 decibelios. Los sustratos cerámicos permiten frecuencias superiores a 10 GHz y los sustratos orgánicos 3 ghz.

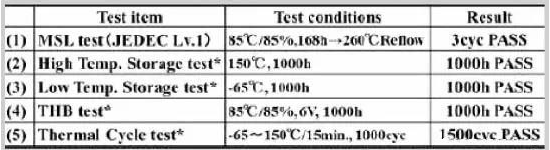

Alta fiabilidad y alta resistencia a la humedad

La resistencia normal de retorno (msl: nivel de humedad) es de nivel 3 (@ 30deg / 60 100% rh192hr). Cada uno de los monsterpac tipec tiene un Chip Semiconductor intacto, y las protuberancias están hechas de materiales no fundidos. Cuando se devuelve a alta temperatura, las protuberancias no se derriten, por lo que no se repite la regentación y la reguración, y el sustrato cerámico no absorbe agua. Así, el nivel MSL de monsterpac tipo C es el nivel 1 (@ 85deg / 85 100% rh192hr), que elimina los envases húmedos y a prueba de humedad sin hornear previamente, y la vida vegetal de monsterpac tipo C es ilimitada.

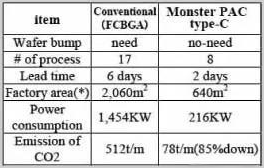

Alta tasa de crecimiento de las plantas

Para facilitar la producción, hemos desarrollado una estructura de protuberancia de gas epoxidado en lugar de soldarla. Por lo tanto, se necesita una gran cantidad de instalaciones de procesamiento de protuberancias de chip, y el costo de una gran cantidad de soldadura can + adyacente al retorno también es necesario. Así, el tamaño plano o superficial del dispositivo puede reducirse en un 69% en comparación con los dispositivos de proceso C4 tradicionales del mismo tamaño y el consumo de energía del dispositivo puede reducirse en un 85%. Se pueden lograr con éxito centrales eléctricas de ahorro de energía y baja carga de fondo.

Capacidad

La singularidad del proceso monsterpac tipec

Protuberancia de la tecnología cerámica

Monsterpac tipec cree que es apropiado usar pasta conductora de plata como material de protuberancia. Las protuberancias se forman en el sustrato cerámico utilizando la tecnología habitual de impresión de piezas SMD de soldadura e impresión (según el caso). No es necesario pretratamiento y limpieza de la superficie del sustrato cerámico antes del tratamiento del punto alto, ni galvanoplastia la superficie después de la formación del punto alto. El fcbga orgánico tradicional requiere protuberancias largas en las almohadillas al de las obleas semiconductoras, como las protuberancias de flujo, au y cu. Sin embargo, las proyecciones basadas en cerámica no requieren este proceso de proyecciones largas de obleas. En cambio, producen ni y au no chapados en chips semiconductores. Los protuberancias basadas en la tecnología cerámica han logrado un proceso de procesamiento simple y bajo costo.

Además, a diferencia de las protuberancias duras (con una dureza de 10 hv) utilizadas en tecnologías de sentido común como los flujos, las protuberancias au y cu, se han desarrollado protuberancias blandas (1hv) para mantener el patrón a baja dureza.

Para el purín conductor suave y convexo que contiene plata, hemos desarrollado puntos fijos relevantes con amplia experiencia en impresión de asfalto de bajo estrés, baja resistencia a la firma y detalles. Hasta ahora, la fuerza de trabajo de los protuberancias que hemos formado es la almohadilla de matriz facial: distancia de 150 angstroms; Almohadillas periféricas: 75 islas de distancia. Sin embargo, las reglas preestablecidas reales tienen en cuenta el espaciamiento de la almohadilla, por lo que el espaciamiento de la matriz superficial de 60 ° m solo se aplica a las protuberancias abiertas.

Adhesión sin daños

Utilizando la tecnología de Unión de chips invertidos blandos, el NCP se utiliza para distribuir las protuberancias blandas formadas por la tecnología de protuberancias cerámicas, y luego unir los chips semiconductores con los chips invertidos. Durante el proceso de unión, la pasta conductora de la protuberancia y el NCP se curan al mismo tiempo. Como resultado, se logró la firma conjunta y la fiabilidad.

La temperatura en las instalaciones de FCB es inferior a 200 grados centígrados, más de 40 grados centígrados por debajo de la tecnología normal de unión. La presión de unión es inferior a 0,12g / dot, que es 1 / 20 de la tecnología de unión ordinaria. A través de estas uniones térmicas de baja temperatura y baja presión, los chips semiconductores no se ven afectados por el estrés y las fuerzas externas durante el proceso de curado después de la Unión y la unión. con el lodo conductor recién desarrollado y el ncp, se logró con éxito un control de teclas de alta velocidad inferior a 1,0 segundos. El NCP incluye suplementos que normalmente se encuentran a ambos lados de la almohadilla del CHIP y las protuberancias. Sin embargo, es común voltear las teclas del chip a baja presión. El complemento está enterrado en la protuberancia, por lo que no afecta a la firma entre la almohadilla del CHIP y la protuberancia. Esta es una de las ventajas de los baches blandos. Después de la distribución del NCP antes de la soldadura invertida, el NCP se complementa fácilmente entre los protuberancias y las brechas estrechas, y se utilizan teclas de baja carga, sin alineación entre el chip y el sustrato. Por lo tanto, esta técnica de unión es adecuada para intervalos estrechos de almohadillas.

El problema con la técnica de unión común es que, en el caso de la Unión de chips invertidos con protuberancias de soldadura, durante la fusión del flujo hasta el curado, se aplica una tensión de retracción muy elevada (unos 200 - 500 MPa / protuberancias) a las protuberancias del Chip Semiconductor y a las almohadillas al. sin embargo, La técnica de Unión de bajo estrés ha tenido éxito, ya que el bajo módulo de elasticidad de los materiales convexos no fundidos requiere un esfuerzo de rebote muy pequeño (menos de 10 Mpa / convexo).

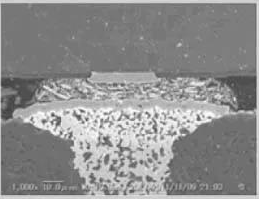

Es precisamente debido al proceso de desarrollo de estas tecnologías básicas mencionadas anteriormente que el éxito de la soldadura invertida no se ha dañado. La figura 4 es un punto clave del chip invertido y un perfil de la contrafirma.

Foto - 4 apariencia y sección

Fiabilidad del embalaje

El TC probó el contorno de la protuberancia trasera, pero no probó ni midió las grietas y la descalentación que pudiera causar el acoplamiento de la fractura.

APIC (dispositivo de aplicación ic)

El procesamiento APIC de hoy se está moviendo hacia el uso de materiales de baja K para el mecanizado de precisión, lo que requiere tolerancia de alta temperatura y alta velocidad. El monsterpac tipec tiene las siguientes ventajas para cumplir con estos requisitos.

. adherencia sin daños

. radiación de alto calor

Cuando hay alta velocidad

Algunos clientes de APIC están evaluando la producción a escala de monsterpac tipo C

PAC tipo C

Como resultado de la evaluación real entre el orgánico fcbga y el monterpac tipo C en las mismas condiciones (la misma falda, el mismo chip y la misma distancia entre almohadillas), la temperatura del monterpac tipo C TJ es 10 grados centígrados inferior a la temperatura del paquete orgánico. Después de una comparación muy precisa de tj, la diferencia será de unos 20 grados centígrados.

Tablero de radiofrecuencia (tablero de radiofrecuencia):

En la actualidad, para la comunicación de alta velocidad lsi, el embalaje de la placa se está mejorando constantemente. Estas secciones requieren las siguientes características especiales:

. adecuado para alta velocidad y alta frecuencia

Tamaño pequeño

Para aplicaciones de alta velocidad y alta frecuencia, como se mencionó anteriormente, si es apropiado, el uso de un sustrato cerámico puede aumentar la pérdida de inserción y puede usarse en 10 ghz.

Además, los multichips y un gran número de componentes SMD se pueden utilizar para encapsulamientos pequeños, ya que se pueden unir con chips invertidos pequeños y espaciados entre detalles.

Trabajar con los clientes para desarrollar muestras de placas de radiofrecuencia, cuyo rendimiento ha sido reconocido por los clientes y se está preparando para la producción a gran escala.

Módulo de radiofrecuencia

Para estas carcasas de placas, la humedad del sustrato es muy estrecha. El MSL del monsterpac tipec es de nivel 1, por lo que no existe asfixia por humedad.

Se puede ver que el monsterpac tipo C es el más adecuado para el encapsulamiento plano, y el encapsulamiento orgánico tradicional SMD y chips invertidos requieren múltiples soldadura de retorno.

Juez

Para la próxima generación de procesos de 20 nm, es necesario encapsular para adaptarse a una mayor radiación térmica y una mayor velocidad. Sin embargo, la tecnología de embalaje de sentido común es difícil de cumplir con estos requisitos. Por lo tanto, es necesario desarrollar una nueva tecnología de encapsulamiento adecuada para el proceso de 20 nm.

Nuestro monsterpac tipec es adecuado para el próximo proceso de 20 nm y maximiza el rendimiento del lsi. Su alto rendimiento es como un producto increíble y extraño. El monsterpac que desarrollamos desactualiza el C4 y se convierte en la principal tecnología de la próxima generación de semiconductores en el futuro.

Desarrollo tecnológico para la próxima generación

Investigación y desarrollo de nuevos sustratos cerámicos

El desarrollo de la tecnología de sustratos cerámicos siempre ha sido brillante. Hasta ahora, los dibujos precisos y detallados de alta densidad se han quedado muy por detrás de los sustratos IC orgánicos.

Para resolver este problema y avanzar, comenzamos a desarrollar un sustrato cerámico de precisión con alta densidad sin afectar el costo. Nuestro objetivo es un espaciamiento de líneas de 20 ° M para lograr la precisión adecuada y el uso de gráficos detallados más flexibles. por defecto, el espaciamiento de agujeros también requiere mayor precisión y detalle, con un objetivo de 50 ° m.

Hasta la fecha, los sustratos cerámicos se han fabricado utilizando estampado e impresión de máscaras (según el caso). Estas técnicas existentes se limitan a dibujos precisos y detallados. Estamos considerando reemplazarlos por procesos láser e impresión directa. La implementación de esta tecnología proporcionará un mejor rendimiento que el sustrato orgánico. Hasta ahora, los sustratos cerámicos se utilizaban comúnmente en productos de alta gama, pero este nuevo sustrato estará dirigido a bienes de consumo. Es cierto que los sustratos requieren bienes de consumo de alto rendimiento para crecer por sí mismos.

Esta combinación de sustrato con la tecnología monsterpac proporcionará al mundo la mejor placa de circuito impreso (pcb) de rendimiento y alta fiabilidad.